全志R128硬件设计指南①

原理图设计

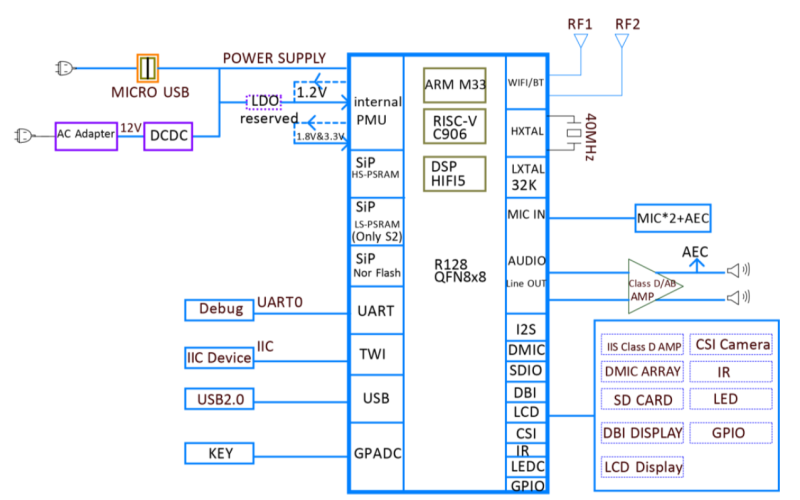

硬件系统框图

R128是一颗专为“音视频解码”而打造的全新高集成度 SoC,主要应用于智能物联和专用语音交互处理解决方案。

- 单片集成 MCU+RISCV+DSP+CODEC+WIFI/BT+PMU,提供生态配套成熟、完善的用于系统、应用和网络连接开发的高效算力;

- 集成 8MB/16MB/32MB PSRAM,为音视频解码、大容量存储、扫码以及网络连接提供充裕的高容量、高带宽的内存支持;

- 拥有丰富的音频接口 IIS/PCM、OWA、DMIC、LINEOUT、MICIN 以及通用通讯接口 IIC、UART、SDIO、 SPI、ISO7816卡接口;同时支持 U 盘、SD卡、IR-TX/RX;

- 内置 LDO、GPADC、LEDC,简化系统方案设计,降低 BOM成本。

硬件系统基本工作原理

R128硬件系统基本工作流程如下:

- 硬件系统正常上电,主控复位之后,CPU开始执行 BROM固化代码,对系统资源和关键外设进行配置及初始化,包括电源,时钟,总线,复位,存储接口等。

- 根据配置,在 BROM阶段将系统初始化信息(串口、PSRAM等)从存储介质读取到系统 SRAM,进行芯片及系统的进一步详细配置和初始化工作;执行完 Boot0 程序后进入 boot 阶段。

- 从外部存储介质中读取下一阶段需要的软件代码,启动操作系统,并对系统资源和外设进行管理。

- 操作系统启动之后,根据产品不同需求加载相关启动,比如 USB、音频、WIFI、显示、蓝牙等模块,最终完成开机启动,进入普通操作界面。

- 系统支持 watchdog 应用监视系统的运行,当程序跑飞或者发生死循环时,watchdog模块会发出一个复位信号,使 SOC复位,软件系统重新启动。

R128硬件系统组成如下表:

| 系统 | 说明 |

|---|---|

| CPU小系统 | 时钟,复位,中断,系统配置 |

| 存储系统 | PSRAM,SPI NAND/SPI NOR/EMMC/SD CARD |

| 音频系统 | MIC IN、FMIN、IIS/PCM/TDM、DMIC、LINEOUT |

| 输入输出子系统 | RGB、SD CARD、USB OTG/HOST、TWI、UART、PWM、GPADC、TPADC、CSI、 IR TX/RX 等 |

| 电源系统 | DCDC、LDO |

| 无线 | WIFI/BT |

| 其他 | 功放、LED |

CPU小系统

R128 CPU小系统包括时钟系统,系统配置 PIN、复位系统和 Debug 部分。

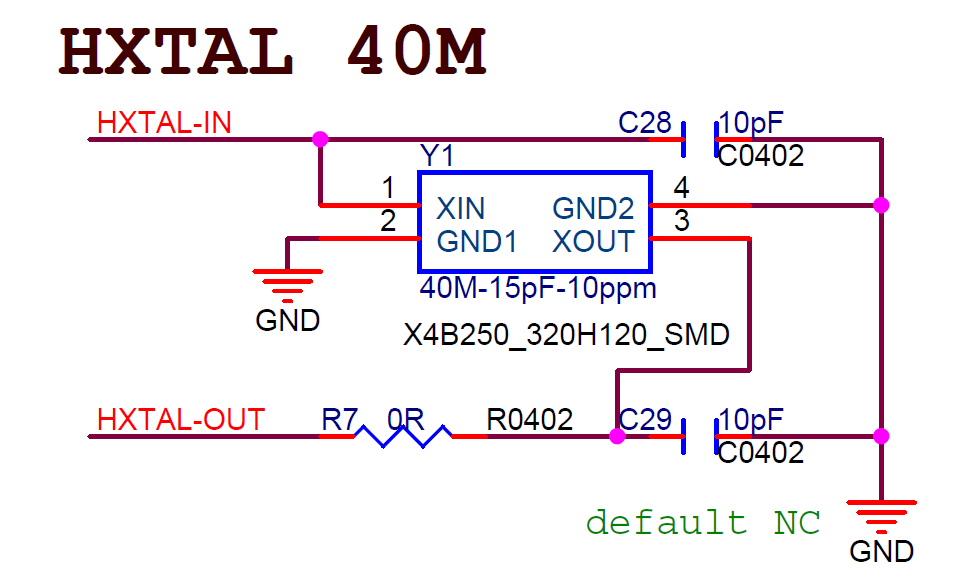

时钟系统信号PIN说明

R128 硬件系统包含 DCXO 40M/RTC 32.768K 两个时钟,对应时钟信号说明如表所示。

| 信号名 | 信号描述 | 应用说明 |

|---|---|---|

| HXTAL_IN | DCXO晶振输入 | 默认使用 40M晶振,频率误差为 10PPM; |

| HXTAL_OUT | DCXO晶振输出 | 默认使用 40M晶振,频率误差为 10PPM; |

| LXTAL_IN | 32K晶振输入 | 32.768K晶振电路,频率误差为 20PPM |

| LXTAL_OUT | 32K晶振输出 | 32.768K晶振电路,频率误差为 20PPM |

RTC 32.768K时钟可以从内部 RC振荡电路产生,可不使用外部 32K晶振。

小系统配置说明

R128小系统配置 PIN说明如表所示。

| 信号名 | 信号说明 | 应用说明 |

|---|---|---|

| RESET | system reset | 1,系统复位 PIN 2,Watchdog 输出 PIN |

| CHIP-PWD | Chip power down/System reset | 1,内部 PMU 下电控制 pin; 2,系统复位 pin |

| PA1/FEL0 | FEL功能选择 pin 0 | 当[FEL0,FEL1]= 00时,SOC进入 FEL升级状态 |

| PA2/FEL1 | FEL功能选择 pin 1 | 当[FEL0,FEL1]= 00时,SOC进入 FEL升级状态 |

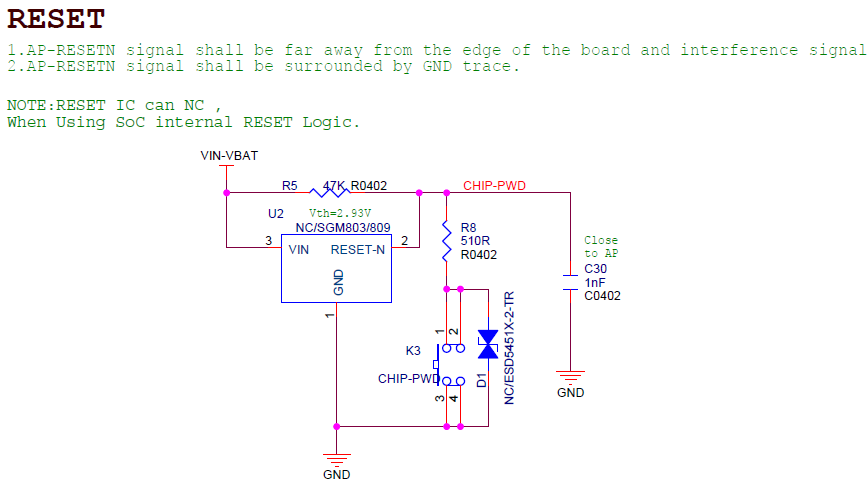

- RESET和 CHIP-PWD均可实现系统复位功能,但 CHIP-PWD包含 R128内部 PMU掉电控制功能,可让R128实现上电复位功能。

- RESET/CHIP-PWD信号上接下地电容默认为 1nF,用于滤波和增强 ESD 防护能力

- 为避免 SOC启动时误进入升级状态,PA1/FEL0和 PA2/FEL1 不能同时接下拉电阻。

主晶振电路

- R128 DCXO模块推荐使用 40M 晶振以获得更好的射频性能。

- 晶振选型参考如下:

- R128集成 WIFI/BT功能,为获得更好的射频性能,建议晶振选型频率容限与频率稳定性均≤ 10ppm

- 晶体负载电容指标 CL,建议 CL≥10pF。CL过小会导致晶体温飘过大

- 晶体驱动能力 DL,建议典型值 100uW,最大不超过 200uW。取值过小会影响晶体寿命。

- 外挂匹配电容大小根据晶振规格和 PCB而定,要求匹配电容+板级杂散电容总值等于晶振规格要求的负载电容大小。

- 串接电阻需要预留位置,便于调试振荡幅度处理 EMI 问题。

晶振参数不得随意更改,需保证晶体自身负载电容、外挂匹配电容、PCB走线负载电容三者匹配。

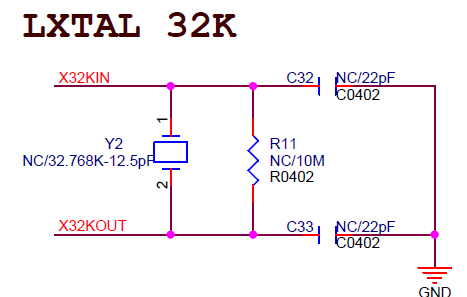

32.768K时钟电路

- 支持内部 RCOSC时钟,支持 HOSC校准,满足 32.768K时钟输出。

- 外挂 32.768K 晶振时,外挂匹配电容大小根据晶振规格和 PCB而定,要求匹配电容+板级杂散电容总值等于晶振规格要求的负载电容大小。

- LXTAL_IN/LXTAL_OUT 之间并接的电阻,必须保留,用于对频率微调。

晶振参数不得随意更改,需保证晶体自身负载电容、外挂匹配电容、PCB走线负载电容三者匹配。

复位电路设计

R128可以选择使用外部复位 IC提供复位信号,也可以使用内部复位源。

- 内部上电复位触发门槛:VBAT爬升至约 2.4V;

- 内部下电复位触发门槛:VBAT跌落至 3.0V/2.9V/2.8V/2.7V/2.6V/2.5V(软件可配置),详见 R128用户手册;

- 使用外部复位 IC 复位,时长不得低于 64ms;

- RESET Pin放置 1nF电容。

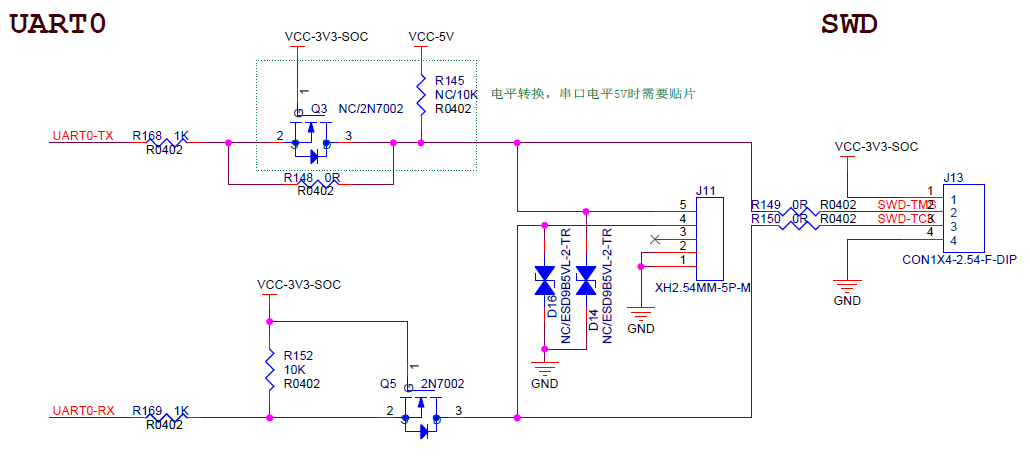

DEBUG电路设计

R128支持 USB(OTG)、UART、JTAG与 SWD 等多种调试方式,客户可根据需要选择合适的调试方式,建议在设计时对相应的调试接口预留测试点方便后续调试验证。

电源系统设计

SOC端电源质量要求

R128集成 PMU,外部仅需提供 VBAT 电源即可满足 R128 电源应用需求,其他电源由内部 PMU 产生。

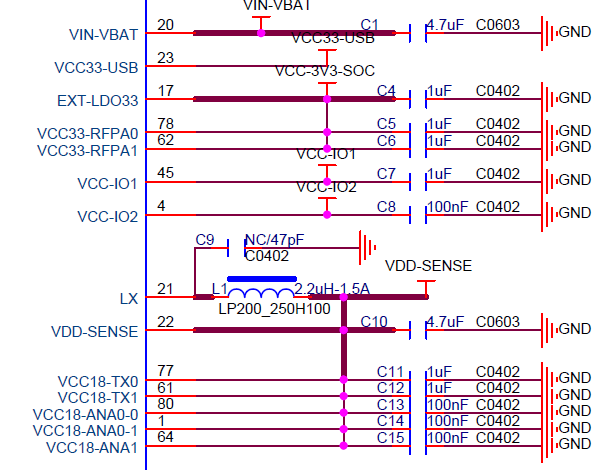

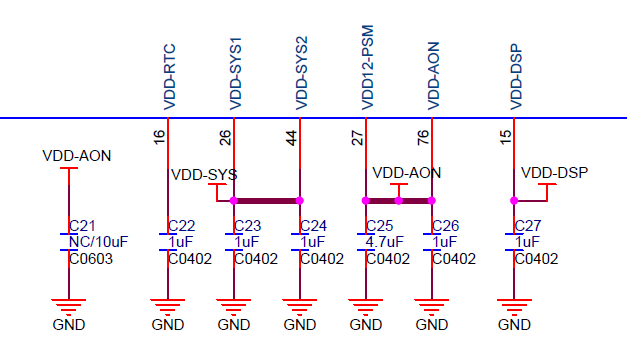

SOC端电源电容设计

R128 SOC端各电源要求滤波电容容值如下:

- VDD_LX管脚建议预留放置 1个 2.2uF电容;

-

VDD_SENSE管脚建议放置 1个 4.7uF电容;

-

VDD_CLK、VDD18_ANA1、VDD18_TX1、VDD18_ANA2、VDD18_TX2电源 pin建议各放置 1个 100nF电容,靠近管脚放置;

- VDD_DSP建议放置 1个 1uF电容,靠近管脚放置;

-

VDD_RTC建议放置 1个 1uF电容,靠近管脚放置;

-

VDD_SYS1、VDD_SYS2建议各放置 1 个 1uF电容,靠近管脚放置;

-

VDD_AON建议放置 1个 1uF电容,VDD12_PSM 建议放置 1 个 100nF 电容,靠近管脚放置;

-

VDD_3V3建议放置 1个 1uF电容, VDD33_LB1、VDD33_LB2 建议各放置 1 个 100nF 电容,靠近管脚放置;

- VDD_IO1、VDD_IO2、VDD_IO_5VTOL建议各放置 1 个 100nF 电容,靠近管脚放置;

- AVDD电源与 AGND之间至少 1个 2.2uF电容,靠近引脚放置。

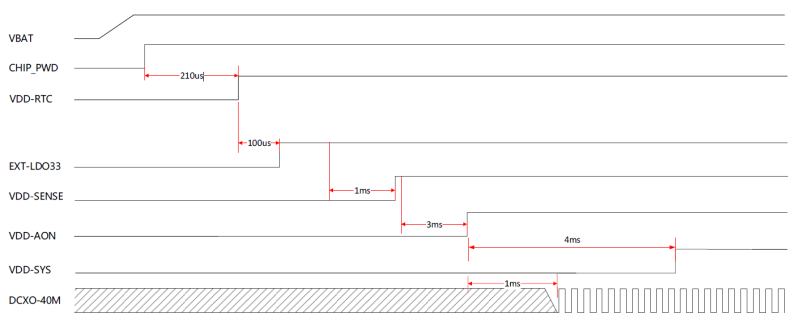

上电时序设计

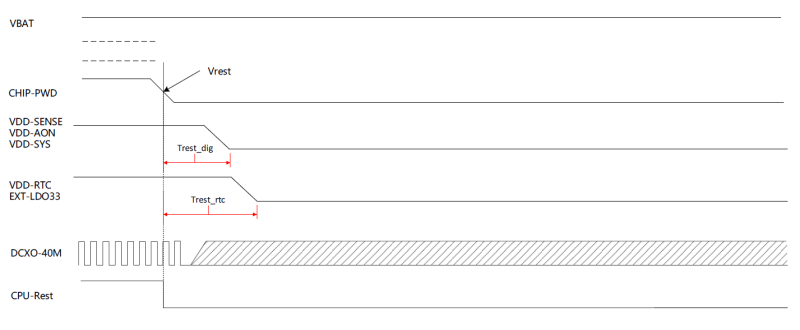

R128各模块供电采用内部 PMU,其上电时序如图所示,时序描述如下:

- VBAT为 SOC外部电源输入,其上电至 2.4V附近触发内部 POR复位;

- 完成 POR 复位后,PMU各路 DCDC、LDO按照下图所示时序进行上电;

当使用外部 DCDC 或 LDO为 R128 的 VDD_IO1、VDD_IO2和 VDD_IO_5VTOL进行供电时,为避免电源从 IO漏电导致 SOC启动失败,建议使用 EXT_LDO(pin VDD_3V3)对外部 DCDC或 LDO 进行时序控制。

下电时序设计

R128下电时序如图所示,时序描述如下:

- R128内部集成掉电复位功能,通过检测 VBAT电压触发复位,可软件使能掉电复位功能和配置门槛电压,详见 R128 用户手册描述;

- 复位信号拉低后,DXCO、RCOSC停止振荡,各路 DCDC、LDO停止输出。

PSRAM 电路设计

R128内置 PSRAM,无需外部电路,只需满足 R128 电源设计要求即可。

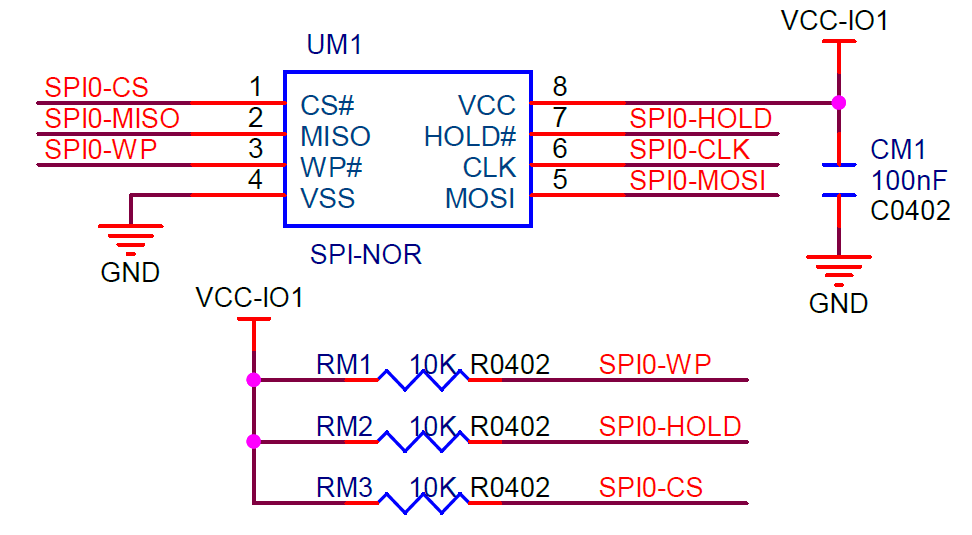

Flash 电路设计

R128支持合封 SPI Nor FLSAH,支持外挂 SPI Nand/Nor、eMMC,设计说明如下:

- 使用合封 SPI Nor FLASH 时,VDD-IO1必须使用 3.3V电源;

- 使用外挂 SPI Nand/Nor、eMMC 器件时,可选择从 PA24-PA29、PB4-PB7&PB14/15、PA2-PA7 三个地方启动;

- 启动介质选择支持 Try 与 eFuse Select 两种方式;

- Try 方式启动顺序为 SDC0->SPI NOR->SPI NAND->EMMC,该模式仅支持轮询 PA 口的启动介质

- eFuse Select方式启动顺序由 eFuse决定,具体启动顺序及烧码值可定制

SPI NOR/NAND 参考设计

GPIO 电路设计

R128 有PA/PB 2 组GPIO,GPIO 逻辑电平与供电电压有关。

- 未使用的GPIO 优先建议接地或者Floating,软件设定为disabled 状态;

- IO 上拉电阻上拉电压选择IO 所在电源域。

| GPIO 分组 | 控制器电源域 | IO电源域 | IO电压 |

|---|---|---|---|

| PA0~PA14 | VDD-SYS | VDD-IO2 | 3.3V/1.8V |

| PA18~PA23 | VDD-SYS | VDD-IO2 | 3.3V/1.8V |

| PA16~PA17 | VDD-SYS | VDD-IO-5VTOL | 5V/3.3V/1.8V |

| PA15 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

| PA24~PA29 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

| PB0~PB15 | VDD-SYS | VDD-IO1 | 3.3V/1.8V |

LED电路设计

R128集成 LEDC功能,可以直接驱动集成式 LED。

集成式 LED一般供电范围是 3.5~5.3V,Vih必须大于 0.7*VDD,如 WS2812C。当 VDD为 5V供电时,Vih必须大于 3.5V,已超出 SOC IO输出电压范围。解决方案:

- 5V供电串联 1N4148二极管,降低 VDD电压,理论 VDD电压为 4.3V,此时 Vih 大于 3V 即可;

- 市场已有 5V 供电且支持 3.3V逻辑控制的集成式 LED,如 WS2128B-V4/V5。

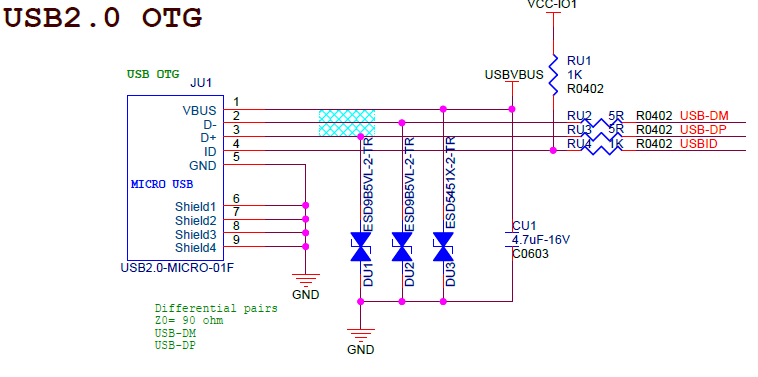

USB电路设计

R128 USB接口具有 HOST和 OTG功能,在产品功能定义上需要注意区别。

- 若使用 Micro USB 供电,建议在 VBUS上放置限流和防倒灌 IC、TVS 保护器件;

- USB-ID 信号为 OTG 检测信号,上拉电压选择 USB-ID Pin所在电源域;

- USB-ID 信号到 SOC端的 GPIO 串接 1K~1.5K电阻提升 ESD性能;

- 建议在 VBUS 上放置稳压管和 TVS保护器件;

- D+/D-信号线为高速信号线,并接的 TVS 要求低容值,否则影响数据传输,以小于 4pF 为宜;串接预留 5 电阻。

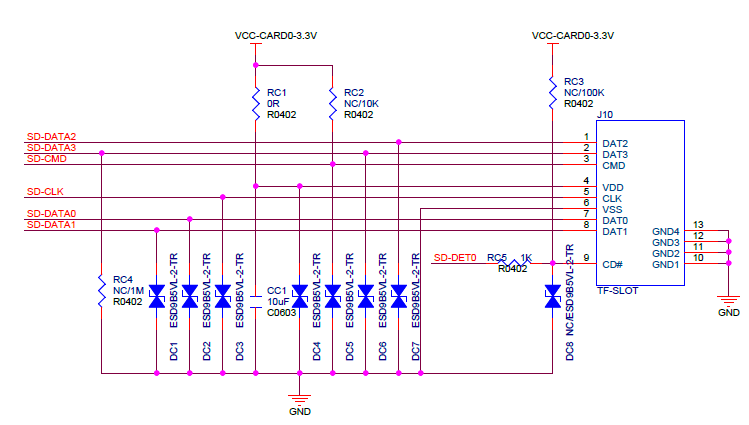

SD Card 电路设计

- SDC0-CLK串接 33R电阻,靠近 SoC摆放;

- SDC0-CMD和 SDC0-DET Pin芯片内部集成 15K上拉电阻,外部 10K上拉默认 NC;

- SDC0-DET串接 1K电阻,减缓信号下冲和提供 IO ESD能力;

- 靠近 SD 卡座,每个信号 Pin放置 ESD器件。

- SD卡座电源 VDD预留串联 0R电阻,防止卡插入时,瞬间大电流烧卡。

音频电路设计

- 3个 ADC,可支持 3 个差分 MIC 输入;

- 2个 DAC,R128-S1/S2可支持差分立体声输出,R128-S3可支持单声道差分音频输出;

- 支持 1 套 I2S/PCM 接口,支持 TDM模式,支持主从模式;

- 支持 OWA 输出,兼容 SPDIF 协议;

- 支持 DMIC 8 声道输入。

音频设计建议如下:

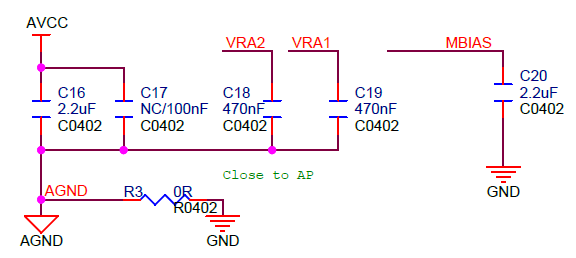

- AVDD对地电容为 2.2uF;VRA1对地电容为 470nF;VRA2对地电容为 470nF;MBIAS对地电容为 2.2uF;

- AVDD/VRA1/VRA2的 AGND通过 0R电阻单点到 GND;

- MIC1-3建议组合成 2MIC+1AEC 电路;

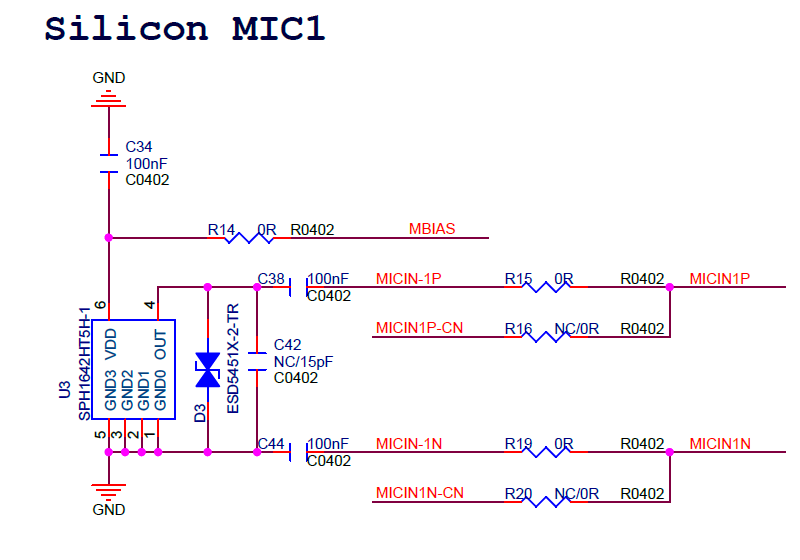

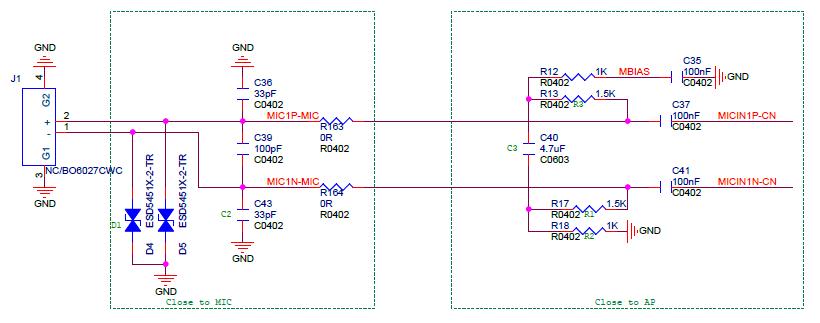

MIC和 AEC参考设计如图所示。AEC 回路电阻电容参数与功放输出幅度和算法公司要求有关,参数以实际开发环境为准。

硅MIC参考电路

驻极体MIC参考电路

ADC电路设计

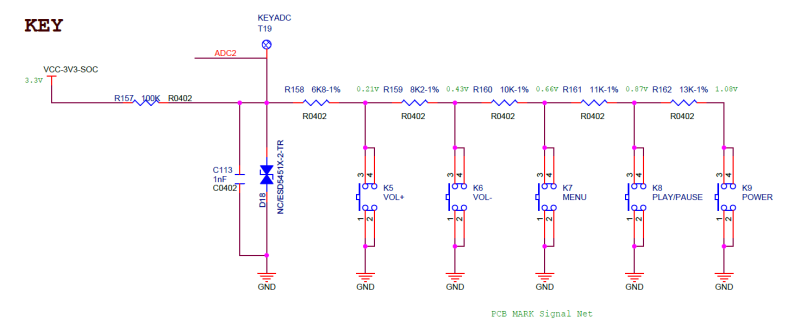

支持 1 路 GPADC 接口,12bit采样分辨率,9bit采样精度,单通道最高采样率为 1MHz,最大支持 8 通道,可以用作按键功能或采集电池电压使用。

- GPADC 量程范围为 0~2.5V,应用时建议使用 0.2~2.3V作为输入检测电平;

- 按键按键分压电阻,请使用推荐的阻值,如 5 个按键以下,推荐使用 1%精度电阻。添加按键时保证按键按下后,ADC网络电压范围为 0~1.08V,最小间隔大于 200mV。

LCD电路接口

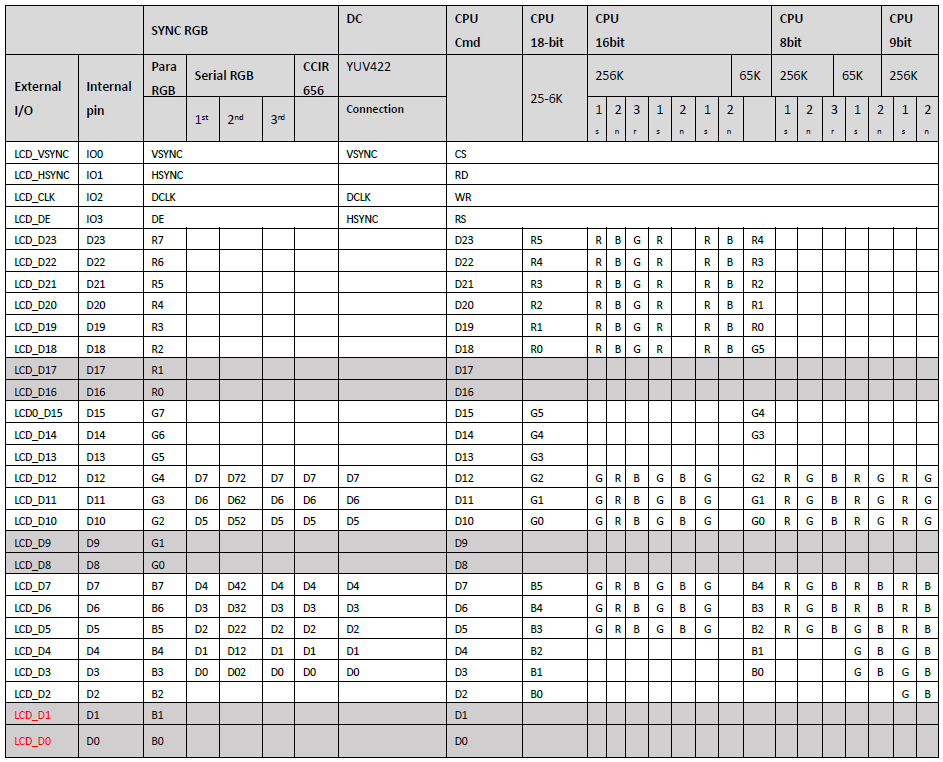

R128 支持一路 RGB屏接口和一路 SPI屏接口。其中 RGB屏接口可支持并行 RGB666 模式(1024x768@60fps)、串行 RGB模式(800x480@60fps)和 i8080模式(800x480@60fps),各种模式下管脚功能描述如下表。

SPI屏支持以下几种模式:

| 3 线 1 DATA | 3 线 2 DATA | 4线1 DATA | 4线2 DATA | 2 DATA Lane |

|---|---|---|---|---|

| DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX |

| / | / | DBI-DCX | DBI-DCX | / |

| DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK |

| DBI-SDA | DBI-SDO | DBI-SDA | DBI-SDO | DBI-SDA |

| / | DBI-SDI | / | DBI-SDI | WRX |

| DBI-TE | DBI-TE | DBI-TE | DBI-TE | DBI-TE |

DBI接口与SPI1复用关系

| SPI | DBI |

|---|---|

| SPI1-CS | DBI-CSX |

| SPI1-CLK | DBI-SCLK |

| SPI1-MOSI | DBI-SDO/SDA |

| SPI1-MISO | DBI-SDI(WRX)/TE/DC X |

| SPI1-HOLD | DBI-DCX/WRX |

| SPI1-WP | DBI-TE |

CSI电路接口

| PIN脚 | CSI接口 | 说明 | DVP |

|---|---|---|---|

| PA18/PB0 | NCSI0-HSYNC | 摄像头行同步 | HSYNC |

| PA19/PB1 | NCSI0-VSYNC | 摄像头场同步 | VSYNC |

| PA20/PB14 | NCSI0-PCLK | 摄像头像素时钟 | PCLK |

| PA21/PB15 | NCSI0-MCLK | 摄像头主时钟 | MCLK |

| PA22 | NCSI0-D0 | Parallel CSI Data | Y2 |

| PA23 | NCSI0-D1 | Parallel CSI Data | Y3 |

| PA27 | NCSI0-D2 | Parallel CSI Data | Y4 |

| PA26 | NCSI0-D3 | Parallel CSI Data | Y5 |

| PA29 | NCSI0-D4 | Parallel CSI Data | Y6 |

| PA25 | NCSI0-D5 | Parallel CSI Data | Y7 |

| PA24 | NCSI0-D6 | Parallel CSI Data | Y8 |

| PA28 | NCSI0-D7 | Parallel CSI Data | Y9 |

射频端口设计

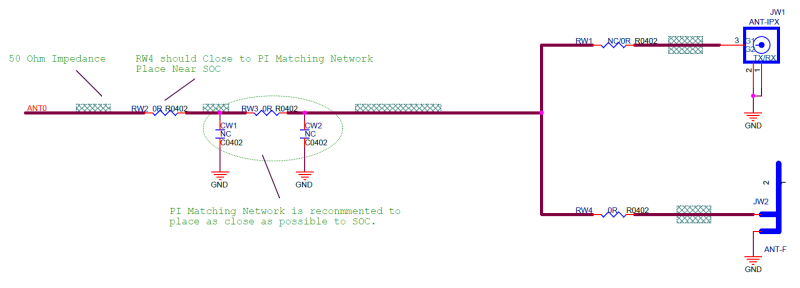

射频输出端口(ANT pin)无需匹配电路,但可预留天线 PI 型匹配电路。如上图所示。为了方便天线PI型匹配电路调试,需在射频输出端口与天线间预留 0Ω电阻 WR1。如图所示。

因 R128 芯片射频前端已设计滤波器用于射频认证时滤除谐波杂散,因此,硬件方案端只需要预留一个PI型匹配电路用于匹配天线,无需额外多预留一个 PI型滤波网络用于滤除谐波杂散。

原理图设计其他

- I2C/TWI 最大支持 400Kbit/s 的传输速率,总线上加上拉电阻,推荐值为 2.0K~4.7K,上拉电源为对应 GPIO电源域,各设备地址不得有冲突;

- GPIO分配时,请确保电平相匹配,上拉的电压域必须为此 GPIO的电源域,以防外设向 SOC漏电情况发生;

- 串口调试电路 TX/RX 信号要加防倒灌电/隔离保护电路。可以选择 MOS管或二极管方案,二极管方案必须选择肖特基二极管。加工生产时为节约成本,MOS管和二极管隔离保护电路可以 NC,但板级至少要串接 100Ω电阻。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Java8新特性——函数式接口

- 【愚公系列】软考中级-软件设计师 017-数据结构(树和二叉树概念)

- 杂题——试题-算法训练-P0802-字符串表达式求解

- 2023年去世21位亿万富豪;蔚来手机负责人尹水军将离职;特斯拉召回超161万辆电动车;家乐福在欧洲四国“封杀”百事

- [leetcode] 四数之和 M

- 现场EMC电磁干扰排查、监测、EMC整改

- R语言【base】——do.call():根据名称或函数以及要传递给它的参数列表构造并执行函数调用

- Apache安装遇到的问题踩坑

- 【漏洞复现】Hikvision SPON IP网络对讲广播系统命令执行漏洞(CVE-2023-6895)

- C语言实现学生成绩管理系统(单链表)