vivado 错误路径

错误路径

假路径是指拓扑上存在于设计中的路径,但有以下两种情况之一:(1)不起作用;或(2)不需要定时。因此,在定时期间应忽略错误路径分析。

错误路径的示例包括:

?添加了双同步器逻辑的时钟域交叉

?通电时可能写入一次的寄存器

?重置或测试逻辑

?忽略异步分布式的写入和异步读取时钟之间的路径RAM(如适用)

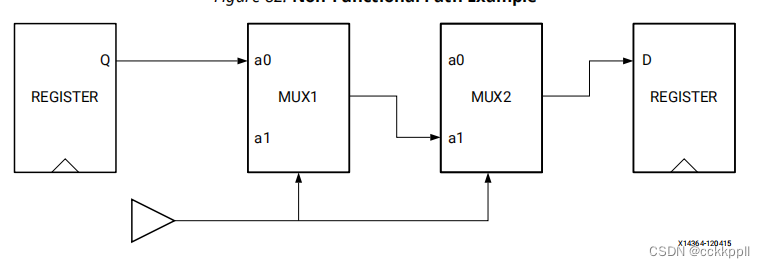

下图显示了一个非功能路径的示例。因为两个多路复用器都是由相同的选择信号驱动,从Q到D的路径不存在,应定义为错误路径。

从时序分析中删除错误路径的原因包括:

?减少运行时间:当从时序分析中删除错误路径时,该工具不需要对那些非功能路径进行计时或优化。具有非功能路径对定时和优化引擎可见可能导致大的运行时损失。

?提高结果质量(QOR):消除错误路径可以大大提高结果(QOR)。综合、放置和优化设计的质量大大提高受到工具试图解决的时间问题的影响。

如果某些非功能路径存在时间冲突,该工具可能会尝试修复这些路径而不是在真正的功能路径上工作。不仅设计可能不必要增加了大小(如逻辑克隆),但该工具可能会跳过修复实际问题,因为非功能路径具有更大的违规行为,会掩盖其他实际违规行为。最佳结果总是通过一组现实的约束来实现。

错误路径是使用XDC命令set_False_path在工具内部定义的:

可以对命令使用以下附加选项来微调路径规范。

有关所有支持的命令行选项的详细信息,请参阅Vivado Design SuiteTcl命令参考指南(UG835)。

?-from选项的节点列表应该是有效起点的列表。有效的起点是时钟对象、顺序元件的时钟引脚或输入(或输出)主端口。多个可以提供元件。

?-to选项的节点列表应该是有效端点的列表。有效的终结点是时钟对象、输出(或inout)主端口或顺序元件输入数据引脚。倍数可以提供元件。

?直通选项的节点列表应该是有效引脚、端口或网络的列表。可以提供多个元件。

through选项的顺序很重要。请参阅以下示例。例如以下两个命令不同:

以下示例删除了从重置端口到所有寄存器的定时路径:

以下示例禁用两个异步时钟域之间的定时路径(用于例如从时钟CLKA到时钟CLKB):

前面的例子禁用了从时钟CLKA到时钟CLKB的路径。来自时钟CLKB的路径至时钟CLKA不被禁用。因此,禁用两个时钟之间的所有路径任一方向上的域都需要两个set_false_path命令:

在图81所示的非功能路径示例中,可以使用-through选项,而不是使用-from或-to选项。见图82。

这确保了无需选择通过上述路径的所有路径以查找起点和终点的特定模式。

set_false_path -through [get_pins MUX1/a0] -through [get_pins MUX2/a1]

另一个常见的例子是异步双端口分布式RAM。文字操作与时钟RAM同步,但读取操作可以是异步的在设计允许的情况下。在这种情况下,可以安全地将写入和读取时钟。

有两种方法可以做到这一点:

?定义从RAM之前的写入寄存器到RAM之后的寄存器的错误路径接收所述读取时钟:

关于Vivado Design Suite示例项目WAVEGen(HDL):

?定义从RAM引脚WE开始的错误路径

关于Vivado Design Suite示例项目WAVEGen(HDL):

下图说明了WAVE(HDL)中分布式RAM的驱动方式示例项目。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 抖音、小红书、视频号是如何判定是否限流的?

- Spring中的工厂类ApplicationContext和BeanFactory

- 【活动回顾】ABeam 德硕 | 企业座谈及宣讲会--石河子大学专场

- 工业控制系统:HSLCommunication可以与DCS(分布式控制系统)进行通信详解:C# HSLCommunication可以与 DCS通信demo

- Python to_numeric函数参数解读与最佳实践!

- 智能化安防与监控:全球发展、挑战与未来趋势

- DTO与VO

- presto/trino 入门介绍实战

- Windterm使用总结

- 哪个牌子的护眼台灯适合学生考研?五款护眼台灯推荐