中央处理器CPU(2)---流水CPU与RISC

?1.流水CPU

(一看到这个就想起老家的流水席了,不知道各位吃过没。)

🌈1.1并行处理技术

对于计算机来说不论如何发展,最重要的一个追求目标就是很高的运算速度,冯诺依曼机是,现代计算机依然是,所以就不得不提及并行处理技术。

早期冯诺依曼机采用串行处理,即任意时刻只能进行一个操作,并行是使得以上各个操作能同时进行,从而大大提高计算机的运行速度。

并行的两种含义:

- 1)同时性:两个以上事物在同一时刻发生。

- 2)并发性:两个以上事物在同一时间间隔内发生。

所以并行有三种形式:空间并行,时间并行,时空并行

- 时间并行:让多个处理过程在时间上相互错开,轮流重叠的使用同一设备的各个部分,以加快硬件周转而赢得速度。

- 空间并行:是指在计算或处理过程中,同时使用多个处理单元或资源来执行并行计算或处理任务的能力。它是一种并行计算的形式,其中不同的处理单元同时处理不同的数据或任务,以提高计算或处理的效率和性能。

- 时空并行:指时间和资源重复的综合应用,同时利用上面两种,达到性能上的最高利用率。(这种技术的高速效益最好。)

而流水线CPU的设计就是根据上面的观点来设计的。

🌈1.2流水线CPU概念?

流水线CPU(Pipeline CPU)是一种计算机中央处理器(CPU)的设计和实现方式,旨在提高指令执行的效率和吞吐量。它将指令执行过程划分为多个阶段,并允许在同一时钟周期内同时执行多个指令的不同阶段。

例如去洗车我发现洗车流程是这样的:喷水、打泡沫、刷洗、擦拭、吹干。

(此图是我在隔壁某乎上借鉴的,比较形象)。

就这样一个工序完成后,车辆向下一个工序移动,当前工序又补进来一辆车。

同理流水线CPU就是按照这个思路来做事!!!

- 在流水线CPU中,指令执行过程被划分为多个独立的阶段,通常包括取指(Instruction Fetch)、译码(Instruction Decode)、执行(Execution)、访存(Memory Access)和写回(Write Back)等阶段。每个阶段负责完成特定的操作,而不同的指令则依次经过这些阶段进行处理。

- 流水线CPU中的每个阶段都有自己的专用硬件单元,这些单元可以并行地执行不同的指令。当一条指令进入流水线后,该指令的不同阶段会依次占用不同的硬件单元,形成一个流水线流程。这样,多条指令可以同时处于不同的阶段,从而提高指令执行的并行性和效率。

- 通过流水线技术,CPU可以在同一时钟周期内同时处理多条指令的不同阶段,从而实现指令级并行和提高吞吐量。

🌈1.3流水CPU的时空图

对于流水CPU,只需拿出三张图就可以让你对他爱的更深!

🌈1.4流水CPU的四个过程

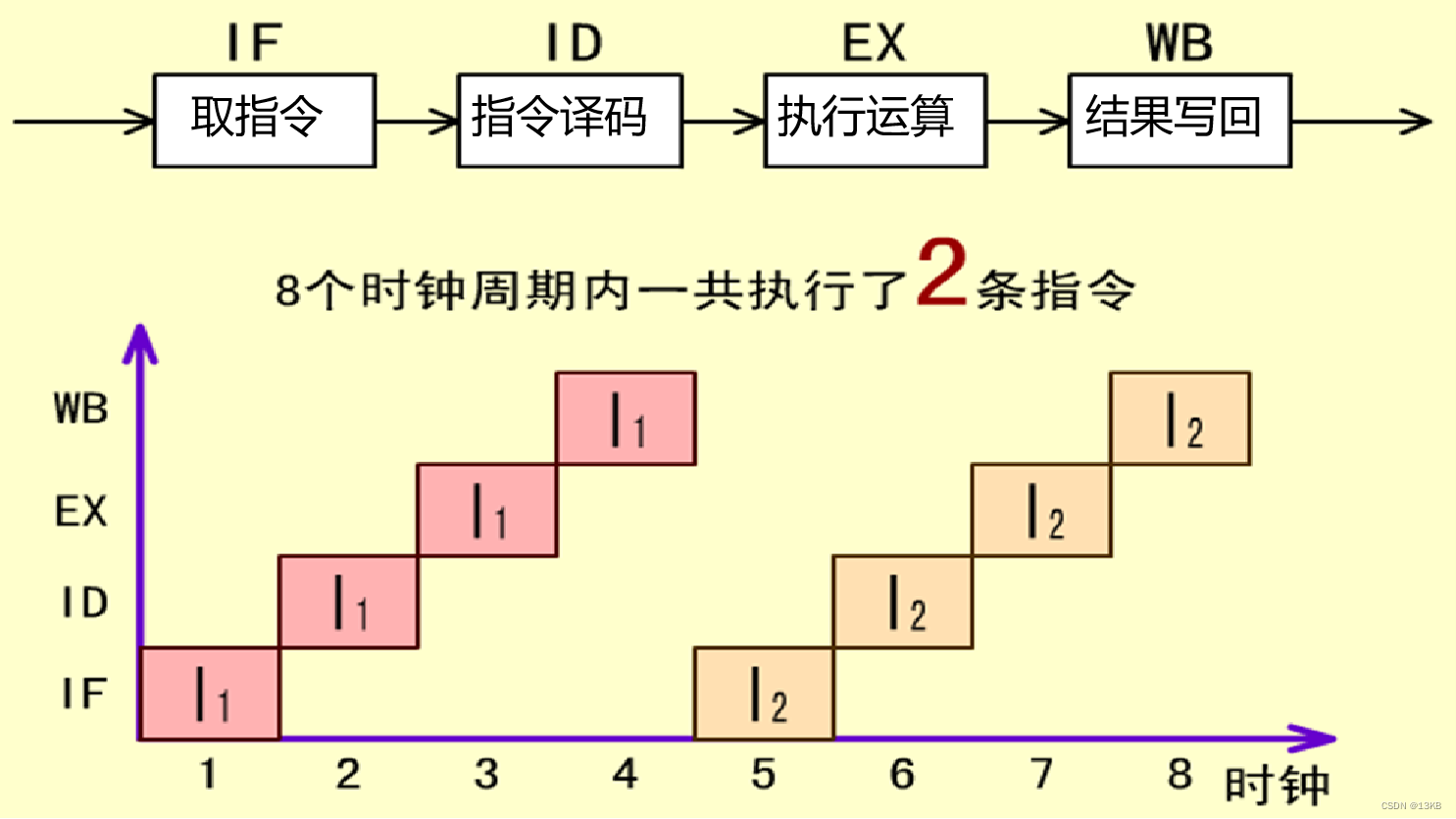

在流水线CPU中,通常将指令执行过程划分为四个主要阶段,分别是指令获取(Instruction Fetch,IF)、指令译码(Instruction Decode,ID)、执行(Execution,EX)和写回(Write Back,WB)。(看看就行,考场就忘了)

下面是对每个阶段的简要描述:

指令获取(IF):在这个阶段,流水线从指令存储器(Instruction Memory)中获取下一条要执行的指令,并将其送入流水线。这个阶段通常包括指令地址计算、内存访问和指令缓存等操作。

指令译码(ID):在这个阶段,取出的指令被解码并分析其操作码和操作数。该阶段还包括寄存器文件(Register File)的读取,以获取指令所需的操作数。此外,还可能进行分支预测和处理异常等操作。

执行(EX):在这个阶段,使用译码阶段提供的操作数执行指令的实际计算或操作。这个阶段的具体操作取决于指令的类型,例如算术运算、逻辑运算、内存访问或条件分支等。执行阶段可能涉及ALU(算术逻辑单元)、乘法器、除法器和浮点运算单元等硬件。

写回(WB):在这个阶段,执行阶段的结果被写回到寄存器文件或内存中,以完成指令的执行。这个阶段通常涉及将计算结果写入目标寄存器或内存位置,并更新相应的状态信息。

👿1.非流水时空图

?👿2.流水时空图

👿3.超流水时空图

?

?超流水CPU比流水CPU功能更加厉害为啥不选这个?

答案很明确:你一天学10小时,没学够;学18个小时,正好,还有点意犹未尽;学23个小时学的挺多但是效果减半,还有可能直接猝死。

超流水(Superpipelining)是一种进一步细分流水线阶段的技术,旨在进一步提高流水线CPU的执行效率和吞吐量。在超流水设计中,CPU的流水线阶段数量更多,每个阶段的操作更细粒度,允许更快的时钟周期和更高的指令吞吐量。

尽管超流水技术在理论上可以进一步提高流水线CPU的性能,但在实践中并不常见,并且不被广泛推荐使用,主要有以下原因:

数据冒险和控制冒险的风险增加:随着流水线阶段的增加,指令在流水线中的停顿和冲突的可能性也增加。数据冒险和控制冒险是流水线中常见的问题,在超流水设计中更容易发生。这些冒险会导致流水线停顿,降低吞吐量和性能。

硬件复杂性增加:超流水设计需要更多的流水线阶段和更细粒度的操作,这会导致更多的硬件资源和更复杂的控制逻辑。这增加了设计、验证和实现的复杂性,可能导致更高的成本和更长的开发周期。

时钟频率限制:随着流水线阶段的增加,每个阶段的操作时间必须缩短,以保持整个指令流水线的时钟周期不变。然而,更短的操作时间可能受到物理限制和电路延迟的限制,导致时钟频率的限制。这可能抵消了超流水设计带来的性能增益。

所以说别卷了,洗洗睡吧!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

🌈1.5 流水线中的问题

要使流水线具有良好的性能,必须使流水线畅通流动,不发生断流。但由于流水过程中会出现以下三种相关冲突,实现流水线的不断流是非常困难的。这三种是:资源相关,数据相关,控制相关。

- 资源相关(Resource Hazards),也称为结构相关(Structural Hazards),是指多个指令需要同时访问同一硬件资源,但该资源在同一时刻只能被一个指令所使用。这种冲突会导致指令无法同时执行,从而影响流水线的性能。

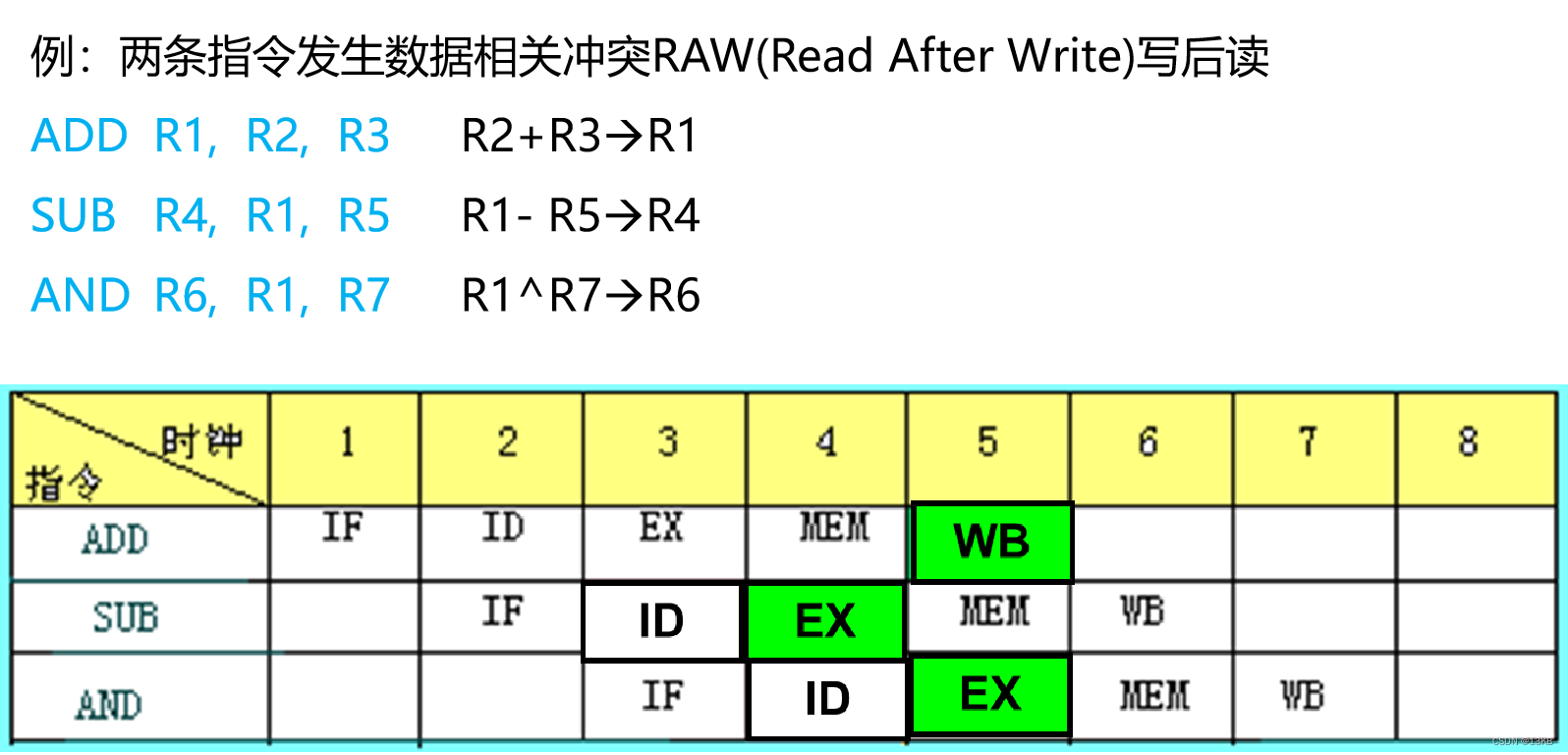

数据相关(Data Hazards):数据相关是指后续指令需要使用前一条指令的结果,但前一条指令的结果还未就绪或者不可用的情况。数据相关包括以下几种类型:读后写(Read-after-Write)相关:后续指令需要读取前一条指令刚刚写入的数据。写后读(Write-after-Read)相关:后续指令需要读取前一条指令刚刚写入的数据。写后写(Write-after-Write)相关:后续指令需要写入与前一条指令相同的寄存器或内存位置。

控制相关(Control Hazards):控制相关是指分支指令(如条件分支或无条件分支)的转移目标依赖于前一条指令的条件结果。在流水线中,当分支指令的条件判断结果还未就绪时,后续指令已经进入流水线并开始执行。这可能导致错误的分支预测和浪费的指令执行。常见的控制相关问题包括:分支相关(Branch Hazards):分支指令的条件判断结果还未就绪,导致后续指令的执行路径选择出现错误。

?1.资源相关

2.数据相关?

?3.控制相关

引起原因:转移指令,当前指令有跳转,但流水已经开启后续指令处理过程。

- 解决办法1:延迟转移法,让跳转的指令接在最后流水入口 。

- 解决方法2:转移预测法,用硬件预测将来的行为,提前让转移指令进流水。

🌈1.6小结回顾

--------------------------------------------------------------------------------------------------------------------------------

---------------------------------------------------------------------------------------------------------------------------------

2.CISC和RISC CPU

🌈2.1概念

- CISC(Complex Instruction Set Computer)和 RISC(Reduced Instruction Set Computer)是两种计算机体系结构的设计理念。

- CISC是一种复杂指令集计算机体系结构,它的设计思想是提供丰富而复杂的指令集,可以执行一条指令完成多个高级操作。CISC体系结构中的指令通常具有不同的格式和长度,可以执行复杂的操作,包括内存访问、算术运算、逻辑运算等。CISC体系结构的特点是指令集复杂、指令格式多样、指令执行周期长。

- 常见的CISC架构包括x86架构。CISC 的典型代表: x86 架构

- CISC优势: 少量指令实现大量功能,同时节省了程序本身的大小,降低内存空间的占用。

- CISC 劣势: 指令集中包含的指令非常多, 而且功能复杂,难以理解。大多数场景下, CISC 的指令使用频率相差极为悬殊,其中 20% 的指令被频繁重复使用,占据了程序功能中的 80% 代码。而剩下的 80% 的指令被闲置。

- RISC是一种精简指令集计算机体系结构,它的设计思想是通过简化指令集,提高指令执行的效率和性能。RISC体系结构中的指令通常具有固定的格式和长度,执行的操作也比较简单和基本,例如加载、存储、算术和逻辑操作等。RISC体系结构的特点是指令集简单、指令格式统一、指令执行周期短。常见的RISC架构包括ARM和MIPS架构。

- RISC 的典型代表: ARM 架构、THUMB 架构、RISC-V 架构。

- RISC 优势: CPU 一个时钟周期能同时运行多条指令,效率得以提升, 同时指令集相对较少, 便于理解。

- RISC 劣势:完成同样的功能,相比 CISC 来说要使用更多的指令, 导致内存空间要消耗的更多, 但是随着目前内存空间的持续增加,其实也不是什么大的问题。

🌈2.2RISC和CISC对比

| ? ? ? ? ? ? ? ? ? 比较内容 | ? ? ? ? ? ? ? ? ? ?CISC | ? ? ? ? ? ? RISC? ? ? ?? |

| ?指令系统 | 复杂,庞大 | ?简单,精简 |

| ?指令数目 | ?一般大于200 | ?一般小于100 |

| ?指令格式 | ?一般大于4 | 一般小于4 |

| ?寻址方式 | 一般大于4 | 一般小于4 |

| 指令字长 | 不固定 | 等长 |

| 各种指令使用频率 | 相差很大 | 相差还不大 |

| 程序源代码长度 | 较短 | 较长 |

| 控制器实现方式 | 大多微程序控制器 | 大多硬布线控制器 |

- CISC和RISC之间的主要区别在于指令集的复杂性和执行效率。

- CISC体系结构通过提供复杂的指令集,可以在一条指令中完成多个操作,但指令执行的效率相对较低。

- 而RISC体系结构通过简化指令集,使得指令的执行更加高效,但需要更多的指令来完成复杂的操作。

随着技术的发展和计算机体系结构的演进,CISC和RISC之间的界限逐渐模糊。现代的处理器通常采用了一种混合的设计,称为CISC-RISC结合体(CISC-RISC Hybrid),它结合了CISC和RISC的优点,将复杂的指令翻译成更简单的内部微操作执行,以提高执行效率。

🎵2.3CPU知识小结

- 早期的CPU由控制器和运算器组成。当今的CPU芯片由运算器,cache,控制器三部分。

- CPU中至少有6种寄存器:指令寄存器,程序计数器,地址寄存器,数据缓冲寄存器,通用寄存器,状态条件寄存器。

- CPU从存储器取出一条指令并执行这条指令的时间和称为指令周期。CISC中,由于各种指令的操作功能不同,各种指令的指令周期是不尽相同的,划分指令周期,是设计操作控制器的重要依据。RISC中,由于流水执行,大部分指令在一个机器周期完成。

- 微程序设计技术是利用软件方式设计操作控制器的一门技术,具有规整性,灵活性,可维护性等一系列优点,因而在计算机设计中得到广泛应用。随着ULSI技术的成熟和对机器速度的要求,硬布线逻辑设计思想又得到重视。(微程序和硬布线的应用场景特性对比)。

- 并行技术已成为计算机发展的主流,并行处理技术可贯穿于信息加工的各个步骤和阶段。概括起来主要有三种形式:时间并行,空间并行,时空并行。

- 流水CPU是以时间并行为原理设计的处理机。是一种是一种非常经济实用的并行技术。目前的高性能微处理器几乎都是用流速技术。

- 流水技术的主要问题是:资源相关,数据相关,控制相关。为此需要采取相应的技术才能保证流水线不断流。

- RISC CPU 是继承CISC CPU的成功技术,并在克服CISC的缺点基础上发展起来的。RISC三个基本要素:1.一个有限的简单指令系统,2.CPU配备大量的通用寄存器,3.强调指令流水线的优化。RISC机器一定是流水CPU。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Qt窗体常用属性设置

- Linux mesg命令教程:如何控制终端的消息接收(附案例详解和注意事项)

- 在Web of Science上检索某个学者的文章

- 制作小米导航实验

- Ansible的安装及简单使用

- Linux - 记录问题:docker 迁移 更改镜像默认位置的注意事项

- DriveWorks Solo捕获参数(二)

- 1,探索「两数之和」问题的多种算法解决方案

- 2023年12月青少年机器人技术等级考试(一级)理论综合试卷

- 函数指针