《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(16)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(15)

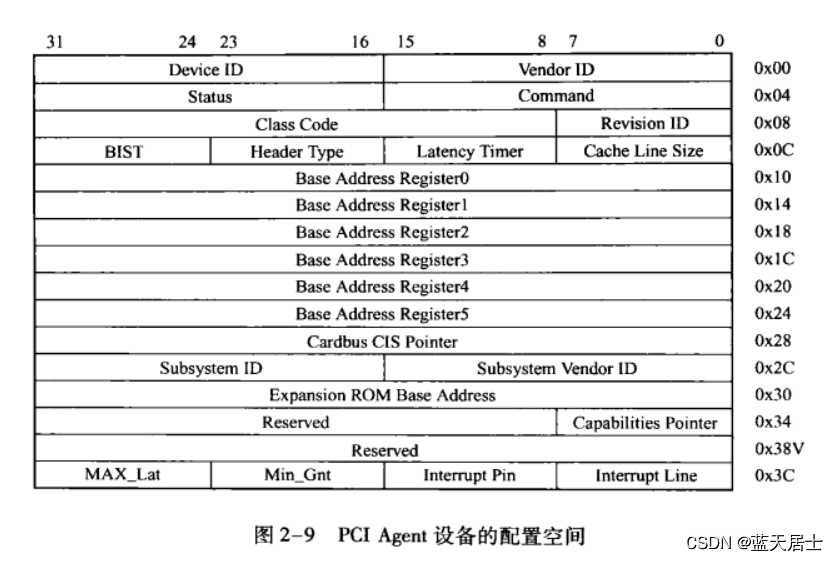

2.3.2?PCI Agent设备的配置空间

在PCI Agent设备的配置空间中包含了许多寄存器,这些寄存器决定了该设备在PCI总线中的使用方法,本节不会全部介绍这些寄存器,因为系统软件只对部分配置寄存器感兴趣。PCI Agent设备使用的配置空间如图2-9所示:

本回继续讲解在PCI Agent设备的配置空间中包含的其余寄存器:

(11)Command寄存器

该寄存器为PCI设备的命令寄存器,在初始化时,其值为0。此时,这个PCI设备除了能够接收配置请求总线事务之外,不能接收任何存储器或者I/O请求。系统软件需要合理设置该寄存器之后,才能访问该设备的存储器或者I/O空间。在Linux系统中,设备驱动程序调用pci_enable_device函数,使能该寄存器的I/O和Memory Space位之后,才能访问该设备的存储器或者I/O地址空间。

Command寄存器各个位的含义如表2-4所示:

表2-4 Command寄存器

| 位 | 描述 |

|---|---|

| 0 | I/O Space位。该位表示PCI设备是否响应i/O请求,为1时响应,为0时不响应。如果PCI设备支持I/O地址空间,系统软件会将该位置1。复位值为0 |

| 1 | Memory Space位。该位表示PCI设备是否响应存储器请求,为1时响应,为0时不响应。如果PCI设备支持存储区地址空间,系统软件会将该位置1。复位值为0 |

| 2 | Bus Master位。该位表示PCI设备是否可以作为主设备,为1时PCI设备可以作为主设备,为0时不能作为主设备。复位值为0 |

| 3 | Special Cycle位。该位表示PCI设备是否响应Special总线事务,为1时响应,为0时不响应。PCI设备可以使用Special总线事务,将一些信息广播发送到多个目标设备,Special总线事务不能穿越PCI桥。如果一个PCI设备需要将Special总线事务发送到PCI桥之下的总线时,必须使用Type 01h配置周期。PCI桥可以将Type 01h配置周期转换为Special周期。该位的复位值为0 |

| 4 | Memory Write and Invalidate位。该位表示PCI设备是否支持Memory Write and Invalidate总线事务,为1时支持,为0时不支持。许多低端的PCI设备不支持这种总线事务。该位对PCIe设备无意义 |

| 5 | VGA Palette Snoop位。该位为1时支持Palette Snoop功能,为0时不支持 |

| 6 | Parity Error Reponse位,复位值为0。该位为1、并且PCI设备在传送给过程中出现奇偶校验错误时,PCI设备将PERR#信号设置为1;该位为0时,即便出现奇偶校验错误,PCI设备也仅会将Status寄存器的“Detected Parity Error”位置1 |

| 7 | - |

| 8 | SERR# Enable位。复位值位0。该位为1,并且PCI设备出现错误时,将使用SERR#信号,将这个错误信息发送给HOST主桥;为0时,不能使用SERR#信号 |

| 9 | Fast Back-to-Back位。该位为1时,PCI设备使用Fast Back-to-Back(快速背靠背)总线周期。这种周期是一种提高传送效率的方法。但并不是所有的PCI设备都支持Fast Back-to-Back传送周期。该位的复位值为0 |

| 10 | Interrupt Disabable位,复位值为0。该位为1时,PCI设备不能通过INTx信号向HOST主桥提交中断请求;为0时可以使用INTx信号提交中断请求。当PCI设备使用MSI中断方式提交中断请求时,该位将被置为1 |

(12)Status寄存器

该寄存器的绝大多数位都是只读,保存PCI设备的状态,其含义如表2-5所示:

表2-5 Status寄存器

| 位 | 描述 |

|---|---|

| 3 | Interrupt Status位,该位只读。该位为1且Command寄存器的Interrupt Disable位为0时,表示PCI设备已经使用INTx信号向处理器提交了中断请求。在多数PCI设备中的BAR空间,存在自定义的中断状态寄存器,因此设备驱动程序很少使用该位判断PCI设备是否提交了中断请求 |

| 4 | Capabilities List位,该位只读。该位为1时,Capability Pointer寄存器的值有效 |

| 5 | 66MHz Capability位,该位为只读。为1时表示此设备支持66MHz的PCI域 |

| 7 | Fast Back-to-Back Capable位。该位只读,该位为1,表示此设备支持快速背靠背总线周期 |

| 8 | Master Data Parity Error位。PCI总线的PERR#信号有效时将置该位为1;当PCI总线出现数据传送错误时置此位为1;当Command寄存器的Parity Error Response位为1时,置此位为1 |

| 9~10 | DEVSEL timing字段。该字段为0b00时表示PCI设备为快速设备;为0b01时表示PCI设备为中速设备;为0b10时表示PCI设备为慢速设备。快速设备要求PCI总线字段主设备置FRAME#信号有效的一个时钟周期后,置DEVSEL#信号有效;中速设备要求PCI总线主设备置FRAME#信号有效的两个时钟周期后,置DEVSEL#信号有效;慢速设备要求PCI总线主设备置FRAME#信号有效的两个时钟周期后,置DEVSEL#信号有效。 在一条PCI总线上,如果快速设备、中速设备和慢速设备都没有使用DEVSEL#信号响应当前总线事务,这条总线上的负向译码设备将被动地接收这个总线事务。如果在这条总线上没有负向译码设备,主设备在FRAME#信号有效后的第4个时钟周期,使用主设备夭折时许,结束当前总线事务。 值得注意的是,在PCI-X总线中,该字段的含义与PCI总线有所不同 |

| 11 | Signaled Target Abort位。该位由PCI目标设备设置,当目标设备使用目标设备夭折(Target Abort)时序结束当前总线周期时,PCI设备将置该位为1 |

| 12 | Received Target Abort位。该位由PCI主设备设置,当发生目标设备夭折时序时,该位被置1 |

| 13 | Receved Master Abort位。该位由PCI主设备设置,当发生主设备夭折时序时,该位被置1。当以上几个Abort位有效时,表示PCI总线的数据传送通路出现了较为严重的问题 |

| 14 | Signaled System Error位。当设备置SERR#信号有效时,该位被置1 |

| 15 | Detected Parity Error位。当设备发现奇偶校验时,该位被置1 |

(13)Latency Timer寄存器

在PCI总线中,多个设备共享同一条总线带宽。该寄存器用来控制PCI设备占用PCI总线的时间。当PCI设备获得总线使用权,并使能Frame#信号后,Latency Timer寄存器将递减。当该寄存器归零后,该设备将使用超时机制停止对当前总线的使用(此时GNT#信号为无效,为提高仲裁效率,PCI设备在进行数据传送时,GNT#信号可能已经无效)。

如果当前总线事务为Memory Write and Invalidate时,需要保证一个完整Cache行的操作结束后,才能停止当前总线事务。对于多数PCI设备而言,该寄存器的值为32或64,以保证一次突发传送的基本单位为一个Cache行。

PCIe设备不需要使用该寄存器,该寄存器的值必须为0。因为PCIe总线的仲裁方法与PCI总线不同,使用的连接方法也与PCI总线不同。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- R语言【cli】——builtin_theme():内置的CLI主题

- Excel乱码?教你3个简单解决方法!

- PySide6多线程处理yolov5目标检测

- 前端如何性能优化

- AI创作系统ChatGPT网站源码,支持AI绘画,支持GPT语音对话+DALL-E3文生图

- Qt之有趣的数字钟

- 基于java的SSM框架实现在线投稿网站系统项目【项目源码+论文说明】计算机毕业设计

- 如何配置phpmyadmin,使它打开后自动登陆(不需要输入用户名和密码)

- Spark调优解析-spark调优基本原则1(七)

- 前端根据文件url路径判断文件预览或者下载以及自定义