NXP应用随记(五):eMios功能点阅读随记

目录

2.1、eMIOS - Single Action Input Capture (SAIC)

2.2、eMIOS - Single Action Output Compare (SAOC)

2.3、eMIOS - Double Action Output Compare (DAOC)

2.4、eMIOS - Pulse/Edge Counting (PEC) – Single Shot

2.5、eMIOS - Pulse/Edge Counting (PEC) – Continuous Mode

2.6、eMIOS - Input Pulse Width Measurement (IPWM)

2.7、eMIOS - Input Period Measurement (IPM)

2.8、eMIOS - Modulus Counter Mode (MC) – UP Counter

2.9、eMIOS - Modulus Counter Buffer Mode (MCB) – UP Counter

2.10、eMIOS - Modulus Counter Buffer Mode (MCB) – UP/DOWN Counter

2.11、eMIOS - Output Pulse Width and Frequency Modulation Buffered (OPWFMB)

2.12、eMIOS -中心对齐输出脉宽调制与死区插入缓冲(OPWMCB)

2.14、eMIOS -带触发器的输出脉宽调制(OPWMT)

1、概念点

An与Bn

????????EMIOS模块包含两个通道,每个通道都包含两个双缓冲数据寄存器,分别称为A和B。这两个寄存器分别为An和Bn,其中n是通道的编号,通常为0或1。

????????具体来说,每个通道都有两个双缓冲数据寄存器:

????????·An 寄存器: 这是通道n的一个缓冲区,用于存储数据。当通道正在使用An缓冲区时,可以在后台准备并更新Bn缓冲区的数据。

????????·Bn 寄存器: 这是通道n的另一个缓冲区。当An缓冲区正在被使用时,可以在Bn缓冲区中准备下一组数据,以便在切换缓冲区时,新的数据可以立即被通道使用。

????????这种双缓冲的设计允许在一个缓冲区传输数据的同时,另一个缓冲区可以准备新的数据,以保证连续的数据传输。这对于实时控制和高效的数据处理非常有用,因为可以在不中断当前操作的情况下进行缓冲区的切换,确保数据的连续性。

????????在使用EMIOS模块进行编程时,程序员可以操作这些An和Bn寄存器,以实现对通道的控制和数据的处理。这样的结构通常用于处理定时器、PWM(脉冲宽度调制)、捕获和比较等应用。

????????通过An[A]、Bn[B]、ALTAn[ALTA]来访问影子寄存器。

????????每个An[A]实例都有一个独立的关联实例AS1和AS2。在某些UC模式下,还可以使用ALTAn[ALTA]访问AS2。

? ? ? ? 注意的是下文中的不同模式,对An[A]、Bn[B]、ALTAn[ALTA] 的操作直接影响着影子寄存器,S32K3XX里面个人理解,影子寄存器存在,但是用户不可见,也只能通过An[A]、Bn[B]、ALTAn[ALTA] 的方式去操作,怎么操作。

2、eMios功能点

2.1、eMIOS - Single Action Input Capture (SAIC)

Type G\X\Y\H可用

返回输入信号边缘匹配的计数器总线的值。

-可以使用内部或模数计数器。

-是否可以匹配上升,下降或切换由EDPOL, EDSEL的状态决定

关注点:

? ? ? ? ·当检测到边缘时,设置标志并在寄存器A2中捕获计数器总线值。用户从UCA[n]寄存器中读取该值。

? ? ? ? ·UCB[n] =已清除,无法写入。

2.2、eMIOS - Single Action Output Compare (SAOC)

Type G\X\Y\H可用

在计数器总线匹配上生成输出。

- 可以使用内部或模数计数器

- 可以设置输出到高,低或切换,根据EDPOL和EDSEL的状态

关注点:

·创建匹配所需的计数器总线值写入UCA[n] (A2n), UCA[n] (A2n)缓冲到A1。

·比较器匹配A1将产生一个输出事件,该事件由EDPOL和EDSEL的状态定义。

2.3、eMIOS - Double Action Output Compare (DAOC)

Type G、H可用

产生一个输出脉冲。

-可以使用内部或模数计数器

-可配置为2个HIGH边或2个LOW边(EDPOL位)测量。

A2更新进A1再更新进A。

关注点:

1、将所需的脉冲前沿写入UCA[n] (A2n),将下降沿写入UCB[n] (B2n),缓存到A1和B1。

2、在比较器a匹配中,输出被设置为EDPOL的值。如果MODE0=1,则设置FLAG

3、在比较器B匹配中,输出被设置为EDPOL的倒数。设置FLAG。

2.4、eMIOS - Pulse/Edge Counting (PEC) – Single Shot

Type G 可用

返回在期望的时间窗口内在输入上检测到的脉冲或边缘的数量。

关注点:

·MODE[0] = 1位选择Single Shot操作。

·极性和触发边由EMIOSC[n]寄存器中的EDSEL和EDPOL位选择.

·A1保存时间窗口的开始时间,寄存器B1保存时间窗口的停止时间.

·另外,寄存器A2总是保存最新的可用测量值。

·比较器A和所选时间基之间的下一次匹配没有效果,直到对寄存器A执行新的写入操作。

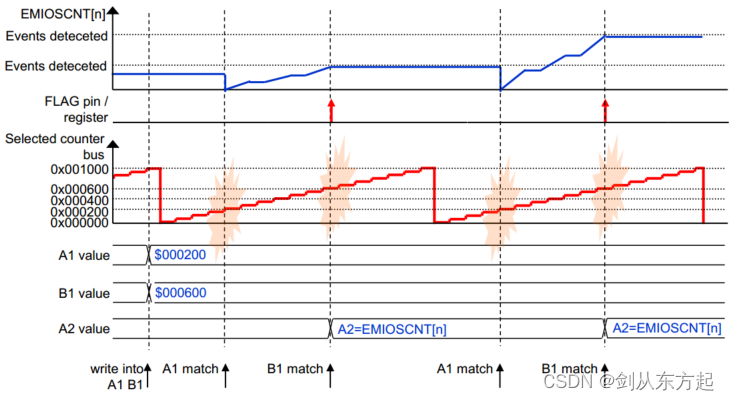

2.5、eMIOS - Pulse/Edge Counting (PEC) – Continuous Mode

Type G 可用

关注点:

·MODE[0] = 0位选择连续操作。

·极性和触发边由EMIOSC[n]寄存器中的EDSEL和EDPOL位选择

·A1保存时间窗口的开始时间,寄存器B1保存时间窗口的停止时间

·另外,寄存器A2总是保存在第一个FLAG发生后的任何时间提供一致数据的最新可用测量值。

2.6、eMIOS - Input Pulse Width Measurement (IPWM)

Type G 、H可用

确定输入脉冲宽度的宽度(在计数器总线时钟刻度中)。

-可以使用内部或模数计数器

-可以通过EDPOL位的状态来测量HIGH或LOW脉冲(EDPOL=1表示HIGH)

关注点:

-前沿被捕获到B2[n]中。(EDPOL确定前缘是高还是低)。

-后沿捕获到A2[n],并设置Flag

-脉冲宽度由UCAn (A2)减去UCBn (B1)计算。

????????警告(溢出的时候)-如果脉冲已经跨越了一个计数器总线周期,那么需要小心修改计算....宽度= (UCAn +计数器周期)- UCBn。

2.7、eMIOS - Input Period Measurement (IPM)

Type G 、H可用

确定输入脉冲宽度的周期(以计数器总线时钟刻度计)。

-可以使用内部或模数计数器

-可配置为2个HIGH边或2个LOW边(EDPOL位)测量。

??????关注点:

??当检测到所选极性的边缘时,将计数器值捕获到A2[n]和B2[n]中,将先前保存在B2[n]中的数据捕获到A1[n]和B1[n]中,并设置Flag。

????????周期由UCAn (A2)减去UCBn (B1)计算。

????????注意-如果输入信号的周期已经跨越了一个计数器总线周期,那么需要注意修改计算....

????????宽度= (UCAn +计数器周期)- UCBn

2.8、eMIOS - Modulus Counter Mode (MC) – UP Counter

Type G 、H可用

生成一个时基,可通过内部计数器时基与其他通道共享。

- 可使用内部或外部(输入通道引脚)计数器。

关注点:

?在比较器a匹配上,FLAG被设置,内部计数器被设置为值$0。

?A2寄存器的变化使A1寄存器在下一个时钟更新。

·注意-如果进入MC模式时,内部计数器值高于寄存器UCA[n]值,那么在匹配A1之前,它将在最大计数器值($FFFFFF)处包装。

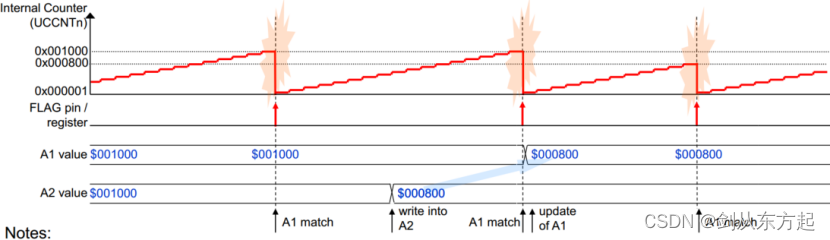

2.9、eMIOS - Modulus Counter Buffer Mode (MCB) – UP Counter

Type X可用

生成可通过内部计数器库与其他通道共享的时间库。

-可以使用内部或外部(输入通道引脚)计数器。

关注点:

·在比较器a匹配上,设置FLAG,并将内部计数器设置为值$1。

·为了实现平稳的转换,当内部计数器达到$1时,A2寄存器的变化使A1寄存器更新。

·注意-如果进入MCB模式时,内部计数器值高于寄存器UCA[n]值,那么在匹配A1之前,它将在最大计数器值($FFFFFF)处包装。

2.10、eMIOS - Modulus Counter Buffer Mode (MCB) – UP/DOWN Counter

Type G 、X可用

生成可通过内部计数器库与其他通道共享的时间库。

-可以使用内部或外部(输入通道引脚)计数器。

关注点:

在比较器a匹配上,设置FLAG,并将内部计数器设置为值$1。

为了实现平稳的转换,当内部计数器达到$1时,A2寄存器的变化使A1寄存器更新。

2.11、eMIOS - Output Pulse Width and Frequency Modulation Buffered (OPWFMB)

Type G 、X可用

生成简单的输出 PWM 信号。

- 需要内部计数器

- EDPOL 允许在高电平有效或低电平有效占空比之间进行选择。

关注点:

占空比= UCA[n] (A1) + 1,周期= UCB[n] (B1) + 1

比较器A1匹配时,输出引脚设置为EDPOL值

比较器B1匹配时,输出引脚设置为EDPOL的补码,内部计数器复位

从寄存器B2[n]到B1[n]以及从寄存器A2[n]到A1[n]的传输在下一个周期的第一个时钟执行。

根据MODE[5]位的不同,只能在B1匹配上生成标志,也可以同时在A1和B1匹配上生成标志。

2.12、eMIOS -中心对齐输出脉宽调制与死区插入缓冲(OPWMCB)

Type G 可用

·产生中心对齐PWM输出信号与死区时间插入。

·MODE[6]位分别在尾随死区插入和前导死区插入之间选择。

·EDPOL允许有源高或有源低占空比之间的选择。

·需要MCB上/下

关注点:

Period = MCB Period, Dead Time = B1[n], Duty Cycle = 2 * (Period - A1[n]) – Dead Time

在选取的死区插入边上:

?在比较器A1匹配(选择计数器总线)上,内部计数器设置为$1

?在比较器B1匹配(内部计数器)上,输出引脚设置为EDPOL值

在非选择死区插入边缘上:

?在比较器A1匹配上,输出引脚设置为EDPOL的补码,内部计数器设置为$1

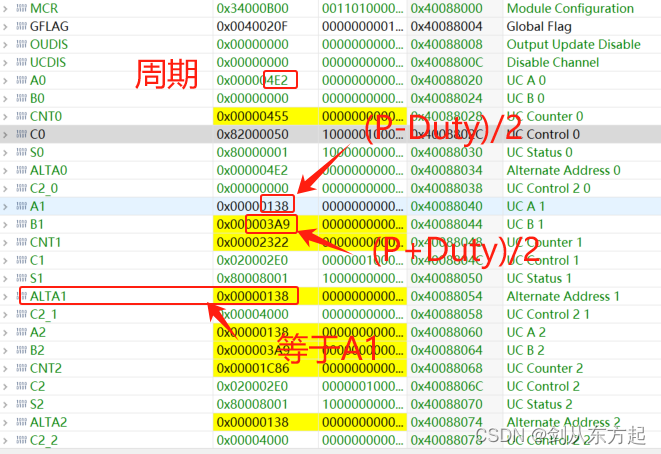

2.13、eMIOS -输出脉宽调制缓冲(OPWMB)

Type G 、H、X、Y可用

产生一个简单的输出PWM信号。

-使用模数计数器

- EDPOL允许在有源高或有源低占空比之间进行选择。

关注点:

UCA[n] (A1) 写入前沿

UCB[n] (B1) 写入后沿

在比较器A1匹配上,输出引脚设置为EDPOL的值

在比较器B1匹配上,输出引脚被设置为EDPOL的补码

从寄存器B2[n]到B1[n]和从寄存器A2[n]到A1[n]的传输在下一个周期的第一个时钟执行。

根据MODE[5]位的不同,只能在B1匹配上生成标志,也可以同时在A1和B1匹配上生成标志。

程序里面体现如下:

假设TICKS为0x4E2,占空比为50%,emios0_0作为Count bus,emios0_1、emios0_2、emios0_3参考emios0_0输出,寄存器如下显示。

2.14、eMIOS -带触发器的输出脉宽调制(OPWMT)

Type G 、H、X、Y可用

·产生一个固定偏移量的PWM信号和一个触发信号。

·-旨在与具有共享公共时基的相同模式下的其他信道一起使用。

·这种模式在产生 lighting ?PWM控制信号时特别有用

A1[n]定义前缘,B1[n]定义后缘,A2[n]定义FLAG事件的生成

在比较器A1匹配上,输出引脚设置为EDPOL的值

在比较器A2匹配时,FLAG被设置(并且可以允许与其他事件同步,例如:AD告转换)

在比较器B1匹配上,输出引脚被设置为EDPOL的补码

寄存器B2[n]到B1[n]的传输在寄存器A1的每次匹配时执行

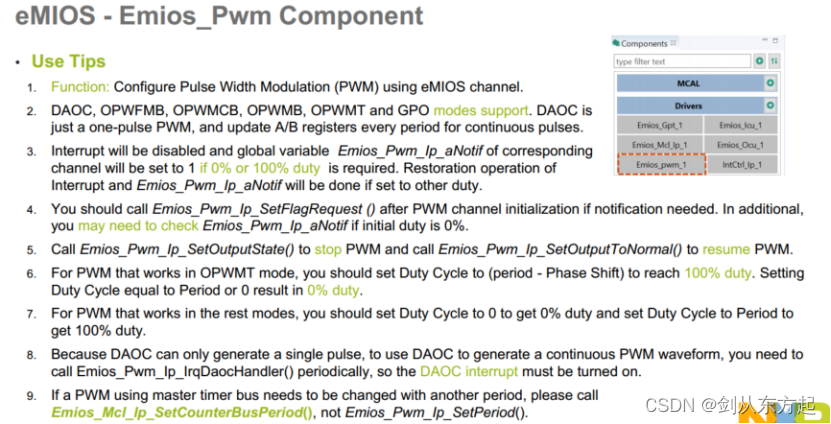

3、RTD组件详细介绍

3.1、eMIOS -概述的eMIOS组件的RTD

配置工具提供五个RTD的eMios实现驱动应用。

- eMios的为控制库,也就是MCAL

- eMios的GPT模块

- eMios的输出比较单元

- eMios的PWM

- eMios的IC

需要注意的:

如果想使用其他四个派生程序,则必须在项目中添加Emios_Mcl_Ip。

每个eMIOS RTD模块都有自己的Irq函数,您可以为应用程序设置一个回调函数。

所有处理程序项都在Mcl Irq文件中分配。

EMIOSx_x_IRQ -> Emios_Xxx_Ip_IrqHandler(inst, channel) -> CallbackFunction/Notification

eMIOS初始化一般流程:

Initialize instance (Mcl) -> Initialize channel (Gpt, Ocu, Pwm, Icu) -> other (start, notification, etc.)

3.2、eMIOS - Emios_Mcl_Ip组件

1、启用eMIOS通用支持。

·否则,EmiosCommon不可用。

·需要启用错误检测

2、配置全局eMIOS。

启用eMIOS实例冻结状态和全局时基。

设置全局时钟分频值:1 ~ 256

3、配置eMIOS主总线

选择硬件通道

选择master bus

选择默认周期与通道分频

启用或禁用调试模式和中断

主总线通道不能配置为其他模式。

MC与MCB的区别:MC表示本周期,MCB表示下周期,起作用的时间不一样

3.3、GPT的使用

3.4、OCU的使用

3.5、PWM使用

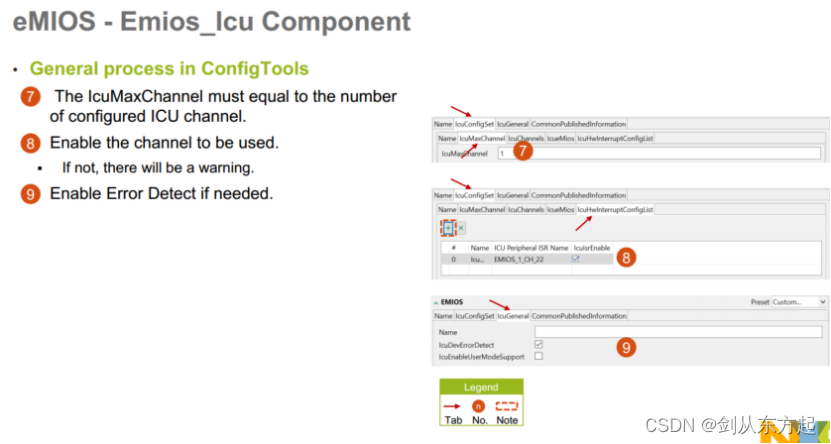

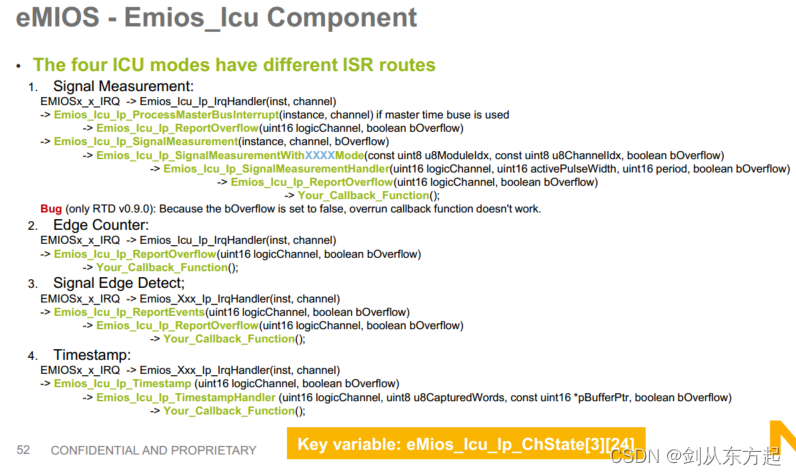

3.6、ICU的使用

除主总线通道(ch[23])外,每个 eMIOS 通道都能触发 BCTU。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 网络安全(网络安全)—2024自学

- 探讨APP自动化测试工具的重要性

- 使用Go语言处理Excel文件的完整指南

- yarn无法加载文件和‘vue-cli-service‘ 不是内部或外部命令解决方法

- 【云原生技术】地域、可用区、集群、VPC、工作空间、命名空间的联系

- 交叉验证理解

- Codeforces Beta Round 51 D. Beautiful numbers

- 【开题报告】基于springboot的大学生租房平台的设计与实现

- 新生代和老年代介绍

- 【解决方法】pdf密码忘了怎么办?