ARM多核调度器DSU

1. 背景

????????从A75开始,ARM提出了一个新的多核心管理系统单元,叫做DSU(DynamIQ Shared Unit)。DSU的核心功能是控制CPU内核,使其成簇Cluster使用,簇内每一个核心可以单独开关、调整频率/电压,能效表现更佳,甚至制造商是可以将不同核心以不对等的数量放到一个簇内,兼顾成本与性能。

????????再有就是L3缓存的共享。DSU能够使用CCI、CCN或是CMN不同总线技术,把CPU与SoC里其它单元(GPU、Modem、内存)高速连接起来;假如它拥有4MB三级缓存,能以动态方式分配缓存给每个核心,比如说Cortex-A75×1+ Cortex-A55×7下,可以将3MB缓存分配给A75核心,剩下7个A55核心共享1MB缓存,甚至可将三级缓存交给GPU等单元使用,灵活性非常高;

????????在设计DynamIQ之时ARM还考虑到冗余需求,比如相比智能手机,汽车对可靠性、冗余度要求高出不少,DynamIQ允许多个簇通过CCIX连接在一起,这样处理器就可以分布于汽车不同位置,当发生交通意外一个簇受损时,DynamIQ技术可以调用出备用处理器,保证汽车正常运转。

2. DSU结构

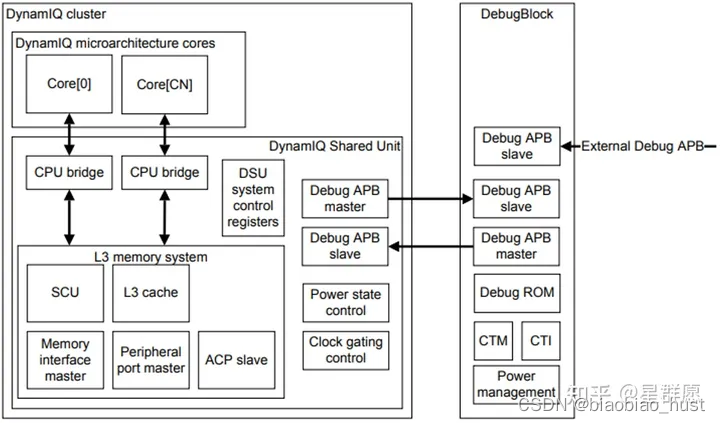

DynamIQ cluster顶层由DSU与DebugBlock组成。

DSU:包含L3、ctrl logic & external interface。

DebugBlock:包含3组apb接口、rom、CTM、CTI & PMU。

2.1 组件说明

| 元件 | 描述 |

| CPU桥接器 | CPU 网桥,控制内核和 DSU 之间的缓冲和异步处理。 |

| 时钟和电源管理 | 群集支持一组由外部电源控制器控制的省电模式。这些模式是通过 P 通道上的电源模式请求来选择的,对于每个内核,以及用于 DSU 的单独 PChannel。 通过从外部时钟控制器向DSU发出的Q通道请求来支持时钟门控。Q 通道允许单独控制 SCLK、PCLK、ATCLK 和 GICCLK 时钟输入。 |

| Snoop 控制单元 | SCU 保持集群中所有数据缓存之间的一致性,存在私有的缓冲区 |

| L3 缓存 | 缓存大小实现为 256KB、512KB、1MB、1.5MB、2MB、3MB 或 4MB。 所有缓存的行长均为 64 字节。 可选择实现数据和标签RAM的ECC保护。 |

| 主存储器主控 | 主存储器接口最多支持两个ACE或CHI主接口。 |

| 加速器一致性端口 | 加速器一致性端口 (ACP) 是可选的从接口。ACP 提供对可缓存内存的直接内存访问。SCU 通过检查 ACP 访问在核心和 L3 缓存中的分配来保持缓存一致性。ACP 实现了ACELite 协议的子集。 |

| 外设端口 | 外设端口是可选的主接口,提供对紧密耦合加速器的DEVICE访问。该端口实现 AXI 4 主接口协议。 |

| DSU系统控制寄存器 | DSU 实现一组系统控制寄存器,这些寄存器对群集中的所有内核都是通用的。您可以从 集群中的任何内核访问这些寄存器。这些寄存器提供: 1.控制群集的电源管理。 2.L3缓存分区控制。 3.CHI QoS总线控制和方案ID分配。 4.有关 DSU硬件配置的信息。 5.L3 缓存命中和未命中计数信息。 |

| 调试和跟踪组件 | 每个内核都包括一个嵌入式跟踪宏单元 (ETM),允许在调试时进行程序跟踪。 来自内核的触发事件被合并并输出到调试 APB 主节点。在调试 APB 从机上接收到内核的触发事件和调试寄存器访问。 |

| 群集到 DebugBlock APB | 当 APB 写入时,来自内核的触发事件将传输到 DebugBlock |

| DebugBlock 群集 APB | 触发事件在APB 写入 DSU 时传输到内核。来自系统调试APB 的寄存器访问被传输到 DSU |

| 系统调试 APB | 系统调试 APB 从属接口连接到外部 CoreSight 组件,如调试访问端口(DAP) |

| CTI 和 CTM | DebugBlock 实现嵌入式交叉触发器 (ECT)。交叉触发接口 (CTI) 分配给集群 中的每个 PE,如果存在,则为集群 ELA 分配额外的 CTI。CTI 通过交叉触发矩阵 (CTM) 相互连接。实现单个外部通道接口,允许将交叉触发扩展到 SoC。 |

| 调试ROM | ROM 表包含系统中的组件列表。调试器可以使用 ROM 表来确定实现了哪些CoreSight 组件 |

| 电源管理和时钟门控 | DebugBlock 实现了两个 Q 通道接口,一个用于控制 PCLK 时钟的请求,另一个用于控制调试电源域的请求。 |

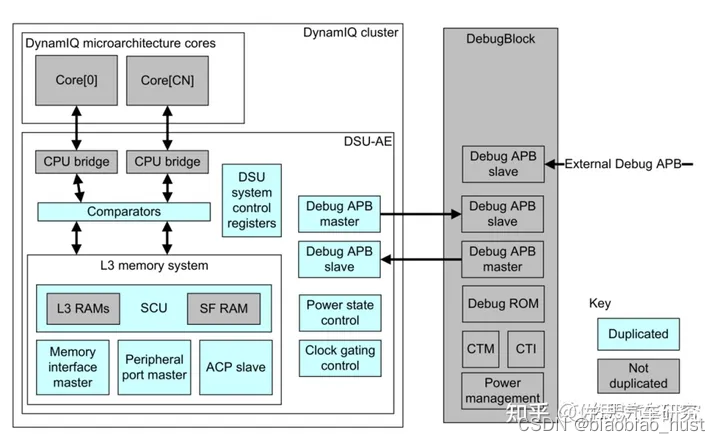

3. DSU AE结构

????????DSU AE主要是添加了比较器,再有就是亮色部分都复制一份,包括执行逻辑、时钟、功率状态,各个界面,当然缓存不能复制,那样成本太高,也意义不大。

3.1?Split模式

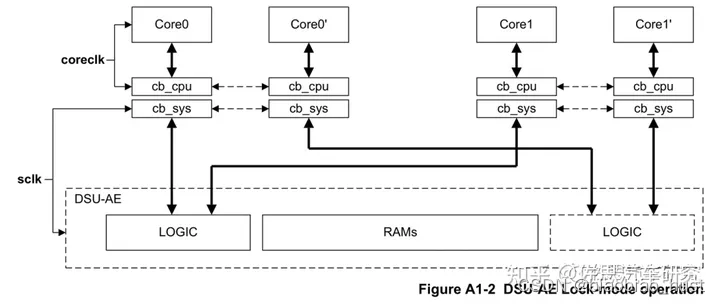

3.2 lockstep模式

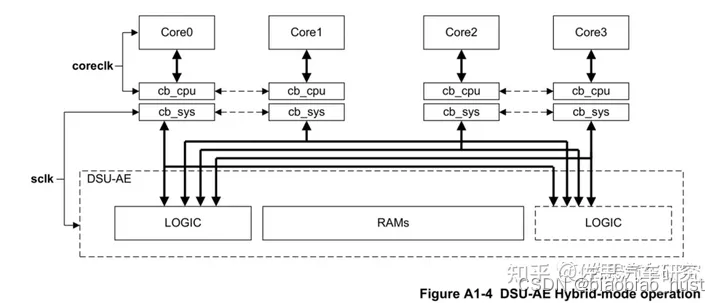

3.3 Hybrid模式

3.4 CMN

????????ARM发展了一种介于总线和NoC之间的连接系统,称之为CMN,主要用于连接CPU内核,也可以CPU内核和加速器之间的连接。采用MESH网格结构,但没有路由功能,本质上还是总线,但MESH网格支持的单元很多,远比一般总线要多,最高可支持512核,支持512MB的L3缓存,目标市场主要是HPC领域。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 渗透测试:保障网络安全的重要手段!

- 机器学习:数据处理与特征工程

- Python脚本打包成exe文件

- [论文笔记] PAI-Megatron中qwen和mistral合并到Megtron-LM

- 静态变量有什么作用?

- Android 跨进程之间通信(IPC)方式之BroadcastReceiver

- vue3引用类型和基础类型深度克隆

- Linux 为普通用户赋予docker的执行权限

- 线程的深入学习(一)

- ArrayList与LinkLIst