加法器和Verilog代码

发布时间:2024年01月15日

截图来自B站,讲的非常好,地址:

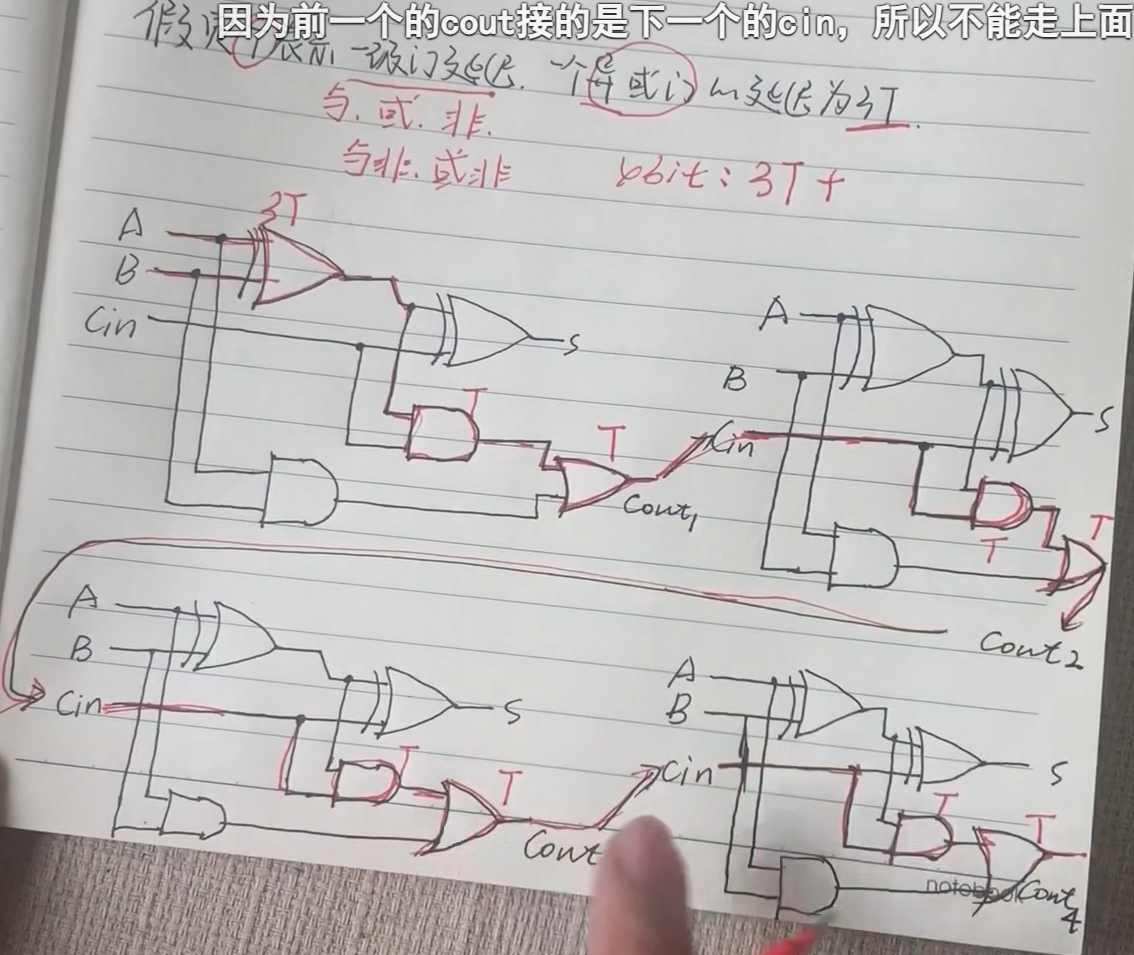

串行进位加法器

门级电路图和进位位、加和位

延迟计算

先行进位加法器(Carry Lookahead Adder):

所以在下面的verilog代码中,会把四位先行进位加法器叫做C4

ci+1=ai*bi+(ai+bi)*ci

ai*bi意思是两个数如果都是1,那就一定会有一个进位

(ai+bi)*ci意思就是,如果ai+bi=1并且上一级来的进位等于1,那么本级的进位一定等于1

ci+1=ai*bi+(ai+bi)*ci就是上述的两种情况只需要发生一种,本级就会有进位推导

g是generate,生成,p是propagate传递,A*B直接就能生成一个进位,但是A+B还需要一个上一级进位才能生成本级的进位

文章来源:https://blog.csdn.net/weixin_44357071/article/details/135597154

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 疯狂的多元宇宙-----git分支

- Generator - JavaScript的异步颠覆者

- HarmonyOs4.0基础

- 一站式查询热门小程序排名,助力小程序运营决策

- Java基础-String, StringBuilder, StringBuffer区别

- WEB接口测试之Jmeter接口测试自动化 (三)(数据驱动测试)

- 如何使用Docker本地部署Wiki.js容器并结合内网穿透实现知识库共享

- 代码随想录算法训练营第三十四天| 1005.K次取反后最大化的数组和、134.加油站、135.分发糖果

- JavaScript基础--布尔类型,空型和未定义

- 基于STM32的HX711压力传感器信号处理与应用