5.3数据通路的功能和基本结构

数据通路的基本结构:

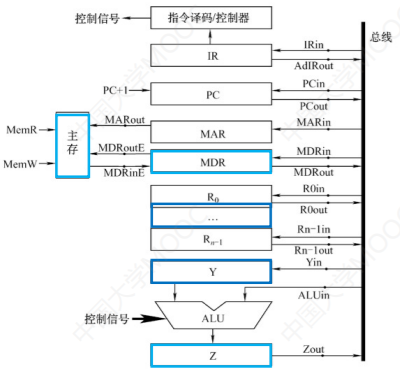

1.CPU内部单总线方式。

2.CPU内部多总线方式。

3.专用数据通路方式。

内部总线是指同一部件,如CPU内部连接各寄存器及运算部件之间的总线;

系统总线是指同一台计算机系统的各部件,如CPU、内存、通道和各类I/O接口间互相连接的总线。

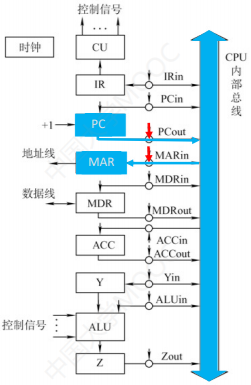

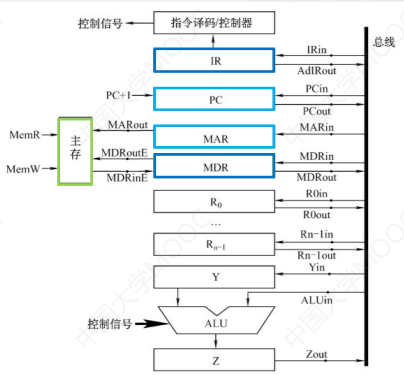

数据通路-CPU内部单总线方式

1.寄存器之间数据传送

比如把PC内容送至MAR,实现传送操作的流程及控制信号为:

(PC)->Bus PCout有效,PC内容送总线

Bus>MAR MARin有效,总线内容送MAR

也可写为:(PC)->BuS->MAR

也有的教材写为:PC->Bus->MAR

重要的是描述清楚数据流向

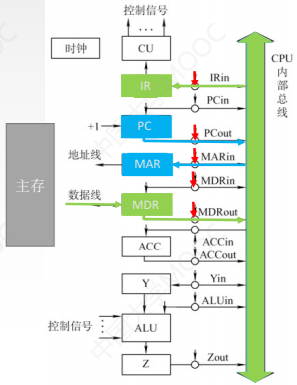

2.主存与CPU之间的数据传送

比如CPU从主存读取指令,实现传送操作的流程及控制信号为:

(PC)->Bus->MAR PCout和MARin有效,现行指令地址→>MAR

1->R CU发读命令(通过控制总线发出,图中未画出)

MEM(MAR)->MDR MDRin有效

MDR->Bus->IR MDRout和IRin有效,现行指令>IR

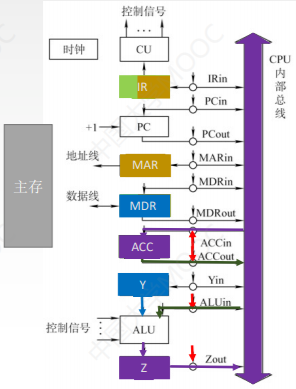

3.执行算术或逻辑运算

比如一条加法指令,微操作序列及控制信号为:

Ad(IR)->Bus->MAR MDRout和MARin有效 或AdlRout和MARin有效

1->R CU发读命令

MEM(MAR)->数据线->MDR MDRin有效

MDR->Bus->Y MDRout和lYin有效,操作数->Y

(ACC)+(Y)->z ACCout和ALUin有效,CU向ALU发送加命令

Z->ACC Zout和ACCin有效,结果->ACC

例:

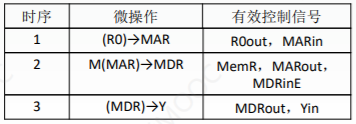

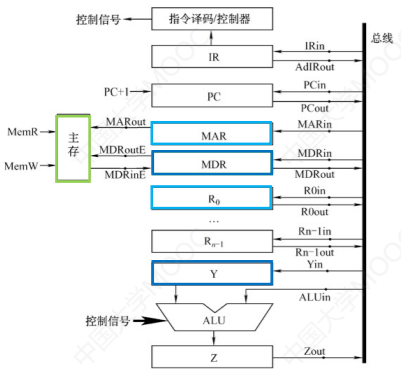

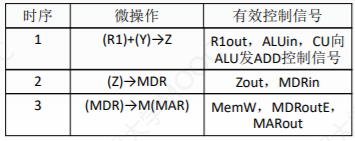

设有如图所示的单总线结构,分析指令ADD(RO),R1的指令流程和控制信号。

1.分析指令功能和指令周期

功能:((R0))+(R1)>(R0)

取指周期、间址周期、执行周期

2.写出各阶段的指令流程

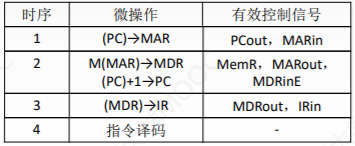

取指周期:公共操作

间址周期:完成取数操作,被加数在主存中,加数已经放在寄存器R1中。

执行周期:完成取数操作,被加数在主存中,加数己经放在寄存器R1中。

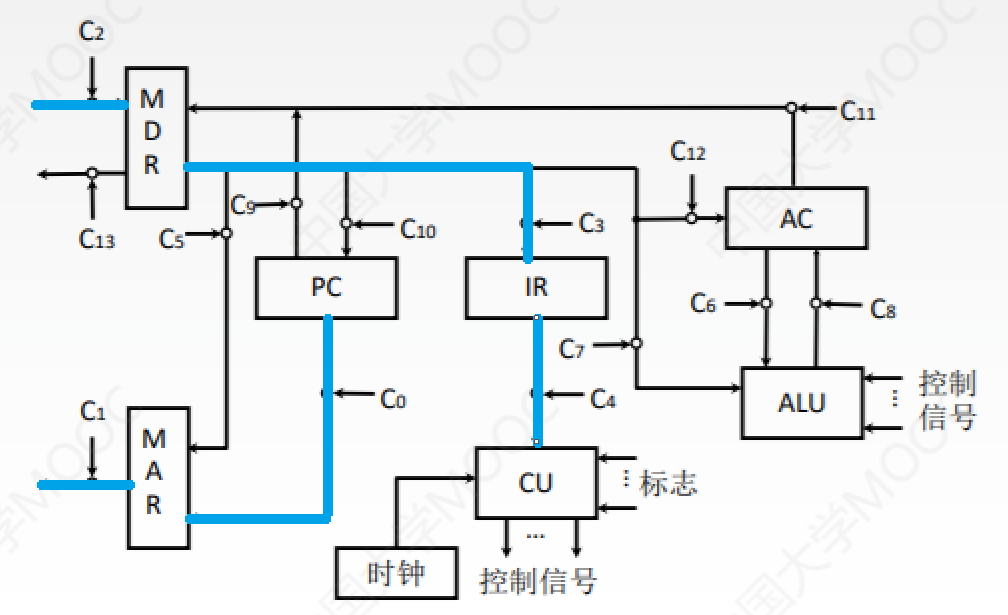

数据通路-专用通路结构

(PC)->MAR C0有效

(MAR)>主存 C1有效

1->R 控制单元向主存发送读命令

M(MAR)->MDR C2有效

(MDR)->IR C3有效

(PC)+1->PC

Op(IR)->CU C4有效

例

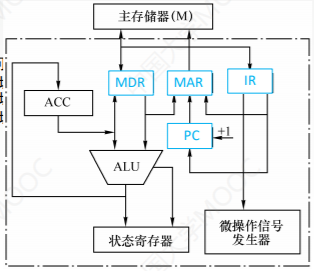

下图是一个简化了的CPU与主存连接结构示意图(图中省略了所有的多路选择器)。其中有一个累加寄存器(ACC)、一个状态数据寄存器和其他4个寄存器:主存地址寄存器(MAR)、主存数据寄存器(MDR)、程序寄存器(PC)和指令寄存器(IlR),各部件及其之间的连线表示数据通路,箭头表示信息传递方向。

(1)请写出图中a、b、c、 d 4个寄存器的名称。

d能自动“+1”,是PC

PC内容是地址,送MAR,故c是MAR

b与微操作信号发生器相连,是IR

与主存相连的寄存器是MAR和MDR,c是MAR,则a是MDR

(2)简述图中取指令的数据通路。

(PC) ->MAR

M(MAR) ->MDR

(MDR)->IR

(3)简述数据在运算器和主存之间进行存/取访问的数据通路。

存/取的数据放到ACC中

设数据地址已放入MAR

取:

M(MAR)-> MDR

(MDR)-> ALU -> ACC

存:

(ACC)-> MDR

(MDR)-> M(MAR)

(4)简述完成指令LDA X的数据通路(X为主存地址,LDA的功能为(X)->ACC)。

X ->MAR

M(MAR)-> MDR

(MDR)->ALU ->ACC

(5)简述完成指令ADD Y的数据通路(Y为主存地址,ADD的功能为(ACC)+(Y)->ACC)

Y -> MAR

M(MAR)-> MDR

(MDR)->ALU,(ACC)->ALU

ALU ->ACC

(6)简述完成指令STA Z的数据通路(Z为主存地址,STA的功能为(ACC)->Z)。

Z->MAR

(ACC) ->MDR

(MDR)-> M(MAR)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 第17课 文件操作

- 基于ssm潍坊理工学院就业信息网的设计与实现论文

- harmonyOS以修改注释颜色为例 演示如何改变DevEco Studio中指定内容颜色

- mysql使用expain查看sql语句执行

- 一段与VFP共舞的编程岁月

- 什么是金融RPA?金融RPA解决什么问题?金融RPA实施难点在哪里?

- ubuntu用终端将文件打开、编辑、保存的方法

- C/C++ 分解质因数

- SpringBoot使用支付宝沙箱环境进行仿真支付

- 回溯法解决01背包问题