【ZYNQ学习】PL第一课

这节课讲什么?

这节课的名字本来是想写为LED,但这一课里除了LED也有按键,又想换为GPIO控制,但关于PL的GPIO控制,不应该这么草率和简单,而且这一课有很多和ZYNQ或者PL关联性不强的东西要说。

所以我写了删删了写改了好几遍,终于定为《PL第一课》,而这节课就是讲ZYNQ的PL开发如何学习。

参考资料

【正点原子】领航者ZYNQ开发板资料v2,1_领航者ZYNQ之FPGA开发指南_V2.0.pdf

放轻松

其实在第一遍学习ZYNQ的时候我就已经学过了一遍PL,但由于当时公司项目紧而我本身只做PS端的工作,所以学的诚惶诚恐,学的草草了事,而这么久过去了,当我回过头来再学PL端时,没了那些压力,也多了一些经验,所以我给的第一个建议就是放轻松。

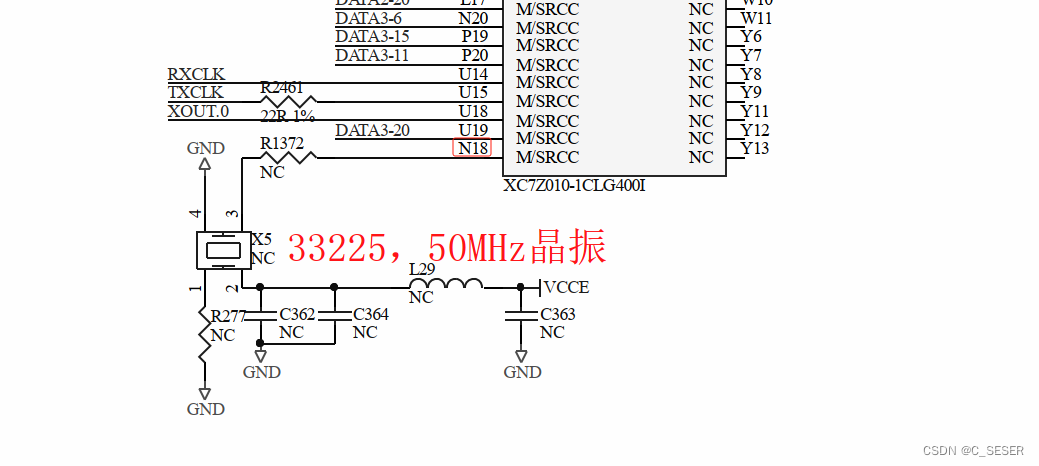

看懂原理图

看懂原理图很重要,可能很多人用正点原子的原理图,所以管脚都是直接按照文档来配置,原理图更是打都没有打开过,比如最基本的sys_clk,由于我拿到的这块板子并不是什么正规开发板,所以我第一时间用的时候也要去看一下晶振产生的时钟在哪里连接到了PL端

虽然管脚配置的代码和步骤本身很简单,但是要通过原理图自己清楚地知道应该怎么配置是非常重要的,这也能让你更清楚的知道自己在做什么,而不是一味地按照文档得到结果,而这也引出下一部分我要说的——

要求甚解

对于PL的学习,甚至整个ZYNQ的学习,其实底层都并不复杂,但现在太多人无法沉下心来恨不得一小时把最后一章的实验都做完但连最简单的一些东西都无法独立完成,在开发板上抄代码抄的风生水起,突然换到一块同样芯片的其他板子就泻火了,更别说往其他类似的板卡上迁移时出现的问题。

所以,学习不能不求甚解,而是要求甚解,当然事情都是有一个度的,我们不能遇到困难就偷看答案,也不能揪着所有问题停滞不前,要自己学会把控。

LED和按键

具体查看正点原子参考资料PDF的4.2节,此处只粘贴代码,后续会单独开一节GPIO的课程集中讲解。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/14 23:29:52

// Design Name:

// Module Name: led_twinkle

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led_twinkle(

input sys_clk,

input sys_rst_n,

output [1:0] led

);

reg [25:0] cnt;

assign led = (cnt < 26'd2500_0000) ? 2'b01: 2'b10;

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmodule

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- (更新)上市公司专利质量数据(附原始数据及stata代码,1990-2022年)

- SynchronousQueue介绍

- sqlserver->clickhouse迁移数据

- Moviepy怎样使用?

- C++ //习题13.4 建立两个磁盘文件f1.dat和f2.dat,编程序实现以下工作:(1) 从键盘输入20个整数,分别存放在两个磁盘文件中(每个文件中放10个整数);(2) 从f1.dat读入

- C++ day6

- 基于Java SSM框架实现人事员工考勤签到请假管理系统项目【项目源码+论文说明】计算机毕业设计

- 用友ERP软件-各个模块单据含义整理

- 低信噪比环境下的GPS信号识别与捕获技术

- ssm/php/node/python中医保健系统