Verilog刷题笔记14

题目:

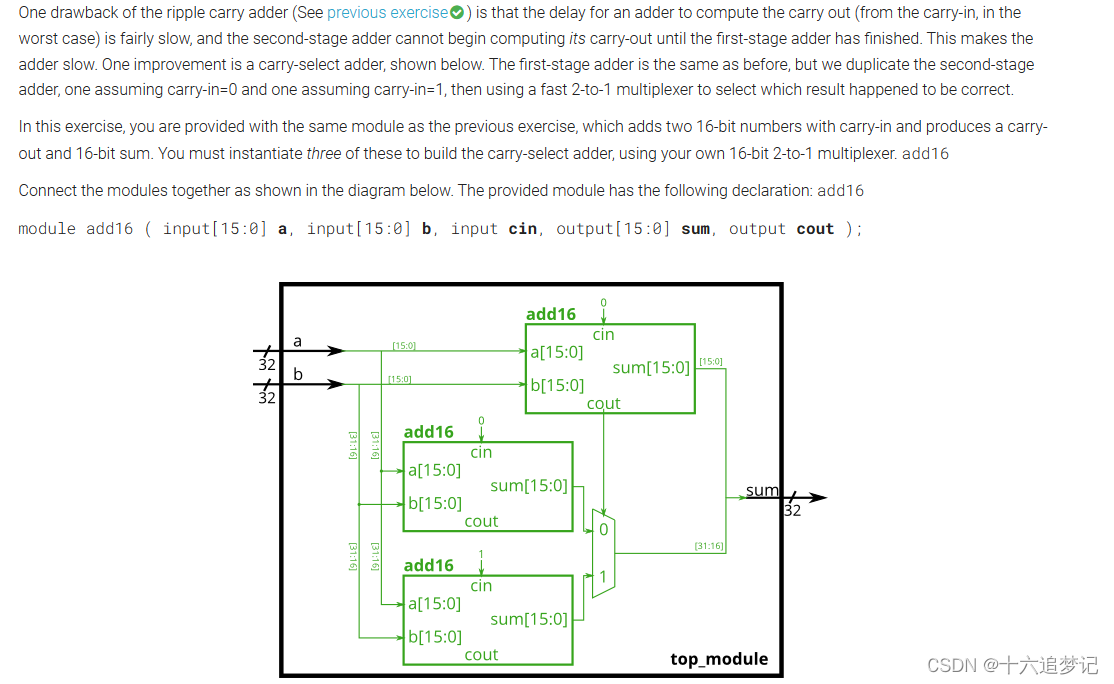

One drawback of the ripple carry adder (See previous exercise) is that the delay for an adder to compute the carry out (from the carry-in, in the worst case) is fairly slow, and the second-stage adder cannot begin computing its carry-out until the first-stage adder has finished. This makes the adder slow. One improvement is a carry-select adder, shown below. The first-stage adder is the same as before, but we duplicate the second-stage adder, one assuming carry-in=0 and one assuming carry-in=1, then using a fast 2-to-1 multiplexer to select which result happened to be correct.

In this exercise, you are provided with the same module as the previous exercise, which adds two 16-bit numbers with carry-in and produces a carry-out and 16-bit sum. You must instantiate three of these to build the carry-select adder, using your own 16-bit 2-to-1 multiplexer. add16

Connect the modules together as shown in the diagram below. The provided module has the following declaration: add16

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

解法:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0]sum1,sum2,sum3;

wire sel;

add16 add161 (

.a(a[15:0]),

.b(b[15:0]),

.cin(0),

.sum(sum1),

.cout(sel)

);

add16 add162 (

.a(a[31:16]),

.b(b[31:16]),

.cin(0),

.sum(sum2),

.cout()

);

add16 add163 (

.a(a[31:16]),

.b(b[31:16]),

.cin(1),

.sum(sum3),

.cout()

);

always@(*) begin

case(sel)

0 : sum = {sum2,sum1};

1 : sum = {sum3,sum1};

endcase

end

endmodule

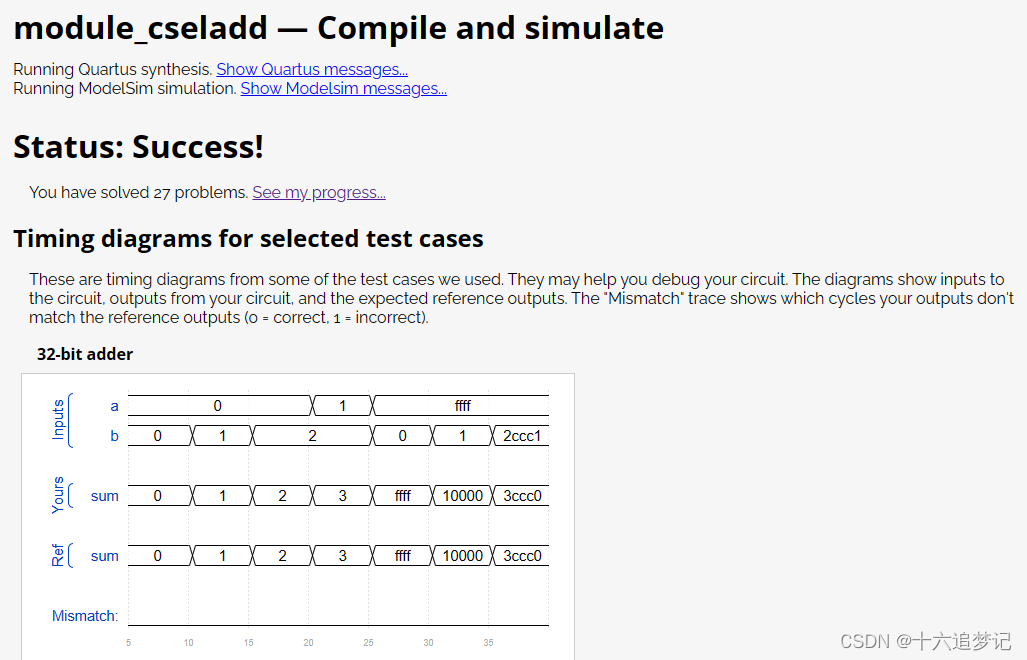

结果:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【INTEL(ALTERA)】Agilex7 FPGA Development Kit DK-DK-DEV-AGI027RBES 编程/烧录/烧写/下载步骤

- 华为无线ac双链路冷备和热备配置案例

- JavaScrip实现一个有时间限制的缓存类

- Ethercat“APWR配置从站地址”报文分析(0x0010:0x0011)

- acwing2241 礼物( FFT)

- JavaScript DOM表单相关操作之相关案例

- OpenCV4 工业缺陷检测的六种方法

- 在Java中正确使用Optional

- odoo16 产品变体之体验

- Mybatis配置-对象工厂(objectFactory)