Verilog 高级教程笔记——持续更新中

发布时间:2024年01月09日

Verilog advanced tutorial

转换函数

| 调用系统任务 | 任务描述 |

|---|---|

| int_val = $rtoi( real_val ) ; | 实数 real_val 转换为整数 int_val 例如 3.14 -> 3 |

| real_val = $itor( int_val ) ; | 整数 int_vla 转换为实数 real_val 例如 3 -> 3.0 |

| vec_val = $realtobits( real_val ) ; | 实数转换为多位宽的寄存器向量 寄存器内按照 IEEE-754 标准存储双精度浮点型数据 |

| real_val = $bitstoreal( vec_val ) ; | 多位宽的寄存器向量转换为实数 |

real 型变量的产生或转换过程,都应该遵循 IEEE Std 754-1985 [B1] 标准。

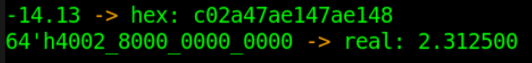

利用 $realtobits 与 $bitstoreal 对数据进行转换:

- 实例

//real, bits*

reg [63:0] num_bits ;

initial begin

num_bits = 64'h4002_8000_0000_0000 ;

$display("-14.13 -> hex: %h", $realtobits(-13.14));

$display("64'h4002_8000_0000_0000 -> real: %f", $bitstoreal(num_bits));

end

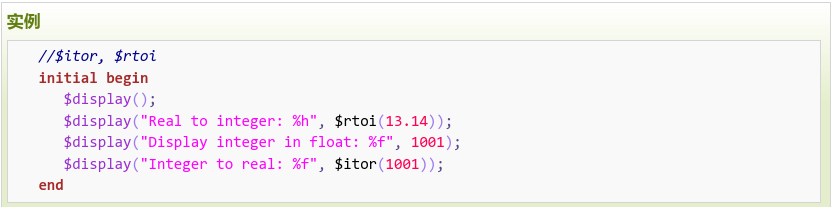

利用 $itor 与 $rtoi 对数据进行格式转换:

由以下仿真 log 可知,$rtoi 做实数(13.14)向整数(4’hd)的转换时,只截了取整数部分。$itor 做整数 (1001) 向实数(1001.000000)的转换时,似乎没有什么变化。

其实,$rtoi 与 $itor 的功能是改变变量的存储方式。

例如 14 以整数型变量储存时,表示方法为 32’h1110,而如果以实数型变量存储,则表示方法为 64h402c_0000_0000_0000。

Display system tasks

| System tasks | Description |

|---|---|

| $display | To display strings, variables, and expressions immediately in the active region.立即在活动区域中显示字符串、变量和表达式。 |

| $monitor | To monitor signal values upon its changes and executes in the postpone region.监视信号值的变化并在延迟区域执行。 |

| $write | To display strings, variables, and expressions without appending the newline at the end of the message and executing in the active region.显示字符串、变量和表达式,而不在消息末尾附加换行符并在活动区域中执行。 |

| $strobe | To display strings, variables, and expressions at the end of the current time slot i.e. in the postpone region.在当前时间段的末尾(即推迟区域)显示字符串、变量和表达式。 |

显示系统任务使用各种格式说明符来打印值

| Format specifiers | Description |

|---|---|

| %d or %D | To display variables in decimal |

| %b or %B | To display variables in binary |

| %h or %H | To display variables in hexadecimal |

| %o or %O | To display variables in octal |

| %c or %C | To display ASCII character |

| %s or %S | To display string |

| %t or %T | To display the current time |

| %f or %F | To display real numbers in decimal format. (Ex. 3.14) |

| %e or %E | To display real numbers in scientific format. (Ex. 2e20) |

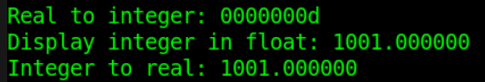

Difference between $display and $monitor

- $monitor 可以连续监视提到的变量或信号值的变化,而 $display 在调用时打印提到的变量或信号值。

- $monitor 只能调用一次,而 $display 可以调用多次。

- 如果多个 $monitor 任务调用了,则仅最后一个 $monitor 语句将处于活动状态,并且先前的语句将被覆盖。

module display_tb;

reg [3:0] d1, d2;

initial begin

d1 = 4; d2 = 5;

#5 d1 = 2; d2 = 3;

end

initial begin

$display("At time %0t: {$display A} -> d1 = %0d, d2 = %0d", $time, d1, d2);

$monitor("At time %0t: {$monitor A} -> d1 = %0d, d2 = %0d", $time, d1, d2);

$write("At time %0t: {$write A} -> d1 = %0d, d2 = %0d", $time, d1, d2);

$strobe("At time %0t: {$strobe A} -> d1 = %0d, d2 = %0d", $time, d1, d2);

#5;

$display("At time %0t: {$display B} -> d1 = %0d, d2 = %0d", $time, d1, d2);

// $monitor is missing -> Observe print for $monitor A

$write("At time %0t: {$write B} -> d1 = %0d, d2 = %0d", $time, d1, d2);

$strobe("At time %0t: {$strobe B} -> d1 = %0d, d2 = %0d", $time, d1, d2);

end

endmodule

Output:

Simulation controlling system tasks

| $reset | resets the simulation back to time 0; |

|---|---|

| $stop | It is used to stop or suspend the running simulation. It is generally used for debugging purposes and puts the simulation mode in interactive mode so that designers can examine signal values. |

| $finish | It is used to terminate the simulation. |

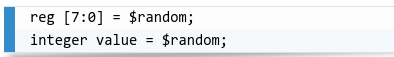

Random number generator system task

$random – It returns a 32-bit signed integer i.e. it can be positive or negative integer.

$time, $stime, $realtime

它们分别以 64 位整数、32 位整数和实数形式返回当前模拟时间。

$scope, $showscope

$scope(hierarchy_name) 将当前分层范围设置为hierarchy_name。 $showscopes(n) 列出当前范围内(及以下,如果 n 设置为 1)的所有模块、任务和块名称。

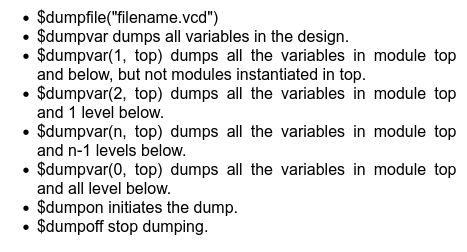

$dumpfile, $dumpvar, $dumpon, $dumpoff, $dumpall

这些可以将变量变化转储到像德彪西这样的模拟查看器。转储文件能够转储模拟中的所有变量。这对于调试来说很方便,但可能会很慢。

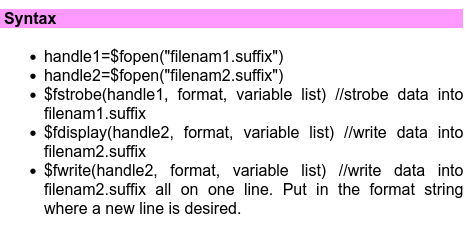

$fopen, $fdisplay, $fstrobe $fmonitor and $fwrite

这些命令更有选择性地写入文件。

- $fopen 打开一个输出文件并为打开的文件提供一个句柄以供其他命令使用。

- $fclose 关闭文件并允许其他程序访问它。

- $fdisplay 和 $fwrite 每当执行时都会将格式化数据写入文件。它们是相同的,只是 $fdisplay 在每次执行后插入一个新行,而 $write 则不然。

- $strobe 在执行时也会写入文件,但它会等到时间步中的所有其他操作完成后才写入。因此初始#1 a=1; b = 0;

- $fstrobe(hand1, a,b); b=1;将为a和b写1 1。

- 只要 $monitor 的任何参数发生更改,就会写入文件。

$signed(expr) or $unsigned(expr)

- 这些调用的返回值与输入值的大小相同。

- 无论之前的符号如何,返回值的符号都是强制的。

$readmemb and $readmemh

- 使用 $readmemb 进行二进制表示。

- 使用 $readmemh 进行十六进制表示。

- 使用索引参数来避免 Vivado 综合和模拟器之间的行为冲突。

$readmemb("rams_20c.data",ram, 0, 7);

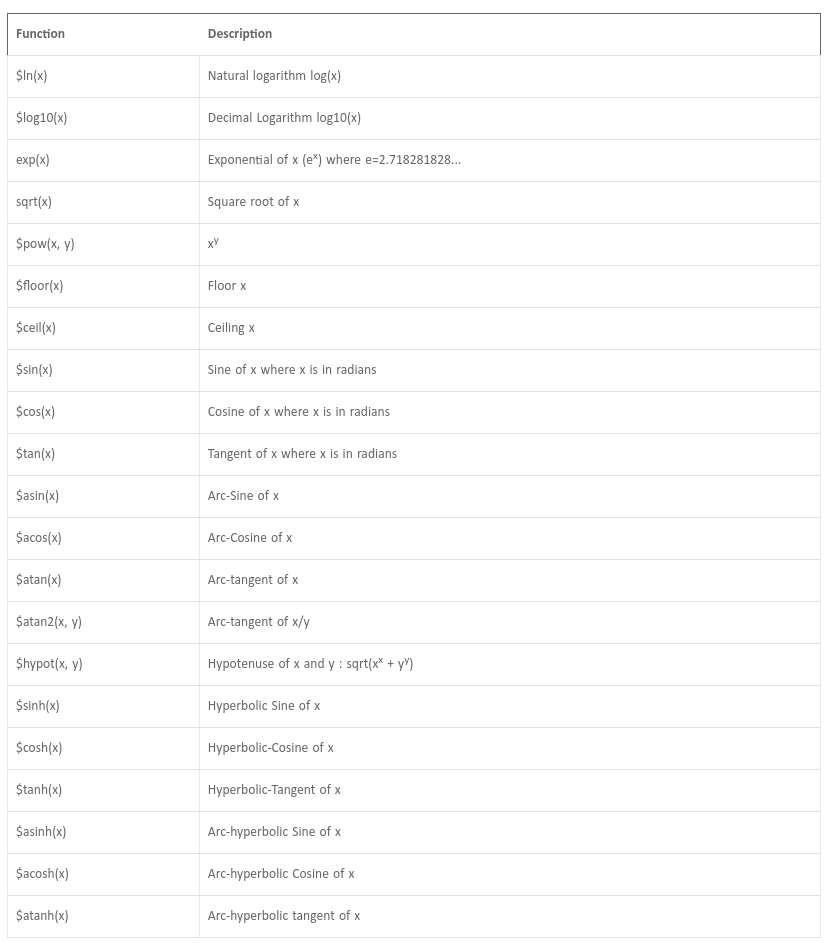

Real Math functions

Synthesizable and Non-Synthesizable Verilog constructs

| Synthesizable | Non-Synthesizable | |

|---|---|---|

| Basic | Identifiers, escaped identifiers, Sized constants (b, o, d, h), Unsized constants (2’b11, 3’07, 32’d123, 8’hff), Signed constants (s) 3’bs101, module, endmodule, macromodule, ANSI-style module, task, and function port lists —— 标识符、转义标识符、大小常量 (b、o、d、h)、未大小常量 (2’b11、3’07、32’d123、8’hff)、有符号常量 (s) 3’bs101、module、endmodule、宏模块、ANSI 样式模块、任务和函数端口列表 | system tasks, real constants |

| Data types | wire, wand, wor, tri, triand, trior, supply0, supply1, trireg (treated as wire), reg, integer, parameter, input, output, inout, memory(reg [7:0] x [3:0] `;), N-dimensional arrays, | real, time, event, tri0, tri1 |

| Module instances | Connect port by name, order, Override parameter by order, Override parameter by name, Constants connected to ports, Unconnected ports, Expressions connected to ports, ——按名称、顺序连接端口、按顺序覆盖参数、按名称覆盖参数、连接到端口的常量、未连接的端口、连接到端口的表达式、 | Delay on built-in gates 内置门延迟 |

| Generate statements | if,case,for generate, concurrent begin end blocks, genvar, | |

| Primitives | and, or, nand, nor, xor, xnor,not, notif0, notif1, buf, bufif0, bufif1, tran, | User defined primitives 用户定义的原语 (UDPs), table, pullup, pulldown, pmos, nmos, cmos, rpmos, rnmos, rcmos, tranif0, tranif1, rtran, rtranif0, rtranif1, |

| Operators and expressions | +, - (binary and unary) | |

| Bitwise operations | &, |, ^, ~^, ^~ | |

| Reduction operations | &, |, ^, ~&, ~|, ~^, ^~, !, &&, || , ==, !=, <, <=, >, >=, <<, >>, <<< >>>, {}, {n{}}, ?:, function call | === , ! == |

| Event control | event or, @ (partial), event or using comma syntax, posedge, negedge (partial), | Event trigger (->), delay and wait (#) |

| Bit and part selects | Bit select, Bit select of array element, Constant part select, Variable part select ( +:, -`:), Variable bit-select on left side of an assignment ——位选择、数组元素的位选择、常量部分选择、变量部分选择(+:、-:)、赋值左侧的变量位选择 | |

| Continuous assignments | net and wire declaration, assign | Using delay |

| Procedural blocks | always (exactly one @ required), | initial |

| Procedural statements | ;, begin-end, if-else, repeat, case, casex, casez, default, for-while-forever-disable(partial), | fork, join |

| Procedural assignments | blocking (=), non-blocking (<=) | force, release |

| Functions and tasks | Functions, tasks | |

| Compiler directives | `define, `undef,`resetall, `ifndef, `elsif, `line, `ifdef, `else, `endif, `include |

文章来源:https://blog.csdn.net/qq_46264636/article/details/135489869

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!