【SV的激励时序与接口_2023.12.26】

发布时间:2023年12月27日

SV的激励时序

竞争冒险

竞争:由于每条途径延迟时间不同

冒险:竞争有先有后产生毛刺

解决方法:

仿真时,一般采用加#0延时,多个#0无法判定→非阻塞赋值

层次化事件队列

仿真器对一个timeslot内语句的执行是按照一定的时间顺序执行的,sv对其进行了更丰富的区域划分

sv中,为了区分验证和RTL事件,tb代码都包含在program模块中,program内部不能包含module、interface、program

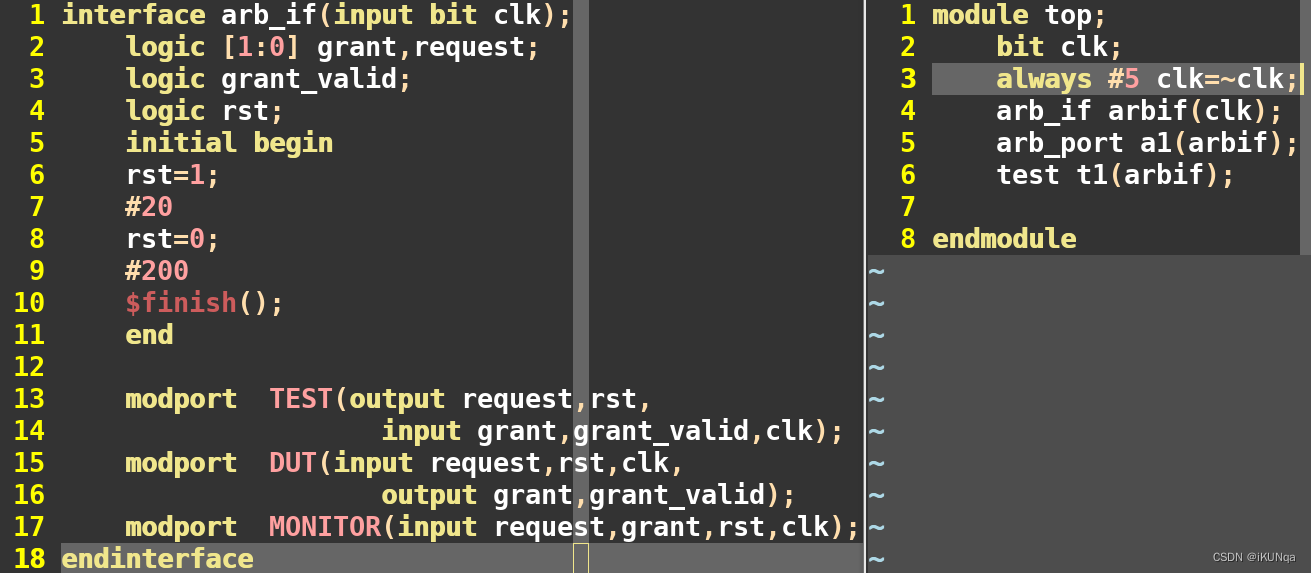

SV的interface(可综合)

理解

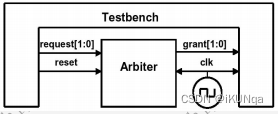

无interface时,tb是rtl的top

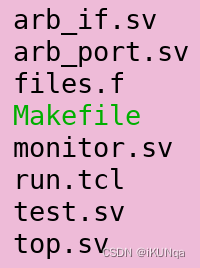

有interface时,tb和rtl同级,还可以延伸出更多的同级文件,top层作为时钟发生器生成时钟激励

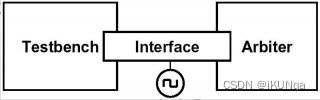

SV使用接口来连接不同模块,它连接了DUT和验证平台

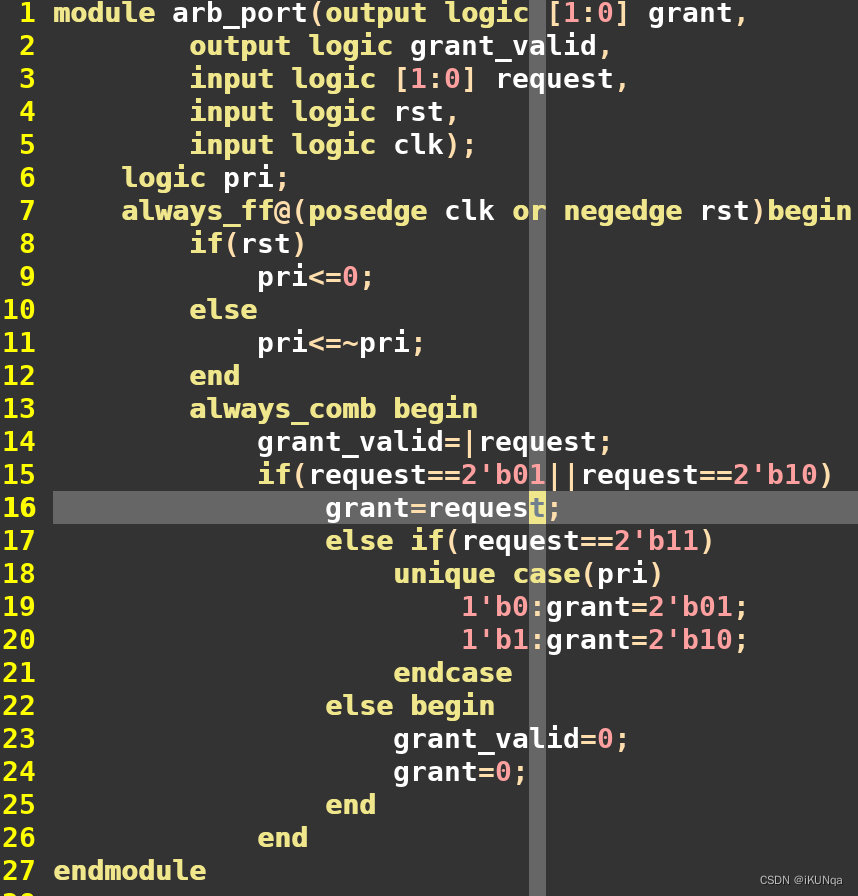

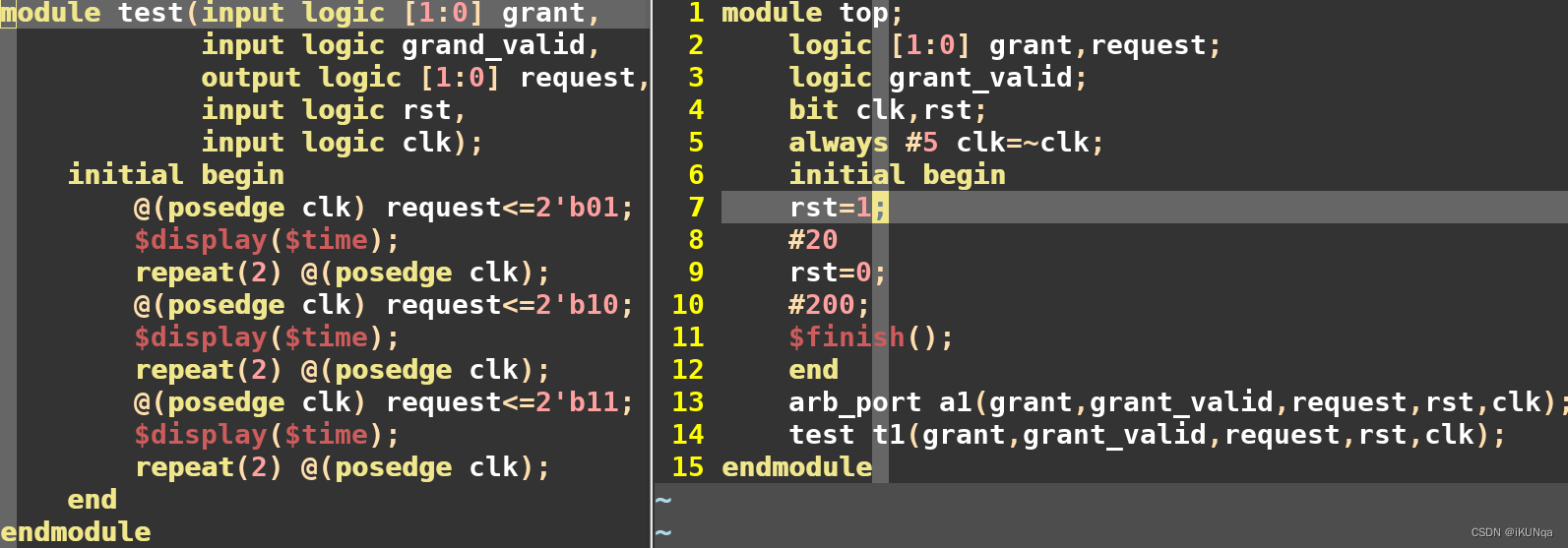

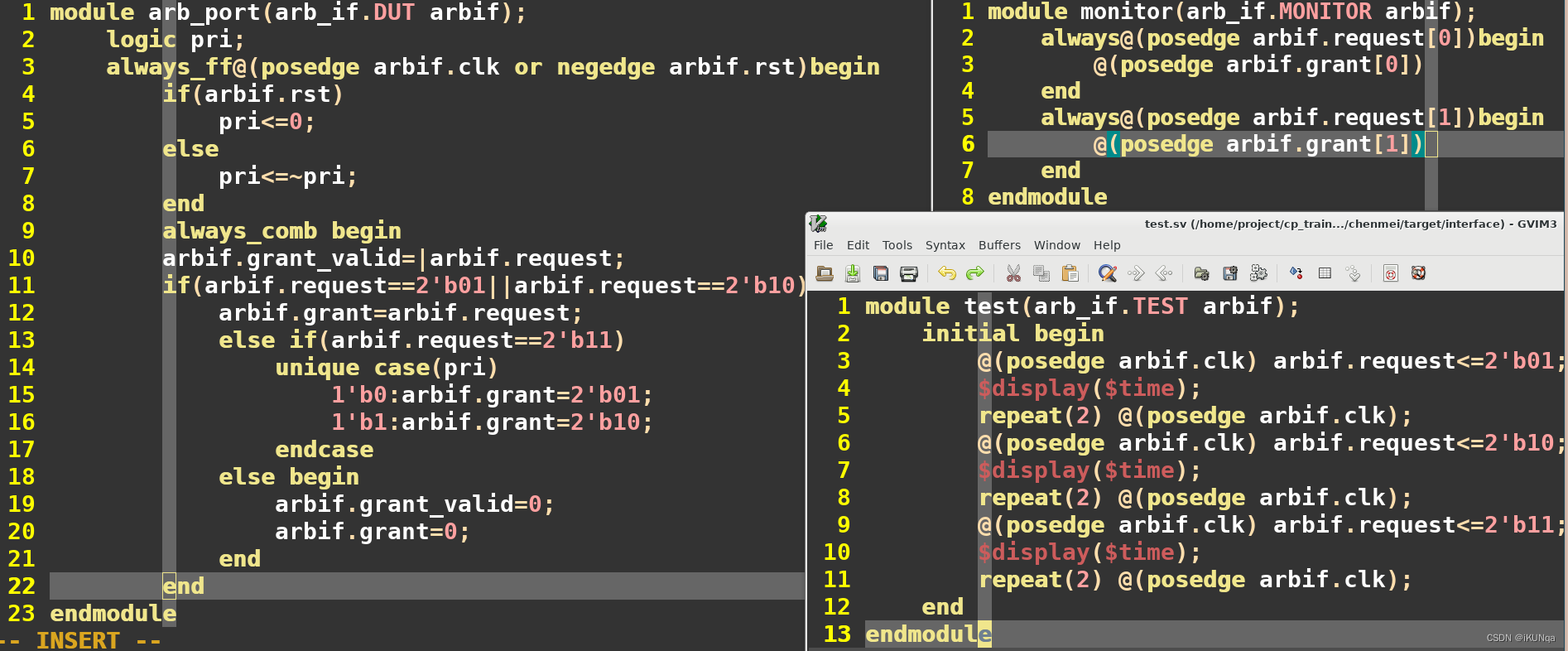

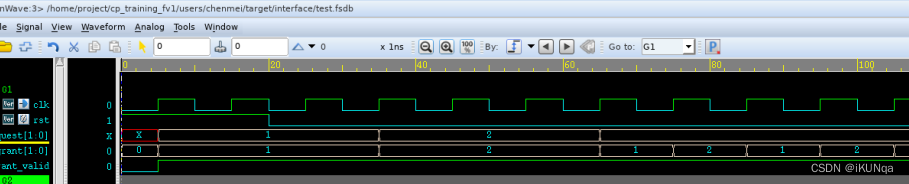

使用接口的仲裁器和使用接口的测试平台

interface连接接口和端口,管理端口

modport

为了指定方向,使用modport将接口中的信号分组

端口连接和接口连接的对比

端口

结果如接口中相同

接口

要注意写$finish();,否则仿真卡顿

文章来源:https://blog.csdn.net/xiaotong121/article/details/135251526

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 软件测试大神教你如何做好需求管理和用例设计逻辑映射(三)

- vue-qr 下载保存二维码

- 【离散数学】xjtu版离散复习攻略

- mysql:1153 Got a packet bigger than ‘max_allowed_packet’ bytes的错误

- wy的leetcode刷题记录_Day74

- IDEA 2023.3.2 安装教程

- 多核调度实验设计

- Axure的元件库的使用以及详细案例

- 如何让CHAT使用python绘制概率密度图像?

- springboot学生信息管理系统