NOC CCN NIC CCI总线

1. 前言

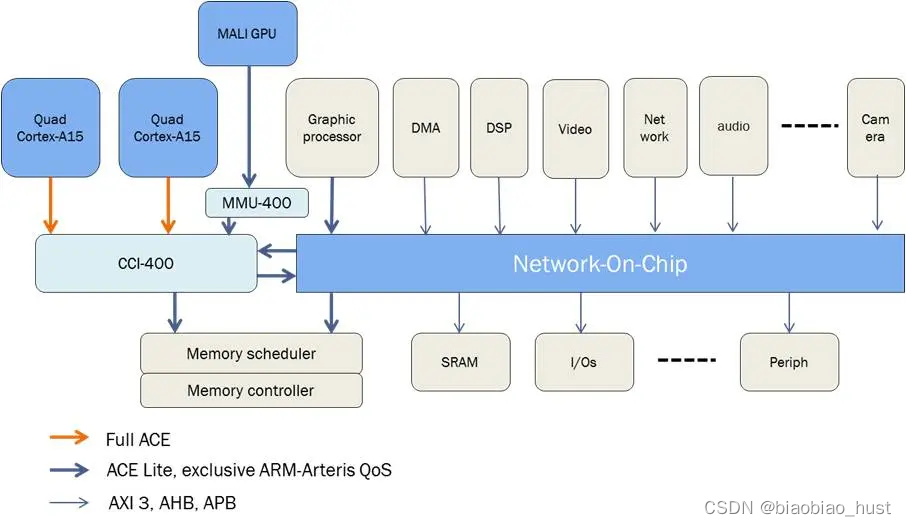

????????在ARM当前所有的总线产品里,根据拓扑的不同可以分为三类产品:NIC/CCI系列是交叉矩阵的(Crossbar),CCN系列是基于环状总线的(Ring),NoC系列是网状总线(Mesh)。他们各有特点,适合不同场景。一般手机芯片上使用交叉矩阵,网络处理器和服务器上使用环状网络,而网状拓扑也被大量应用于手机芯片。

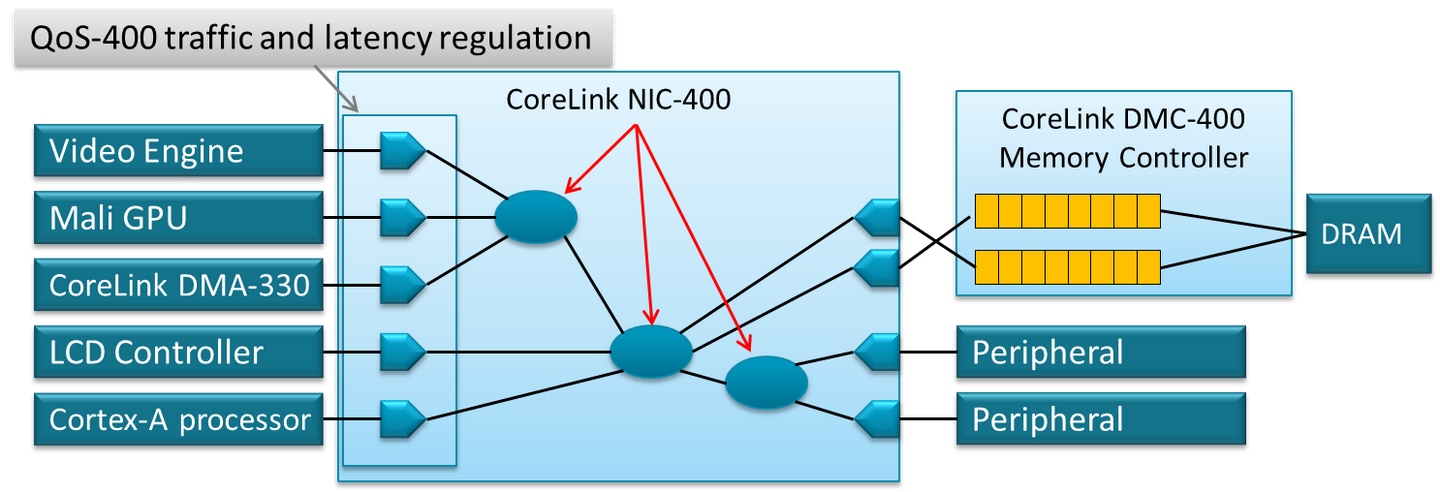

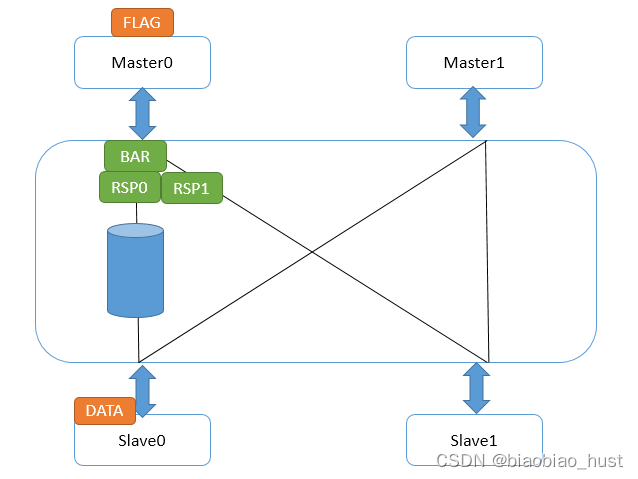

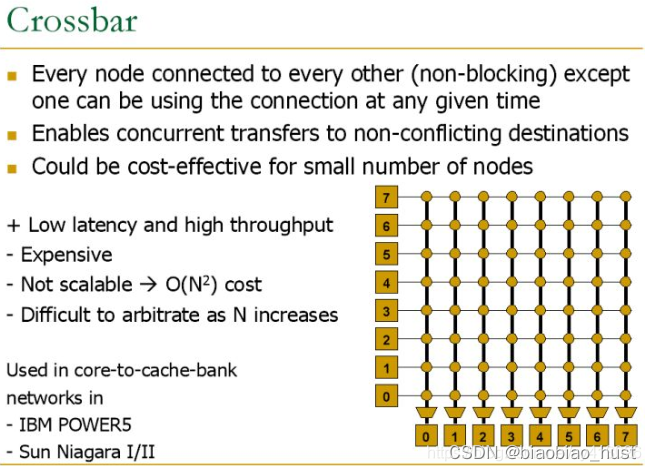

????????交叉矩阵连接的主从设备数量受到限制,但是效率最高,读写请求可以在1到2个周期内就直达从设备。如下图所示,这就是一个5x4的交叉矩阵:

????????在28纳米制程上,5x4的配置下,这个总线的频率可以跑到300Mhz。如果进一步增加主从对数量,那么由于扇出增加,电容和走线增加,就必须通过插入更多的寄存器来增加频率。但这样一来,从主到从的延迟就会相应增加。要想进一步提高到频率,要么使用更好的工艺,要么插入寄存器,这样,读写延时就会增加。要知道处理器访问二级缓存的延迟通常也不过10多个处理器周期。所以,要达到更高的频率,支持更多的主从设备,就需要引入环状总线CCN系列,如下图:

????????CCN总线上的每一个节点,除了可以和相邻的两个节点通讯之外,还可以附加两个节点组件,比如处理器组,三级缓存,内存控制器等。在节点内部,还是交叉的,而在节点之间,是环状的。这样使得总线频率在某种程度上摆脱了连接设备数量的限制(当然,还是受布线等因素的影响)。当然,代价就是节点间通讯更大的平均延迟。为了减少平均延迟,可以把经常互相访问的节点放在靠近的位置。

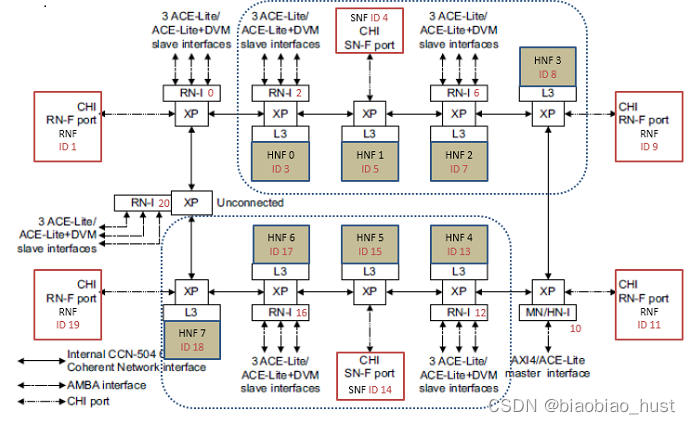

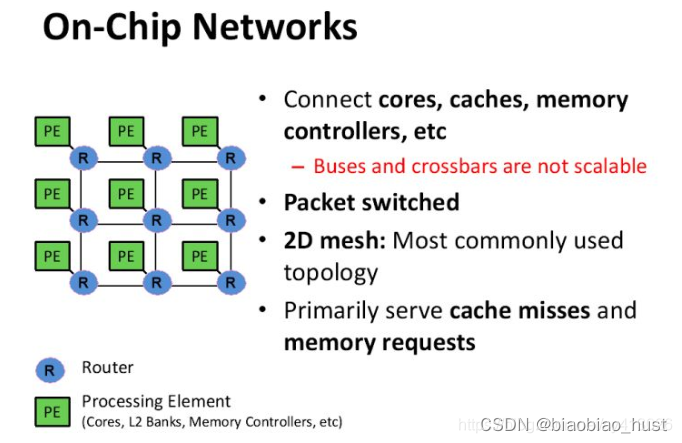

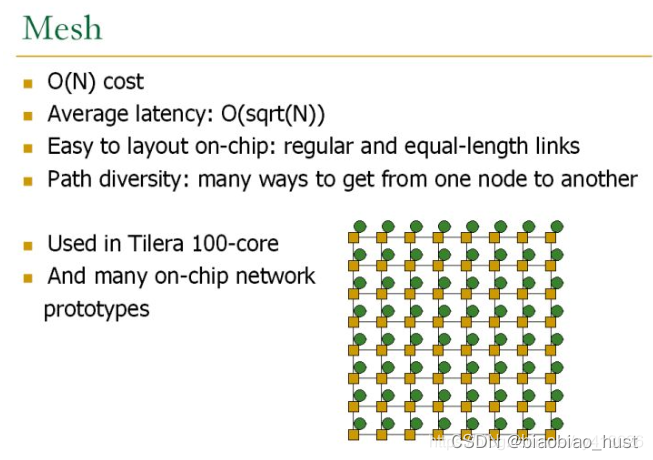

????????在有些系统里,要求连接更多的设备,并且,频率要求更高。此时环状总线也不够用了。这时就需要NoC出马了,如下图:

????????这个图中,刚才提到的交叉矩阵,可以作为整个网络的某部分。而连接整个系统的,是位于NoC内的节点。每个节点都是一个小型路由,它们之间传输的,是异步的包。这样,就不必维持路由和路由之间很大数量的连线,从而提高频率,也能支持更多的设备。当然,坏处就是更长的延迟。并且它所连接每个子模块之间,频率和拓扑结构可以是不同的。可以把需要紧密联系的设备,比如CPU簇,GPU放在一个子网下减少通讯延迟。

1.1 NIC/NOC/CCI的简单比较

? ? ? ? NIC crossbar 结构,特点是全互联switch,容量高,latency低,并发性好。缺点是可扩展性差,适用于输入输出数目比较小的情况。

? ? ? ? NOC是类似路由的一种结构,特点是可扩展性好,缺点是并行性差,结构复杂,需要路由协议。适用于连接非常多个处理单元的情况。 ?

? ? ? ? NIU准确的定义应该是BIU,也就 bus interface unit.用于连接网络节点和处理单元, NIU/BIU不是必须的,如果两种协议一致,就不需要这个了。

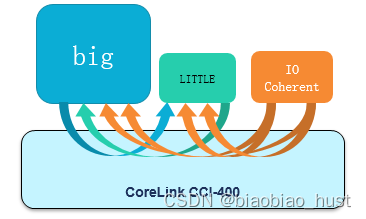

? ? ? ? CCI是保证多核处理单元之间cache 内容一致性的互联结构。

2. 硬件一致性

2.1 CCI? ? ? ??

????????ARM引入了几个支持硬件一致性的总线,下图是第一代方案CCI400:

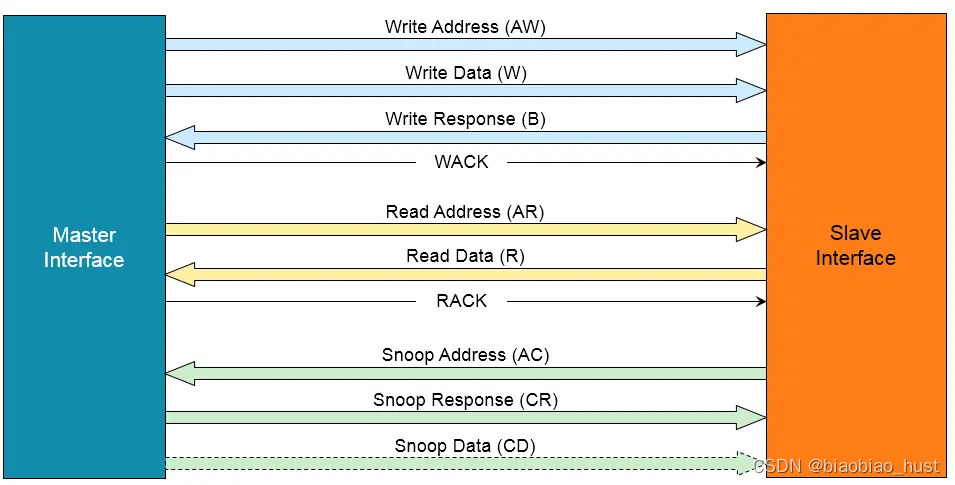

????????CCI400是怎么做到硬件一致性的呢?简单来说,就是处理器组C1,发一个包含地址信息的特殊读写的命令到总线,然后总线把这个命令转给另一个处理器组C2。C2收到请求后,根据地址逐步查找二级和一级缓存,如果发现自己也有,那么就返回数据或者做相应的缓存一致性操作,这个过程称作snooping(监听)。在这个过程中,C2中的处理器核心并不参与,所有的工作由缓存和总线接口单元BIU等部件来做。为了符合从设备不主动发起请求的定义,需要两组主从设备,每个处理器组占一个主和一个从。这样就可以使得两组处理器互相保持一致性。而有些设备如DMA控制器,它本身不包含缓存,也不需要被别人监听,所以它只包含从设备,如上图桔黄色的部分。在ARM的定义中,具有双向功能的接口被称作ACE,只能监听别人的称作ACE-Lite。它们除了具有AXI的读写通道外,还多了个监听通道,如下图:

????????多出来的监听通道,同样也有地址(从到主),回应(主到从)和数据(主到从)。每组信号内都包含和AXI一样的标志符,用来支持多OT。如果在主设备找到数据(称为命中),那么数据通道会被使用,如果没有,那告知从设备未命中就可以了,不需要传数据。由此,对于上文的DMA控制器,它永远不可能传数据给别人,所以不需要数据组,这也就是ACE和ACE-Lite的主要区别。

????????我们还可以看到,在读通道上有个额外的线RACK,它的用途是,当从设备发送读操作中的数据给主,它并不知道何时主能收到这个数据,因为我们说过插入寄存器会导致总线延迟变长。万一这个时候,对同样的地址A,它需要发送新的监听请求给主,就会产生一个问题:主是不是已经收到前面发出的地址A的数据了呢?如果没收到,那它可能会告知监听未命中。但实际上地址A的数据已经发给主了,它该返回命中。加了这个RACK后,从设备在收到主给的确认RACK之前,不会发送新的监听请求给主,从而避免了上述问题。写通道上的WACK同样如此。

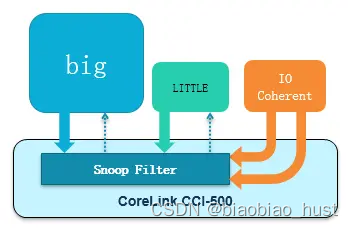

? ? ? ? 问题:给定一个地址,并不知道它是不是在其他处理器的缓存内,所以无论如何都需要额外的监听动作。当未命中的时候,这个监听动作就是多余的,这个多余的动作就意味着额外的延迟。

????????CCI总线的设计者们还使用了一个新的方法来提高性能。他们在总线里加入一个监听过滤器(Snoop Filter)。这其实也是一块缓存(TAG RAM),把它所有处理器组内部一级二级缓存的状态信息都放在里面。这样做的好处就是,监听请求不必发到各组处理器,在总线内部就可以完成,功耗也优于访问内存。它的代价是增加了一点缓存(一二级缓存的10%左右)。以上的想法在CCI500中实现,示意图如下:

3. 壁垒指令

????????和一致性相关的是访存次序和锁。假设我们有两个核C0和C1。当C0和C1分别访问同一地址A0,无论何时,都要保证看到的数据一致,这是一致性。然后在C0里面,它需要保证先后访问地址A0和A1,这称作访问次序,不需要锁,只需要壁垒指令。如果C0和C1上同时运行两个线程,当C0和C1分别访问同一地址A0,并且需要保证C0和C1按照先后次序访问A0,这就需要锁。所以,单单壁垒指令只能保证单核单线程的次序,多核多线程的次序需要锁。而一致性保证了在做锁操作时,同一变量在缓存或者内存的不同拷贝,都是一致的。

????????ARM的壁垒指令分为强壁垒DSB和弱壁垒DMB。强壁垒要求上一条读写指令完成后才能开始下一个请求,弱壁垒则只要求上一条读写指令发出请求后就可以继续下一条读写指令的请求,且只能保证,它之后的读写指令完成时,它之前的读写指令肯定已经完成了。显然,后一种情况性能更高,OT>1。但测试表明,多个处理器组的情况下,壁垒指令如果传输到总线,只能令整体系统性能降低,因此在新的ARM总线中是不支持壁垒的,必须在芯片设计阶段,通过配置选项告诉处理器自己处理壁垒指令,不要送到总线。但这并不影响程序中的壁垒指令,处理器会在总线之前把它过滤掉。

????????如果只需要保证读写次序,用弱壁垒;如果需要某个读写指令完成才能做别的事情,用强壁垒。以上都是针对普通内存类型。当我们把类型设成设备时,自动保证强壁垒。

3.1 CCI

? ? ? ? 在CCI总线中,首先,壁垒和读写一样,也是使用读写通道的,只不过它地址总是0,且没有数据。标志符也是有的,此外还有额外的2根线BAR0/1,表明本次传输是不是壁垒,是哪种壁垒。他是怎么传输的呢?

3.1.1 弱壁垒

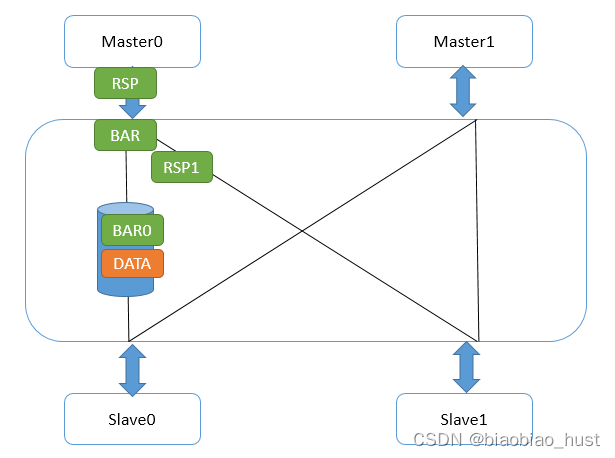

????????先看弱壁垒,如下图:

????????Master0写了一个数据data,然后又发了弱壁垒请求。CCI和主设备接口的地方,一旦收到壁垒请求,立刻做两件事,第一,给Master0发送壁垒响应;第二,把壁垒请求发到和从设备Slave0/1的接口。Slave1接口很快给了壁垒响应,因为它那里没有任何未完成传输。而Slave0接口不能给壁垒响应,因为data还没发到从设备,在这条路径上的壁垒请求必须等待,并且不能和data的写请求交换次序。这并不能阻挠Master0发出第二个数据,因为它已经收到它的所有下级(Master0接口)的壁垒回应,所以它又写出了flag。

????????此时,flag在Master0接口中等待它的所有下一级接口的壁垒响应。而data达到了Slave0后,壁垒响应走到了Master0接口,flag继续往下走。此时,我们不必担心data没有到slave0,因为那之前,来自Slave0接口的壁垒响应不会被送到Master0接口。这样,就做到了弱壁垒的次序保证,并且在壁垒指令完成前,flag的请求就可以被送出来。

3.1.2 强壁垒

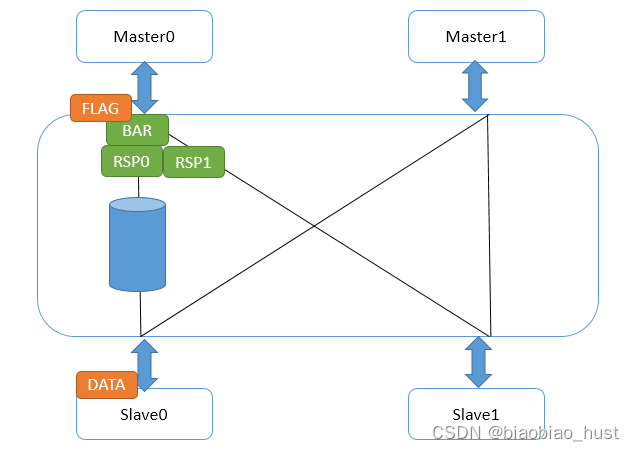

????????对于强壁垒指令来说,仅仅有一个区别,就是Master0接口在收到所有下一级接口的壁垒响应前,它不会发送自身的壁垒响应给Master0。这就造成flag发不出来,直到壁垒指令完成。如下图:

????????这样,就保证了强壁垒完成后,下一条读写指令才能发出请求。此时,强壁垒前的读写指令肯定是完成了的。

3.2 锁和原子操作

????????壁垒只是针对单核。在多核多线程时,哪怕使用了壁垒指令,也没法保证读写的原子性。解决办法有两个,一个是软件锁,一个是原子操作。原子操作有两种,一种是总线收到请求时,直接封掉整个总线,同时只有一个核能访问。这样效率很低。还有个方法是把锁的请求发送到对端设备,比如内存控制器,让他禁止别的核的访问,而总线依然可以运行,这样效率就高不少。

3.2.1 自旋锁

????????软件锁中有个自旋锁,能用一个ARM硬件机制exclusive access来实现。当使用特殊指令对一个地址写入值,相应缓存行上会做一个特殊标记,表示还没有别的核去写这行缓存。然后下条指令读这个行,如果标记没变,说明写和读之间没有人打扰,那么就拿到锁了。如果变了,那么回到写的过程重新获取锁。由于缓存一致性,这个锁变量可以被多个核与线程使用。当然,过程中还是需要壁垒指令来保证次序。

4. NIC-400

????????CoreLink NIC-400网络互连是高度可配置的,能够创建一个完整的高性能,优化和amba兼容的网络基础设施。CoreLink NIC-400网络互联有多种配置。它们的范围可以从单个桥接组件,例如AHB到AXI协议转换桥接,到一个复杂的互连,包括多达128个主和64个从AMBA协议。????????

????????NIC是crossBar结构的总线互联,一般用在主从设备较少的情况下,这种情况下NIC的效率很高,在1到2个时钟周期数据就能到达从设备。所以常看到NIC被用在子系统内部互联多个apb的slave。NIC是只支持amba的协议,不像NOC需要专门的路由协议。ARM总线产品还有CCI(CrossBar),CCN(Ring),NOC(Mesh)三类。

5. NOC

????????NOC解决方案的目标针对采用异步设计方法(即在一块芯片上采用多个时钟及数百个IP块)的设计。鉴于此,Arteris公司开发出专用的片上以及基于分组的NTTP(NOC处理与传输协议)。而由网络接口单元 (NIU)、数据包传输单元及物理链路组成的Danube库,则包含用于执行这种协议的必要元素。

5.1?NOC协议和简单结构

R:Router,NOC内部重要节点,用于路由和流量控制,有的地方叫做SWITCH。

NI:Network InterFace

NIU:是NI与AMBA接口的转换和异步处理【异步处理可以在NIU、LINK和switch做】

LINK:连接NIU、Router/SWITCH的物理线路,上面可以有pipe和async组件

NTTP:NoC Transaction and Transport Protocol,NOC传输和处理协议

????????NOC采用基于数据包的传输和处理协议。为了完成传输和处理,NTTP包含了很多子协议:

1.路由协议:确定数据包在网络中的传输路径,使数据包可以从源节点到目标节点进行路由。常见的路由算法有Dijkstra算法、Floyd算法、最短路径算法等。

2.拥塞控制协议:当网络中的某些部分过载时,拥塞控制协议将采取措施防止网络拥塞,以确保数据包的可靠传输。常见的拥塞控制算法有流控制、拥塞避免、拥塞检测等。

3.流量控制协议:在NoC中,流量控制协议用于控制不同节点之间的数据传输速率,以避免网络拥塞和数据丢失。流量控制协议通常使用缓冲区来存储数据包,并在必要时限制传输速率。

4.错误控制协议:错误控制协议用于检测和纠正网络中发生的错误,以确保数据的可靠传输。常见的错误控制协议有检验和、循环冗余检测等。

5.安全协议:安全协议用于保护NoC中传输的数据和信息的安全性,防止网络攻击和数据泄露。安全协议通常使用加密和解密技术来确保数据的机密性和完整性。

????????所以说NOC在流控,QOS和security及功能安全都做的很好,这些是NIC所没有的。

6. 互联结构

6.1?共享总线 即 BUS结构

????????Bus是最简单的互联,适合small system,当connected nodes太多时,若多个node同时通信,很容易产生contention,bandwidth 太小。所以Bus只适合小系统,一般十个以下的互联设备。

6.2?CrossBar

????????crossbar也是一种常用互联机制,每个node能与其他node直接互联,所以low latency and high throughput.,但 not scalable(可扩展性差)。所以Crossbar适合不太大的系统,一般用于几个到十几个connected nodes 的系统。

6.3 NOC

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 175.【2023年华为OD机试真题(C卷)】API集群负载统计(遍历和条件判断实现Java&Python&C++&&JS)

- 初识Mybatis框架技术(上)

- 如何预防服务器IP被劫持,危害有什么?

- 三种连接因特网的方式

- Linux操作系统—文件和目录管理命令

- Postman中文文档——安装与更新

- 五款出色的产品原型设计工具推荐

- 轻量级Python IDE使用(三)——函数

- JS-WebAPIs- Window对象(五)

- ios ipa包上传需要什么工具