西南科技大学数字电子技术实验六(智力竞赛抢答器的设计及FPGA实现)FPGA部分

一、实验目的

进一步掌握D触发器,分频电路,多谐振荡电器,CP时钟脉冲元等单元电路的设计。

二、实验原理

?

?

三、程序清单(每条语句必须包括注释或在开发窗口注释后截图)

逻辑代码:

module contend

(

?????? input wire clk,rst,start,

?????? input wire[3:0]k,

?????? output reg[3:0]led

);

always@(posedge clk or negedge rst)

?????? begin

?????????????

????????????? if(!rst)

???????????????????? led[3:0] = 4'b1111;

????????????? else if(start)

???????????????????? case(k)

??????????????????????????? 4'b0000 : led = 4'b1111;

??????????????????????????? 4'b0001 : led = 4'b1110;

??????????????????????????? 4'b0010 : led = 4'b1101;

??????????????????????????? 4'b0100 : led = 4'b1011;

??????????????????????????? 4'b1000 : led = 4'b0111;

???????????????????? endcase

?????? end

endmodule

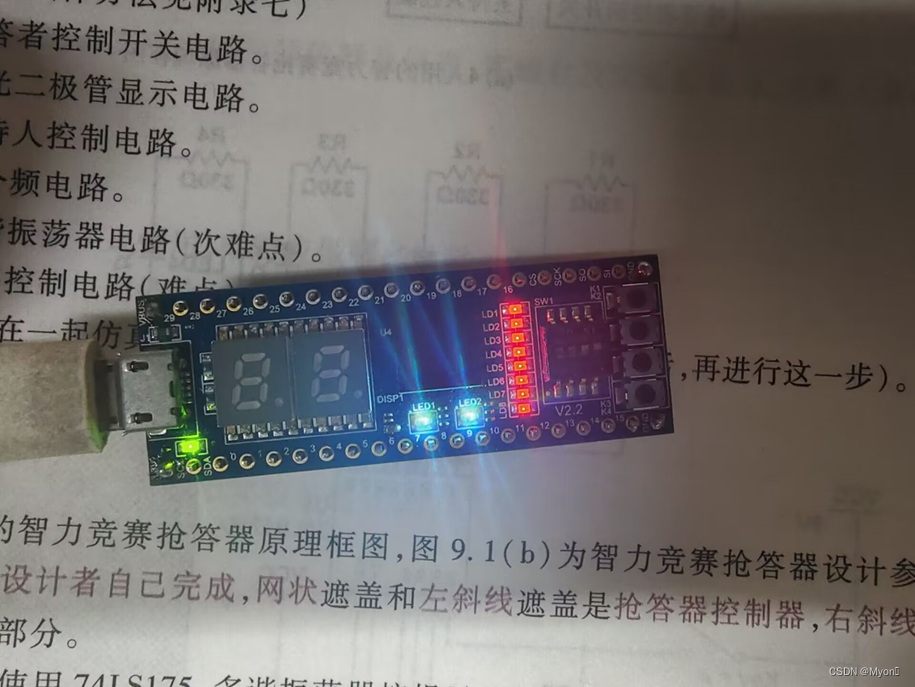

四、综合、管脚分配、生成输出文件、下载(所有步骤截图)

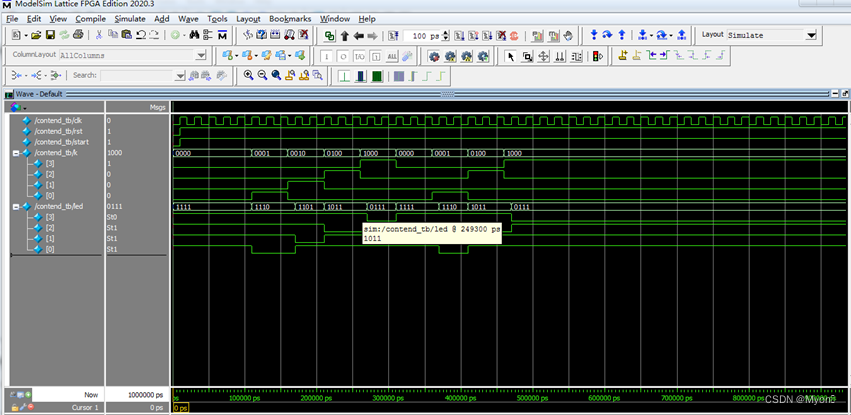

五、仿真程序清单、波形(波形截图必做,截图!)

仿真代码:

`timescale 1ns/100ps

module contend_tb;

? reg clk;

? reg rst;

? reg start;

? reg[3:0]k;

? wire[3:0]led;

? initial

? begin

? clk = 0;

? rst = 0;

? start = 0;

? k=0;

? #10;

? rst = 1;

? start = 1;

? #50;

? k = 4'b0000;

? #50;

? k = 4'b0001;

? #50;

? k = 4'b0010;

? #50;

? k = 4'b0100;

? #50;

? k = 4'b1000;

? #50;

? k = 4'b0000;

? #50;

? k = 4'b0001;

? #50;

? k = 4'b0010;

? $50;

? k = 4'b0100;

? #50;

? k = 4'b1000;

end

always#10 clk=~clk;

contend u1

(

? .clk(clk),

? .rst(rst),

? .start(start),

? .k(k),

? .led(led)

);

Endmodule

六、思考与体会

通过本次实验,我进一步理解了D触发器,分频电路,多谐振荡电器,CP时钟脉冲元等单元电路的设计,能自己设计出竞赛抢答器,并且用FPGA实现了本次实验的内容,经过验证,与仿真结果一致,满足抢答器的基本功能,在实验练习的巩固下,我对相关的理论知识有了更深刻的记忆和运用。

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!