《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(17)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第1章 PCI总线的基本知识(16)

1.4?PCI总线的中断机制

PCI总线使用INTA#、INTB#、INTC#和INTD#信号向处理器发出中断请求。这些中断请求信号为低电平有效,并与处理器的中断控制器相连接。自PCI体系结构中,这些中断信号属于边带信号(Sidebane Signals),PCI总线规范并没有明确规定在一个处理器系统中如何使用这些信号,因为这些信号之于PCI总线是可选信号。PCI设备还可以使用MSI机制向处理器提交中断请求,而不使用这组中断信号。

1.4.1 中断信号与中断控制器的连接关系

不同的处理器使用的中断控制器不同,如x86处理器使用APIC(Advanced Programmable Interrupt Controller)中断控制器,而PowerPC处理器使用MPIC(Multiprocessor Interrupt Controller)中断控制器。这些中断控制器都提供了一些外部中断请求引脚IRQ_PINx#。外部设备,包括PCI设备可以使用这些引脚向处理器提交中断请求。

但是PCI总线规范并没有规定PCI设备的INTx信号如何与中断控制器的IRQ_PINx#信号相连,这为系统软件的设计带来了一定的困难。为此,系统软件使用中断路由表存放PCI设备的INTx信号与中断控制器的连接关系。在x86处理器系统中,BIOS可以提供这个中断路由表,而在PowerPC处理器中,Firmware也可以提供这个中断路由表。

在一些简单的嵌入式处理器系统中,Firmware并没有提供中断路由表,系统软件开发者需要事先了解PCI设备的INTx信号与中断控制器的连接关系。此时外部设备与中断控制器的连接由硬件设计人员指定。

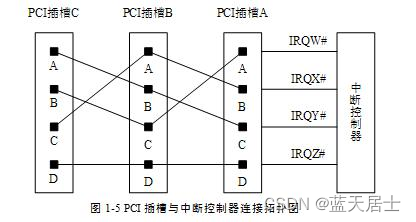

假设在一个处理器系统中,共有3个PCI插槽(分别为PCI插槽A、B和C),这些PCI插槽与中断控制器的IRQ_PINx引脚(分别为IRQW#、IRQX#、IRQY#和IRQZ)可以按照图1-5所示的拓扑结构进行连接。

采用上图所示的拓扑结构时,PCI插槽A、B、C的INTA#、INTB#和INTC#信号将分散连接到中断控制器的IRQW#、IRQX#和IRQY#信号,而所有的INTD#信号将共享一个IRQZ#信号。采用这种连接方式时,整个处理器系统使用的中断请求信号,其负载较为均衡。而且这种连接方式保证了每一个插槽的INTA#信号都与一根独立的INTA#信号都与一根独立的IRQx#信号对应,从而提高了PCI插槽中断请求的效率。

在一个处理器系统中,多数PCI设备仅使用INTA#信号,很少使用INTB#和INTC#信号,而INTD#信号更是极少使用。在PCI总线中,PCI设备配置空间的Interrupt Pin寄存储器记录该设备究竟使用哪个INTx信号。

更多内容请看下回。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Java jar文件变更jar或者xml方法

- 分布式Erlang/OTP(学习笔记)(一)

- 2024 Nomachine 最简安装与使用指南

- FileZille的使用

- 基于grpc从零开始搭建一个准生产分布式应用(10) - Dao逻辑实现

- 逻辑斯蒂回归

- 安装Redis+Redis设置成windows下的服务+windows无法启动Redis服务,报错误1067:进程意外终止,解决方法

- 2023-12-02 青少年软件编程(C语言)等级考试试卷(三级)解析

- 排序算法7----归并排序(C语言)

- JAVA计算排列数