基于FPGA的数字电路(PWM脉宽调制)

发布时间:2023年12月31日

一.PWM的制作原理

????????假如我们有一个锯齿波,然后在锯齿波上设置一个阈值(黑色水平虚线),凡是大于该阈值时输出均为高电平,反之则为低电平,这样我们是不是就得到一个PWM信号呢?如果我们想调整它的占空比,那么调节阈值的高低就可以了。

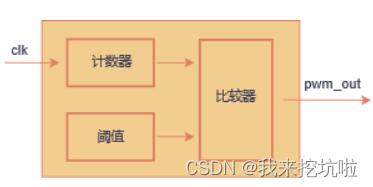

二. FPGA设计框图

????????把上面的描述再抽象化一下,就可以画出的模块框图。锯齿波实际上就可以用计数器生成,阈值就是一个数值而已,比较器是用来生成最后输出高低电平用的。

三.代码实现

????????设置的计数器位宽是8位,也就是每128次后自动重新计数。所以,该计数器的最大频率也就是12MHz/128=93.75KHz。上图可以看出,PWM信号的频率和计数器的频率相同,因此也是93.78KHz。

module pwm (PWM_out, clk, reset);

input clk, reset;

output reg PWM_out;

wire [7:0] counter_out; //计数器的8位宽储存,可以最多数128次时钟的嘀嗒

parameter PWM_ontime = 32; //阈值设在32,对应25%的占空比

always @ (posedge clk) begin //比较器

if (PWM_ontime > counter_out)

PWM_out <= 0;

else

PWM_out <= 1;

end

counter counter_inst( //调用计数器

.clk (clk),

.counter_out (counter_out),

.reset(reset)

);

endmodule

module counter(counter_out,clk,reset); //计数器模块代码

output [7:0] counter_out;

input clk, reset;

reg [7:0] counter_out;

always @(posedge clk)

if (reset) //如果没有按reset,则计数器清零

counter_out <= 8'b0;

else //如果按下reset,则计数器开始计数

counter_out <= counter_out + 1;

endmodule

文章来源:https://blog.csdn.net/weixin_66634995/article/details/135310954

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Python线程池multiprocessing.Pool

- 一文读懂算法中的时间复杂度和空间复杂度,O(1)、O(logn)、O(n)、O(n^2)、O(2^n) 附举例说明,常见的时间复杂度,空间复杂度

- [贪心算法] 国王游戏

- Gartner发布数据安全治理指南:采取四个关键步骤,加快数据安全治理的采用

- 【Linux】Java文件IO之普通IO与Buffer IO

- 加速你的数据库:公司中SQL优化的八大绝招

- TPAMI: 基于强化学习的灵巧双手操作技能学习

- C++初阶——类和对象

- 【Proteus仿真】【Arduino单片机】数控稳压可调电源设计

- 混淆技术概论