STM32系统架构

发布时间:2024年01月17日

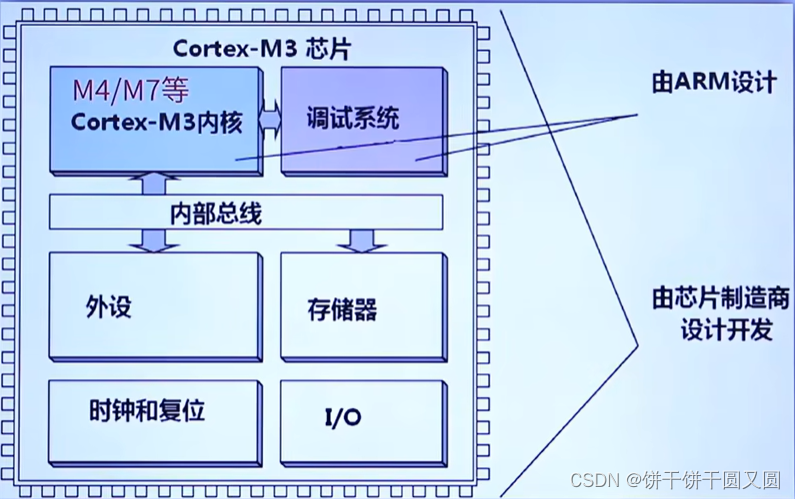

Cortex-M内核&芯片

Cortex-M内核以及调试系统由ARM公司设计,并授权给芯片制造厂商。

由芯片制造商设计开发芯片。

MCU厂商,经ARM公司授权,添加不同的外设=各种xx32芯片

F1系统架构

4个主动单元+4个被动单元

- Cortex-M3内核 DCode总线(D-Bus)

- Cortex-M3内核 系统总线(S-Bus)

- 通用DMA1

- 通用DMA2

- 内部FLASH

- 内部SRAM

- FSMC

- AHB到APB的桥,它连接的所有APB外设

主动单元可以主动发起通信或指令,但被动单元不能。

AHB:高级高性能总线,APB:高级外围总线

F1系统架构图

ICode总线直接连接Flash接口,不需要经过总线矩阵。

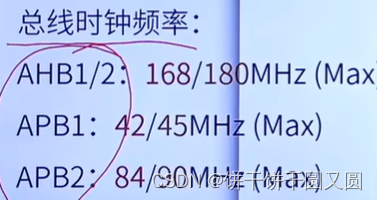

总线时钟频率:

- AHB:72MHz

- APB1:36MHz

- APB2:72MHz

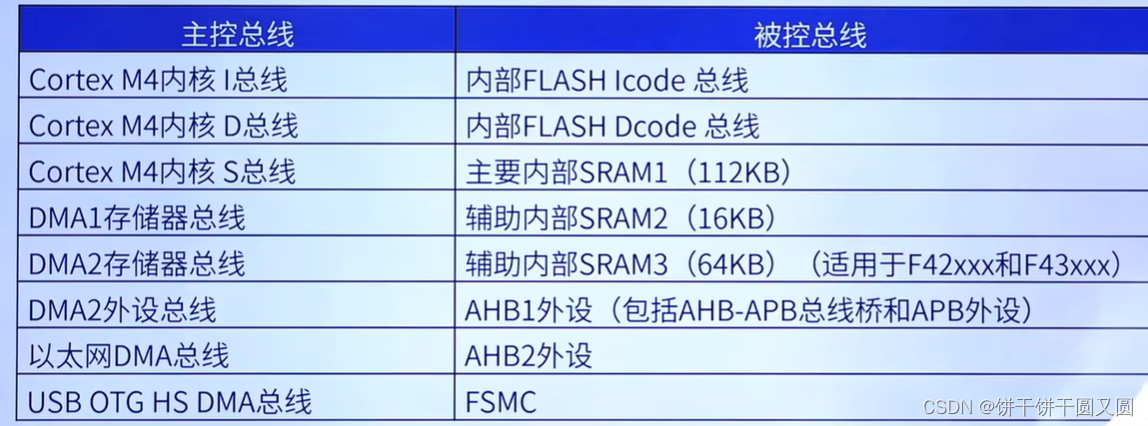

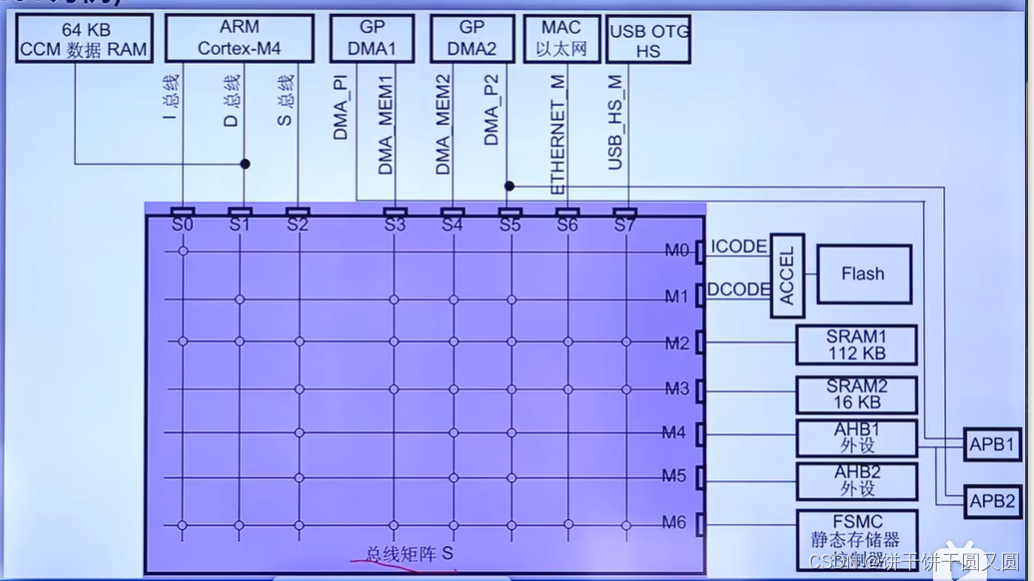

F4系统架构

8个主控总线+7个被控总线

CCM RAM:只能访问数据,优点访问速度快,缺点不支持DMA。

文章来源:https://blog.csdn.net/Caramel_biscuit/article/details/135641456

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 水印遮挡该如何去除呢

- 叫板GPT-4的Gemini,我做了一个聊天网页,可图片输入,附教程

- SpringCloud使用篇

- 抖音旋转验证码角度识别代码分享

- 1434. 数池塘(四方向)-深度优先搜索-DFS

- python3:爬虫代理IP的使用+建立代理IP池

- 【无标题】

- 2024黑龙江省职业院校技能大赛暨国赛选拔赛信息安全管理与评估赛项(高职组)赛题第2套

- 大创项目推荐 图像识别-人脸识别与疲劳检测 - python opencv

- 【正点原子STM32连载】第十九章 通用定时器输入捕获实验 摘自【正点原子】APM32E103最小系统板使用指南