计算机组成原理-CPU数据通路(单总线结构和专用通路结构)

发布时间:2023年12月18日

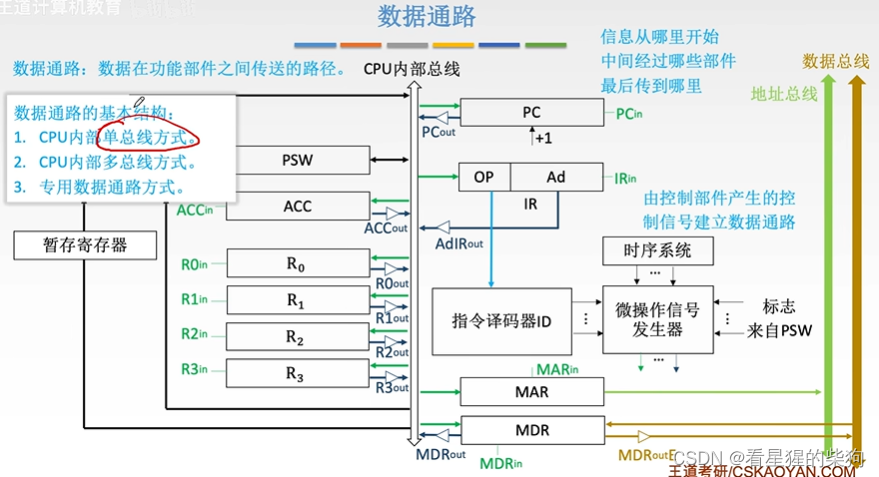

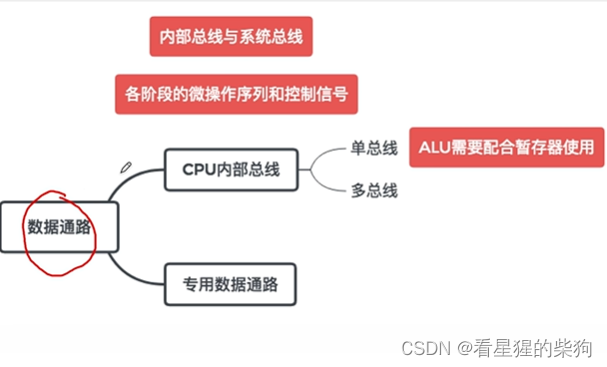

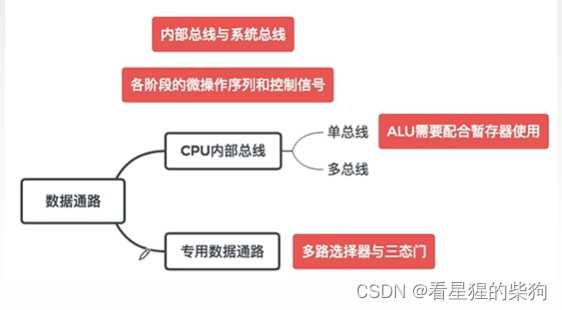

数据通路

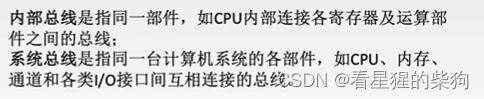

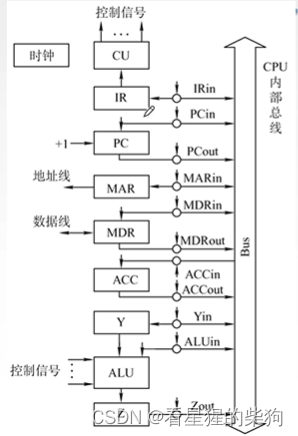

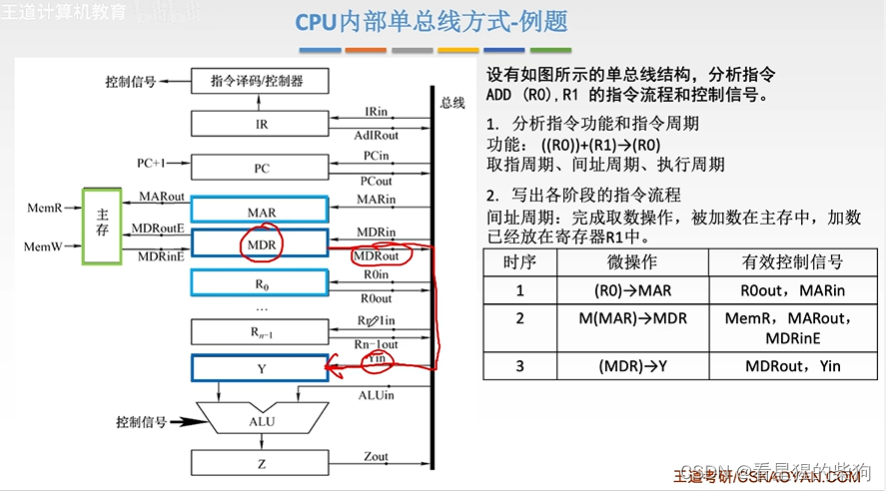

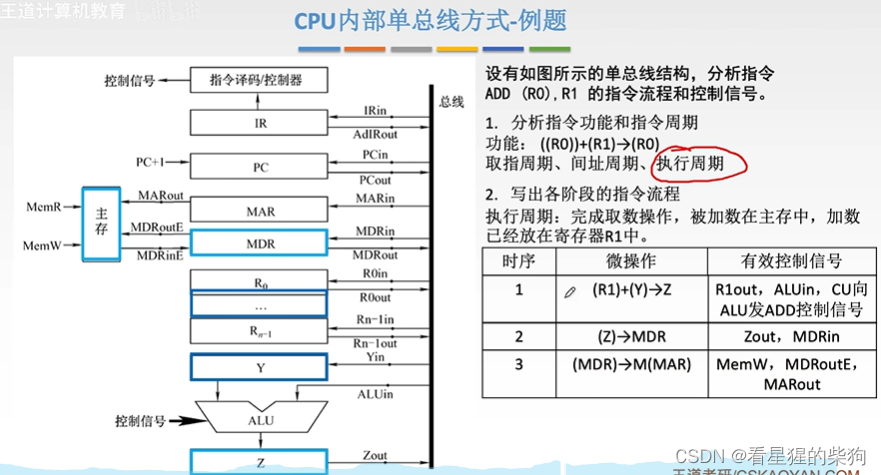

CPU内部单总线方式

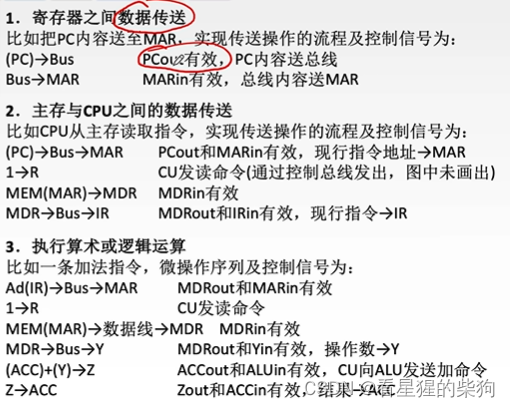

同一时刻内一个总线只可以支持一组部件的数据交互

CPU与各个寄存器的in out线接通可以控制其输入还是输出

Y和ALU有专用数据通路

每个时钟周期CU都会发出一组控制信号去实现微操作

例题

()把括号内的东西取出其储存的内容

指令译码可以认为是把IR内容传入CU

也可以把(PC)+1—>PC补到(MDR)—IR后面

此时MAR依然是(R0)

小结

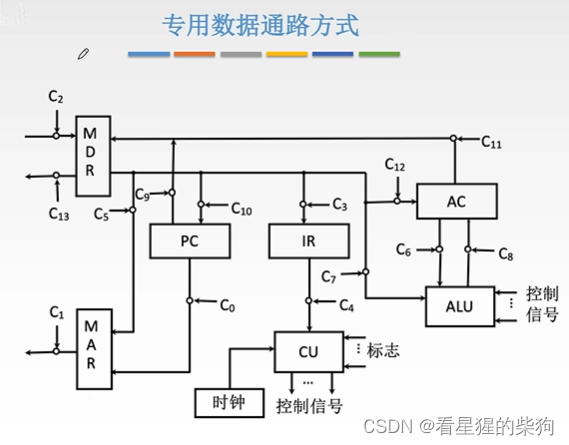

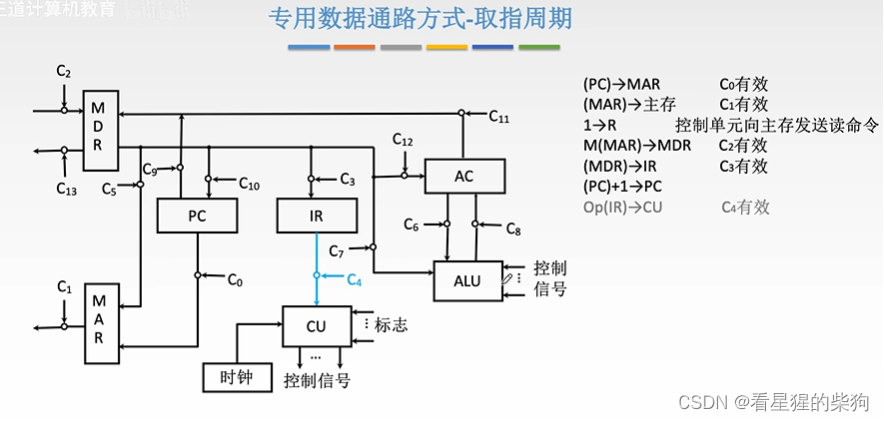

专用数据通路方式

C1等这些接口与CU连接,通过CU发出控制信号来使得有效还是无效(能否通过)

专用数据通路方式-取指周期

Op取指令的操作码部分

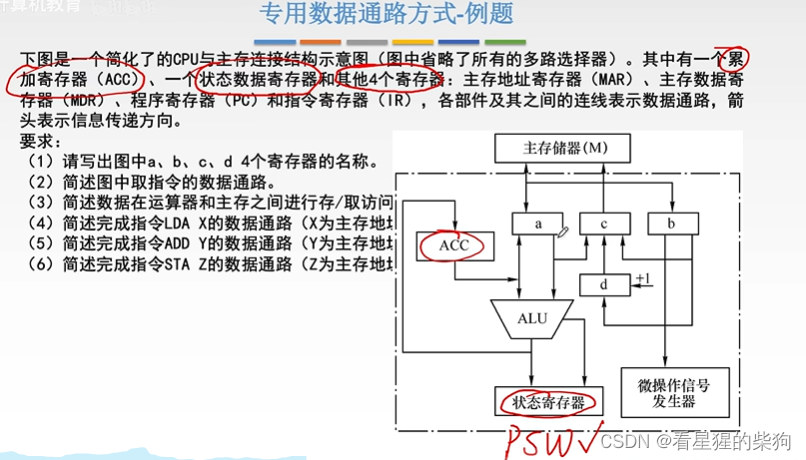

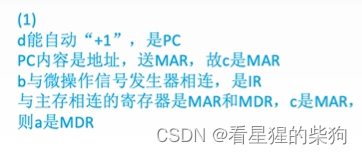

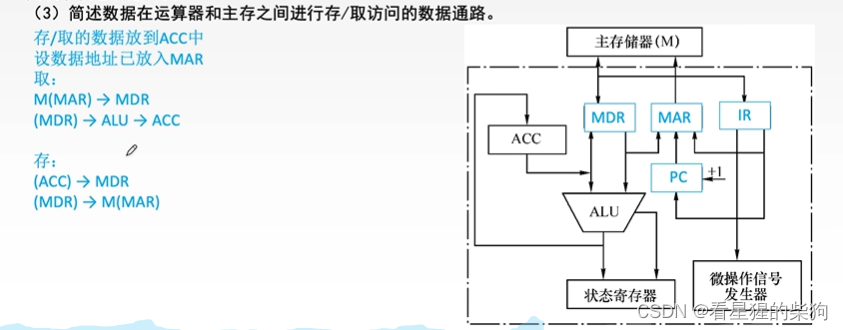

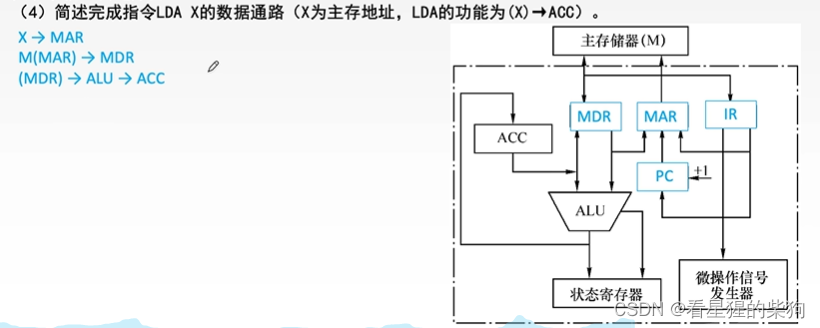

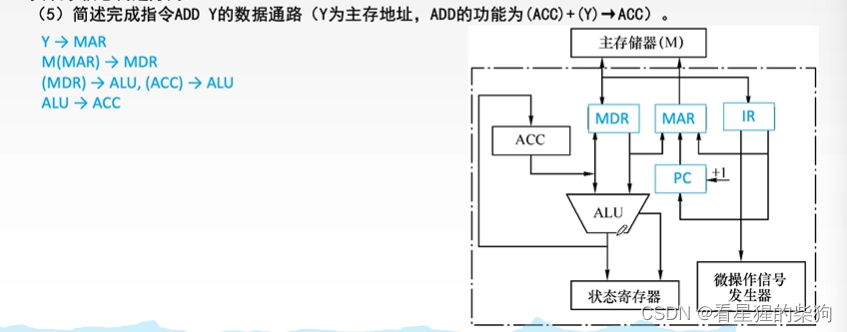

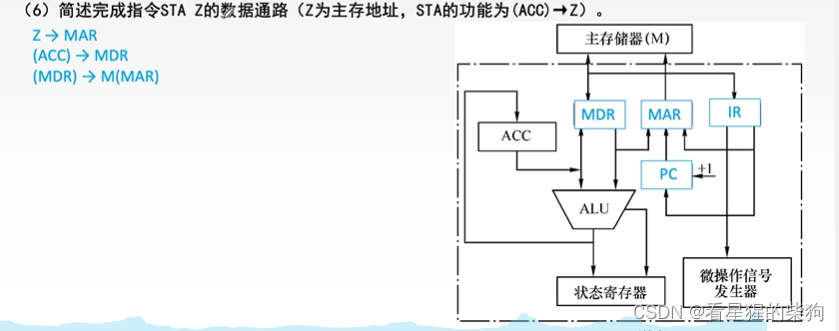

专用数据通路方式-例题

MDR与主存是双向(要读要写)

MAR与主存是单向(只有传输到主存)

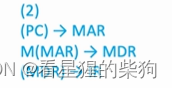

第二问可以补上(PC)+1—>PC,然后是Op(IR)—>微操作信号发生器

ALU可以支持啥都不做然后让信号没有变化的流出来(可以理解为将该数与零相加结果没变)

默认要主存地址已经在MAR中

默认指令已经在IR中

将IR中的形式地址传到MAR

默认指令已经在IR中

将IR中的形式地址传到MAR

默认指令已经在IR中

将IR中的形式地址传到MAR

小结

采用专用数据通路会有多个输入,要哪个输入信号有效可以通过多路选择器或者给每个输入都连一个三态门

文章来源:https://blog.csdn.net/llovewuzhengzi/article/details/135069833

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- yolov5的完整部署(适合新人和懒人,一键安装)

- 如何使用 Ray 开发万能面板(万字 全流程 手把手教学)

- 一些数字设计及验证的笔试题(6)

- B2091 向量点积计算 题解

- vue day5

- 蓝桥杯官网填空题(一步之遥)

- 【云原生之Docker实战】使用Docker部署WBO在线协作白板

- Python采集猎聘网站招聘数据内容,看看现在职位风向

- Plant Physiology:转录因子PpNAC1和DNA去甲基酶PpDML1协同调控桃果实成熟

- 在Linux上安装CLion