计算机系统(软考版)----计算机系统基础知识、基本单位与进制(1)

文章目录

- 计算机系统基础知识

- 一 硬件组成

- 二 CPU功能

- 三 CPU组成

- 运算器

- 控制器

- 寄存器组

- 练习题(答案为加粗部分)

- 计算机基本单位与进制

- 一 计算机基本单位

- 二 进制

- 1 概述

- 2 进制转换

- 3 进制加减

- 练习题(答案为加粗部分)

计算机系统基础知识

一 硬件组成

计算机系统是由硬件和软件组成的,它们协同工作来运行程序。计算机的基本硬件系统由运算器、控制器、存储器、输入设备和输出设备5大部件组成。运算器、控制器等部件被集成在一起统称为中央处理单元(Central Processing Unit,CPU)。(标黄这个需要记忆)CPU是硬件系统的核心,用于数据的加工处理,能完成各种算术、逻辑运算及控制功能。存储器是计算机系统中的记忆设备,分为内部存储器和外部存储器。前者速度高、容量小,一般用于临时存放程序、数据及中间结果。而后者容量大、速度慢,可以长期保存程序和数据。输入设备和输出设备合称为外部设备(简称外设),输入设备用于输入原始数据及各种命令,而输出设备则用于输出计算机运行的结果。

二 CPU功能

中央处理单元(CPU)是计算机系统的核心部件,它负责获取程序指令、对指令进行译码并加以执行。

三 CPU组成

CPU主要由运算器、控制器、寄存器组和内部总线等部件组成

运算器

运算器由算术逻辑单元(Arithmetic and Logic Unit,ALU)、累加寄存器、数据缓冲寄存器和状态条件寄存器等组成。它是数据加工处理部件,用于完成计算机的各种算术和逻辑运算。相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。

运算器有如下两个主要功能。

执行所有的算术运算,例如加、减、乘、除等基本运算及附加运算。

执行所有的逻辑运算并进行逻辑测试,例如与、或、非、零值测试或两个值的比较等。

运算器中各组成部件的功能

- 算术逻辑单元(ALU)。ALU是运算器的重要组成部件,负责处理数据,实现对数据的算术运算和逻辑运算。

- 累加寄存器(AC)。AC通常简称为累加器,它是一个通用寄存器,其功能是当运算器的算术逻辑单元执行算术或逻辑运算时,为ALU提供一个工作区。例如,在执行一个减法运算前,先将被减数取出暂存在AC 中,再从内存储器中取出减数,然后同AC的内容相减,将所得的结果送回AC中。运算的结果是放在累加器中的,运算器中至少要有一个累加寄存器。为ALU提供数据并暂存运算结果

- 数据缓冲寄存器(DR)。在对内存储器进行读/写操作时,用DR暂时存放由内存储器读/写的一条指令或一个数据字,将不同时间段内读/写的数据隔离开来。DR的主要作用为:作为CPU和内存、外部设备之间数据传送的中转站;作为CPU和内存、外围设备之间在操作速度上的缓冲;在单累加器结构的运算器中,数据缓冲寄存器还可兼作为操作数寄存器。

- 状态条件寄存器(PSW)。PSW保存由算术指令和逻辑指令运行或测试的结果建立的各种条件码内容,主要分为状态标志和控制标志,例如运算结果进位标志(C)、运算结果溢出标志(V)、运算结果为0标志(Z)、运算结果为负标志(N)、中断标志(I)、方向标志(D)和单步标志等。这些标志通常分别由 1 位触发器保存,保存了当前指令执行完成之后的状态。通常,一个算术操作产生一个运算结果,而一个逻辑操作产生一个判决。 保存由算数指令和逻辑指令运行或测试的结果建立的各种条件码内容。

控制器

指令 = 操作码 + 地址码

例如:1 + 2 中 1 和 2 为地址码; + 为操作码。

运算器只能完成运算,而控制器==用于控制整个CPU 的工作,它决定了计算机运行过程的自动化。它不仅要保证程序的正确执行,而且要能够处理异常事件。==控制器一般包括指令控制逻辑、时序控制逻辑、总线控制逻辑和中断控制逻辑等几个部分。

指令控制逻辑要完成取指令、分析指令和执行指令的操作,其过程分为取指令、指令译码、按指令操作码执行、形成下一条指令地址等步骤。

- 指令寄存器(IR)。当CPU执行一条指令时,先把它从内存储器取到缓冲寄存器中,再送入IR暂存,指令译码器根据 IR 的内容产生各种微操作指令,控制其他的组成部件工作,完成所需的功能。保存当前CPU执行的指令(指令 = 操作码 + 地址码)

- 程序计数器(PC)PC具有寄存信息和计数两种功能,又称为指令计数器。程序的执行分两种情况,一是顺序执行,二是转移执行。在程序开始执行前,将程序的起始地址送入PC,该地址在程序加载到内存时确定,因此PC的内容即是程序第一条指令的地址。执行指令时,CPU自动修改PC的内容,以便使其保持的总是将要执行的下一条指令的地址。由于大多数指令都是按顺序来执行的,所以修改的过程通常只是简单地对PC加1。当遇到转移指令时,后继指令的地址根据当前指令的地址加上一个向前或向后转移的位移量得到,或者根据转移指令给出的直接转移的地址得到。

- 地址寄存器(AR)。AR保存当前CPU所访问的内存单元的地址。由于内存和CPU存在着操作速度上的差异,所以需要使用AR保持地址信息,直到内存的读/写操作完成为止。

- 指令译码器(ID)。指令包含操作码和地址码两部分,为了能执行任何给定的指令,必须对操作码进行分析,以便识别所完成的操作。指令译码器就是对指令中的操作码字段进行分析解释,识别该指令规定的操作,向操作控制器发出具体的控制信号,控制各部件工作,完成所需的功能。对指令中的操作码字段进行分析解释

时序控制逻辑要为每条指令按时间顺序提供应有的控制信号。总线逻辑是为多个功能部件服务的信息通路的控制电路。中断控制逻辑用于控制各种中断请求,并根据优先级的高低对中断请求进行排队,逐个交给CPU 处理。

指令寄存器(IR)存放的是从内存中取得指令,就像个中间站一样,不过是存放指令的中间站

程序计数器(PC)存放的是指令的地址,还有计数的功能

地址寄存器(AR)存放的是cpu访问内存单元的地址

指令译码器(ID)是把操作码解析成对应的指令操作

PC:程序计数器(PC)保存下一条要执行或解码的指令的地址。

IR:指令寄存器(IR)保存当前正在执行或解码的指令。

寄存器组

寄存器组可分为专用寄存器和通用寄存器。运算器和控制器中的寄存器是专用寄存器,其作用是固定的。通用寄存器用途广泛并可由程序员规定其用途,其数目因处理器不同有所差异。

用户可见:通用寄存器组、程序状态字寄存器(PSWR)、程序计数器(PC)、累加寄存器(ACC)

用户不可见:指令寄存器(IR)、暂存寄存器(DR)、存储器地址寄存器(MAR)、存储器数据寄存器(MDR)

练习题(答案为加粗部分)

-

在CPU中,常用来为ALU执行算术逻辑运算提供数据并暂存运算结果的寄存器是 (1) 。(2014年上半年)

(1) A. 程序计数器 B. 状态寄存器

C. 通用寄存器 D. 累加寄存器 -

属于CPU中算术逻辑单元的部件是 (3) 。(2014年下半年)

(3) A. 程序计数器 B. 加法器 C. 指令寄存器 D. 指令译码器 -

CPU执行算术运算或者逻辑运算时,常将源操作数和结果暂存在 (1) 中。(2017年上半年)

(1) A. 程序计数器(PC) B. 累加器(AC)

C. 指令寄存器(IR) D. 地址寄存器(AR) -

以下关于CPU的叙述中,错误的是 (1) 。(2009年下半年)

(1) A. CPU产生每条指令的操作信号并将操作信号送往相应的部件进行控制

B. 程序计数器PC除了存放指令地址,也可以临时存储算术/逻辑运算结果

C. CPU中的控制器决定计算机运行过程的自动化

D. 指令译码器是CPU控制器中的部件 -

计算机指令一般包括操作码和地址码两部分,为分析执行一条指令,其 (5) 。(2010年上半年)

(5) A. 操作码应存入指令寄存器(IR),地址码应存入程序计数器(PC)

B. 操作码应存入程序计数器(PC),地址码应存入指令寄存器(IR)

C. 操作码和地址码都应存入指令寄存器(IR)

D. 操作码和地址码都应存入程序计数器(PC) -

在CPU的寄存器中, (5) 对用户是完全透明的。(2011年下半年)

(5) A. 程序计数器 B. 指令寄存器

C. 状态寄存器 D. 通用寄存器(书上没提,这里单独记忆一下。) -

CPU中译码器的主要作用是进行 (6) 。(2011年下半年)

(6) A. 地址译码 B. 指令译码

C. 数据译码 D. 选择多路数据至ALU -

在CPU中, (1) 不仅要保证指令的正确执行,还要能够处理异常事件。(2012年下半年)

(1) A. 运算器 B. 控制器

C. 寄存器组 D. 内部总线 -

计算机执行指令的过程中,需要由 (1) 产生每条指令的操作信号并将信号送往相应的部件进行处理,以完成指定的操作。(2019年上半年)

(1) A. CPU的控制器 B. CPU的运算器

C. DMA控制器 D. Cache控制器 -

为实现程序指令的顺序执行,CPU (1) 中的值将自动加1。(2010年上半年)

(1) A. 指令寄存器(IR) B. 程序计数器(PC)

C. 地址寄存器(AR) D. 指令译码器(ID) -

在CPU中用于跟踪指令地址的寄存器是 (1) 。(2011年上半年)

(1) A. 地址寄存器(MAR) B. 数据寄存器(MDR)

C. 程序计数器(PC) D. 指令寄存器(IR) -

计算机在一个指令周期的过程中,为从内存读取指令操作码,首先要将 (2) 的内容送到地址总线上。(2016年下半年)

(2) A. 指令寄存器(IR) B. 通用寄存器(GR)

C. 程序计数器(PC) D. 状态寄存器(PSW) -

CPU在执行指令的过程中,会自动修改 (1) 的内容,以便使其保持的总是将要执行的下一条指令的地址。(2018年下半年)

(1) A. 指令寄存器 B. 程序计数器

C. 地址寄存器 D. 指令译码器 -

计算机中提供指令地址的程序计数器PC在 (2) 中。(2020年下半年)

(2) A. 控制器 B. 运算器

C. 存储器 D. I/O设备 -

在CPU中,用 (1) 给出将要执行的下一条指令在内存中的地址。(2021年上半年)

(1) A. 程序计数器 B. 指令寄存器

C. 主存地址寄存器 D. 状态条件寄存器

计算机基本单位与进制

一 计算机基本单位

| 中文名称 | 英文名称 | 英文缩写 | 转换关系 |

|---|---|---|---|

| 位(比特) | bit | b | |

| 字节 | byte | B | 1 B = 8b |

| 千字节 | KB | K | 1KB = 1024B |

| 兆字节 | MB | 1MB = 1024KB | |

| 吉字节 | GB | 1GB = 1024MB | |

| 太字节 | TB | 1TB = 1024GB了解: |

了解: 计算机中最小的数据单位: b

最小的操作单位: byte

二 进制

1 概述

| 进制 | 后缀表示 | 基数 |

|---|---|---|

| 二进制 | B | 0和1 |

| 八进制 | O | 0-7 |

| 十进制 | D | 0-9 |

| 十六进制 | H | 0-9,A-F (0-15) |

基数是指一种进制中组成的基本数字,也就是不能再进行拆分的数字

2 进制转换

(1) 十进制

n 进制转 十进制

十进制转n进制(除 n 取余法)

(2)二进制

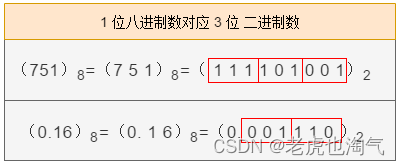

转八进制

转十六进制

转十进制,参考 (1)十进制

(3)八进制

转二进制

转十六进制

转十进制,参考 (1)十进制

(4)十六进制

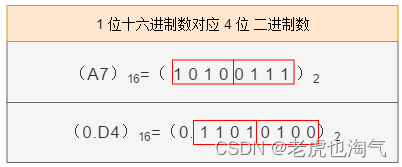

转二进制

转八进制

转十进制,参考 (1)十进制

3 进制加减

(1)相加

规则: 逢 n 进 1

(2)相减

规则: 借 1 转 n

练习题(答案为加粗部分)

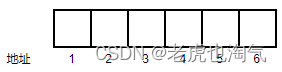

类型1: 给你一个地址的范围,问你有几个存储单元

假设地址范围为[1,6]

存储单元个数 : (6 - 1) + 1 = 6

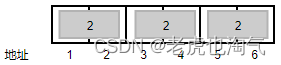

类型2:给你一个地址范围,再给你一个芯片的大小,问你需要几片芯片

假设芯片大小为 2,地址范围为[1,6]

先计算存储单元个数: (6 - 1) + 1 = 6

再计算需要多少片芯片: 6/2 = 3

1 示例1

内存单元按字节编址,地址0000A000H?0000BFFFH共有 (2) 个存储单元。(2012年上半年)

(2) A. 8192K B. 1024K C. 13K D. 8K

分析:

答案: D

2 示例2

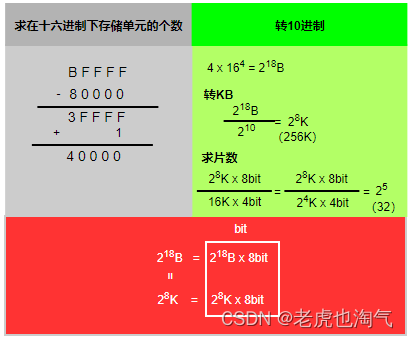

地址编号从80000H到BFFFFH且按字节编址的内存容量为 (5) KB,若用 16K x 4bit 的存储器芯片构成该内存,共需 (6) 片。(2013年上半年)

(5) A. 128 B. 256 C. 512 D. 1024

(6) A. 8 B. 16 C. 32 D. 64

分析:

答案: 256 32

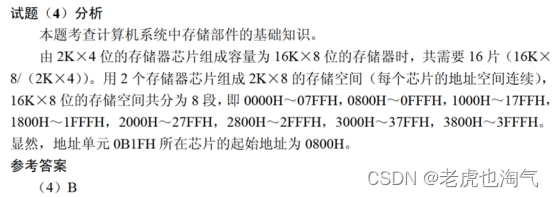

3 示例3(%)

设用 2K x 4 位的存储器芯片组成 16K x 8 位的存储器(地址单元为0000H?3FFFH,每个芯片的地址空间连续),则地址单元0B1FH所在芯片的最小地址编号为 (4) 。(2010年下半年)

(4) A. 0000H B. 0800H C. 2000H D. 2800H

存储器是8bit的,而芯片是4bit的。因此需要用两片芯片构成一个8bit的

地址单位 0B1FH 位于 0800H~0FFFH之间, 因此最小地址编号为 0800H

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 用pandas实现用前一行的excel的值填充后一行

- android解压zip

- 武侠小说中的AI思想探析与未来启示

- Python-高阶函数

- 研发提效必备技能:手把手教你基于Docker搭建Maven私服仓库

- 2024年最新腾讯云服务器优惠活动大全,轻量和CVM租用价格表

- Kubernetes 核心实战之一(精华篇 1/2)

- 前端面试题汇总大全(含答案)-- 持续更新

- 工作流入门这篇就够了!

- 阿赵UE学习笔记——7、导入资源