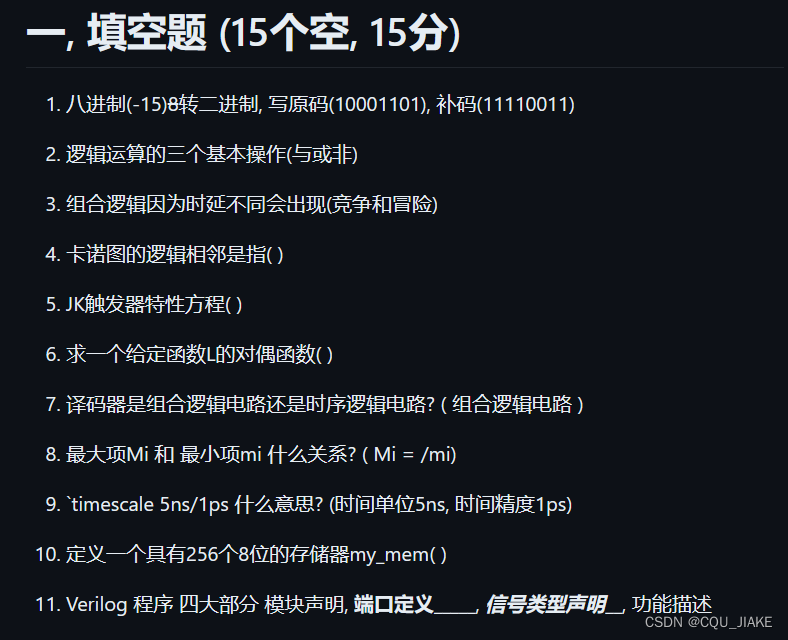

12.19~1.5数字逻辑先兆

WN

补码反码计算,八进制二进制等转换

化简,加两杠进行,与或转换

最小项,定义,m0,m3什么意思

代码说明,第一行的times意义

什么组合逻辑,时序逻辑,区别。输出决定于什么

组合逻辑器件,哪些属于组合逻辑或时序逻辑的器件

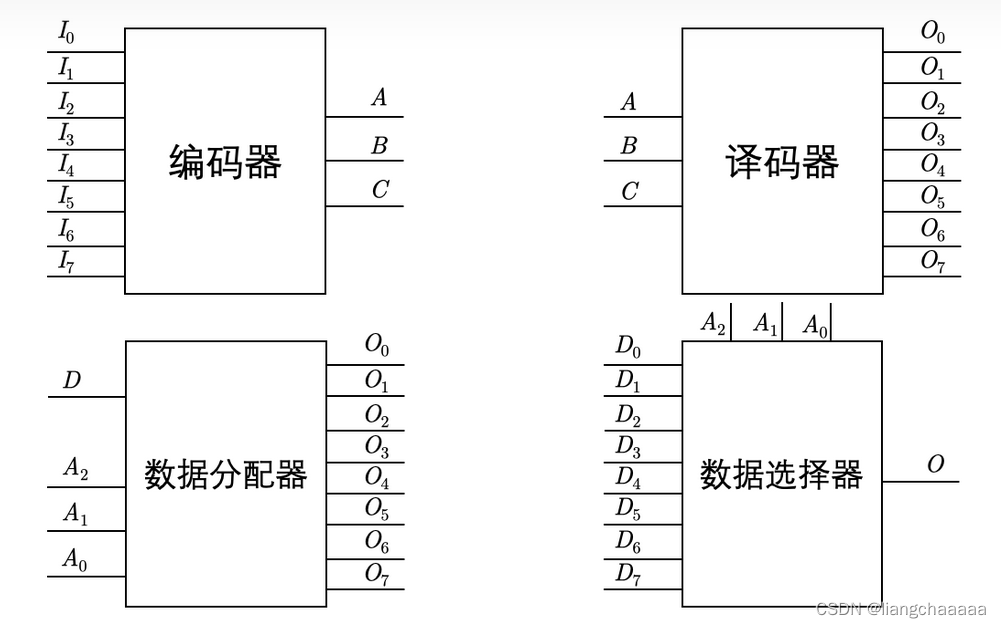

编码器,译码器

电线类型,module,代码翻译,描述几方面信息

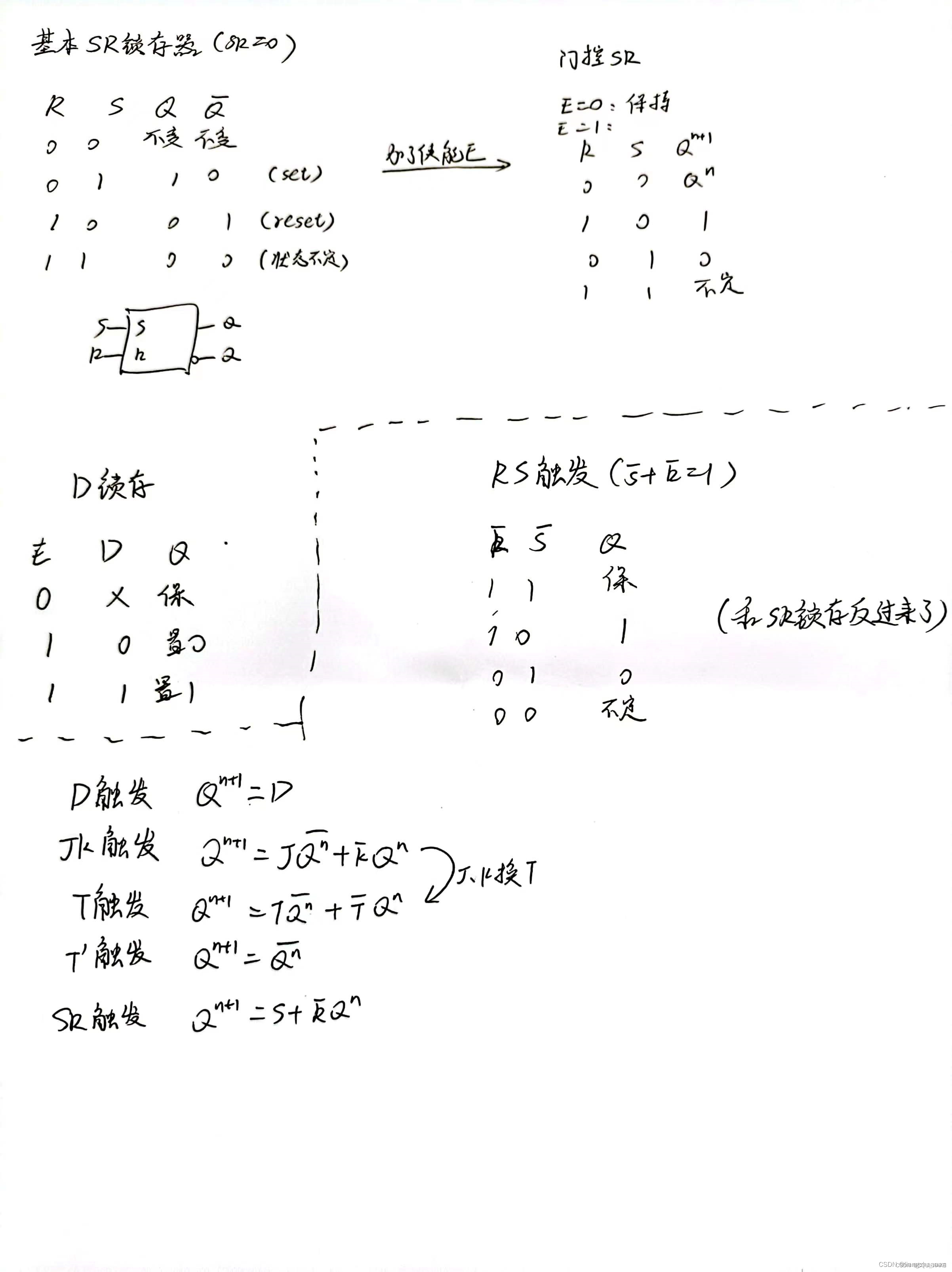

触发器,特征方程的描述

状态机,有限状态机,两类状态机定义于区别

异步,在边沿检测中异步

竞争冒险定义,现象,描述

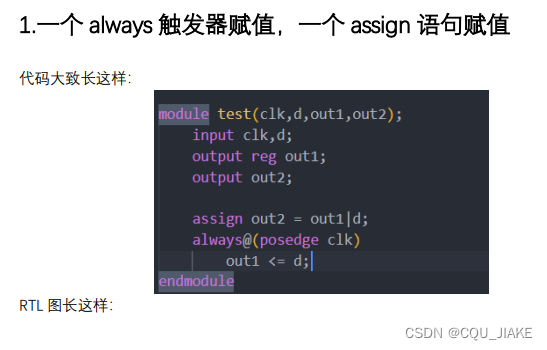

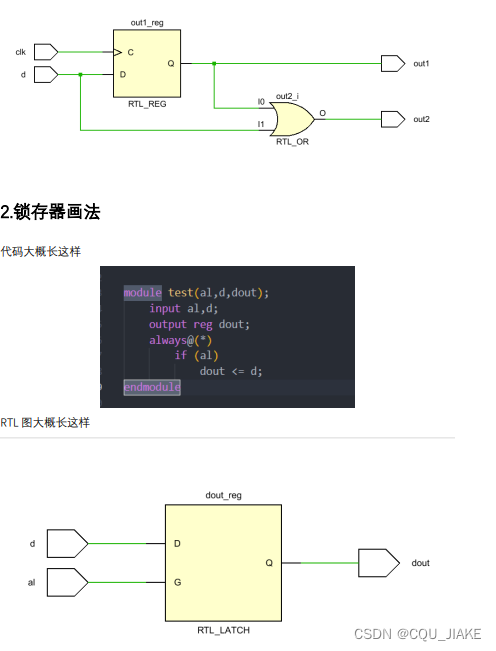

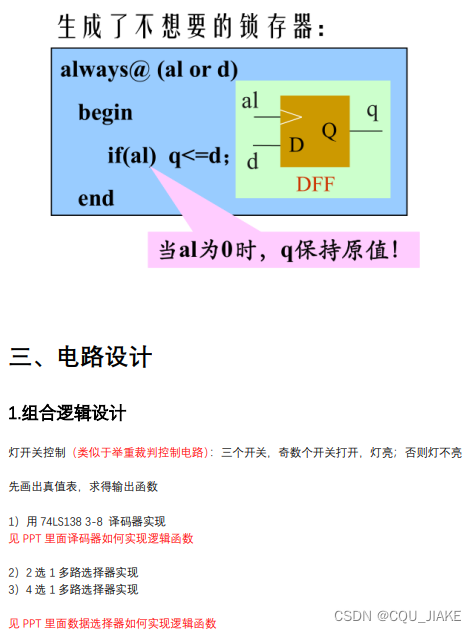

代码,会生成什么电路,赋值方式导致电路不一样

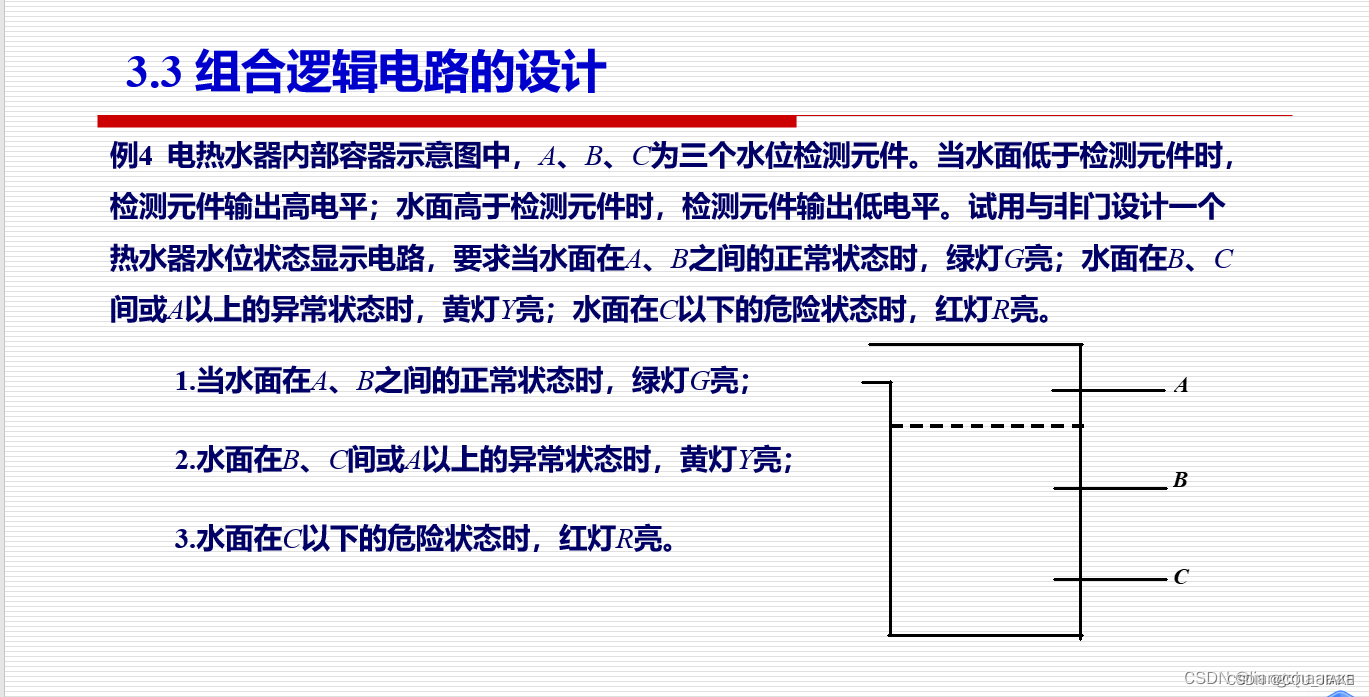

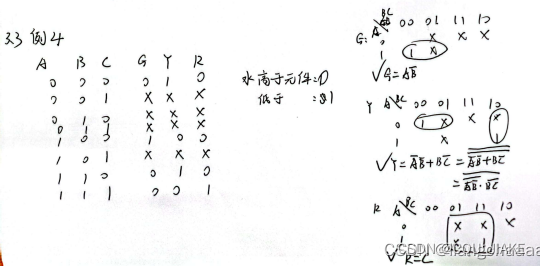

组合电路,时序电路的设计,设计步骤,要画电路也要给出方程(最简与或式给出)

用哪种触发器实现,实现的方式,接线的方式

2道,每道15分

只用写设计的模块

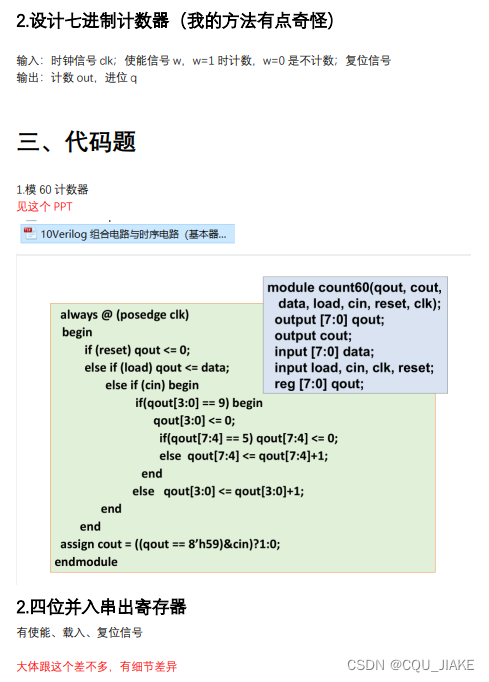

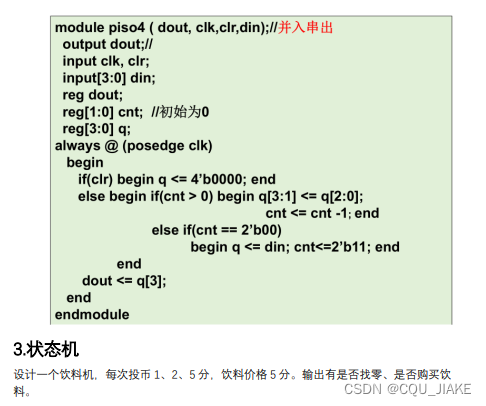

分频,逢几进一,序列检测

?23NQ

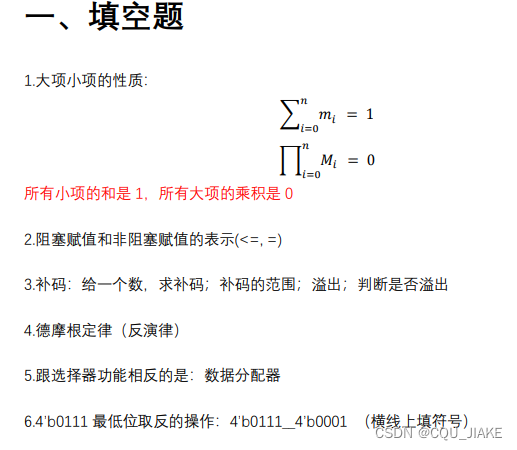

1.8位FE的补码对应的十进制是?

2.把给定逻辑式子转为与非式子

'timescale 5ns/1ps的时间精度

T触发的特征方程

译码器是组合逻辑还是时序?

产生竞争的原因

定义8个1位存储器

verliog程序四大部分

m3对应表达式是?

描述时序逻辑的三大方程?

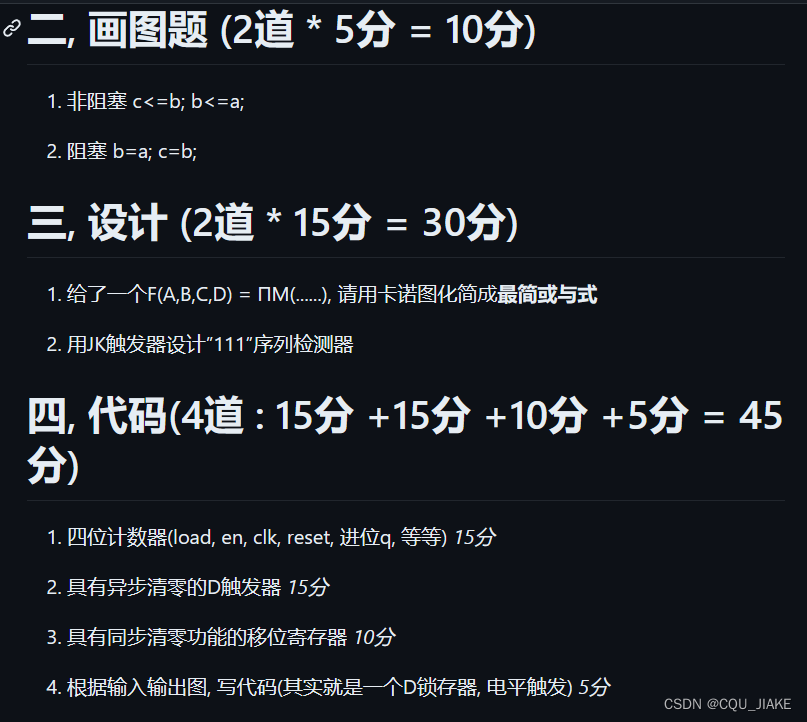

画图题

画两个D触发器

画选择器

设计

用代数方式化简

卡诺图化简

用AB,画化简式子的电路图,用四选一选择器以及逻辑门

用D触发器设计序列检测1010,给出各种方程并画出电路图,

代码

8位全加器

异步D触发器

同步计数器,并给出测试程序

MEALY状态机设计序列检测111

编码器

编码就是将信息装换成独特的代码或信号输出的电路

普通编码器:任何时候只允许输入一个有效编码信号,否则输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信号。当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码。

译码器

译码是将二进制码翻译成代表某一特定含义的信号。(即电路的某种状态)

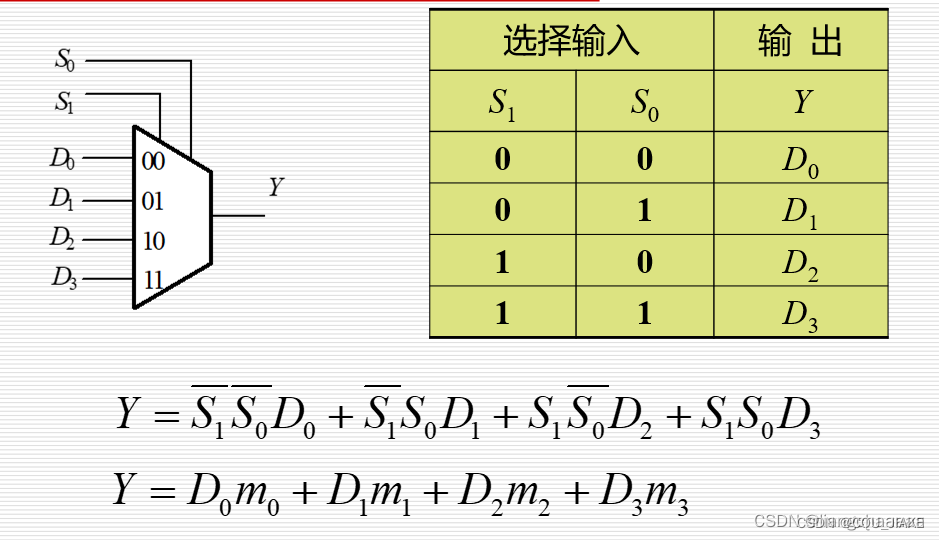

数据选择器

能实现数据选择功能的逻辑电路。它的作用相当于多个输入的单刀多掷开关,又称“多路开关”。

也就是说,它可以从多个输入信号中选择一个并将其输出。

特点:并入串出

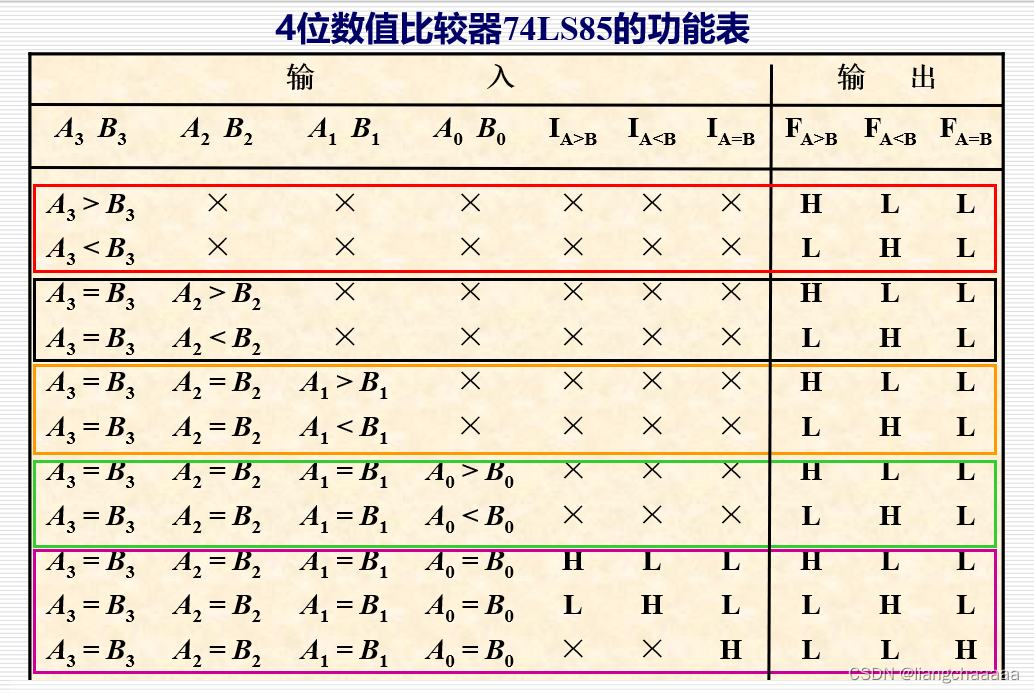

数值比较器?

对两个二进制数字进行比较(A、B),以判断其大小的逻辑电路。

看真值表比较清晰明了

对比图

时序逻辑和组合逻辑区别

组合逻辑电路:它是一种没有存储元件或状态(也就是无记忆)的逻辑电路。它的输出仅由输入决定,不依赖于任何时钟等外部信号。

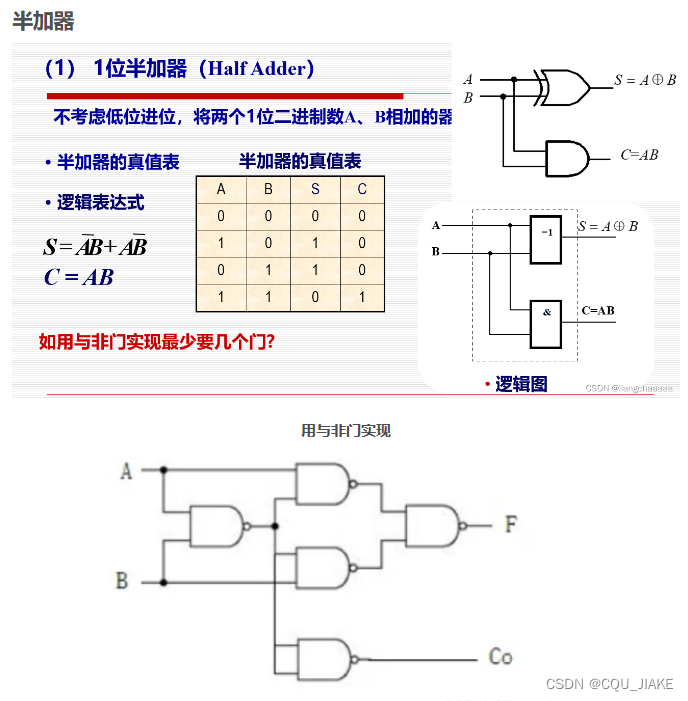

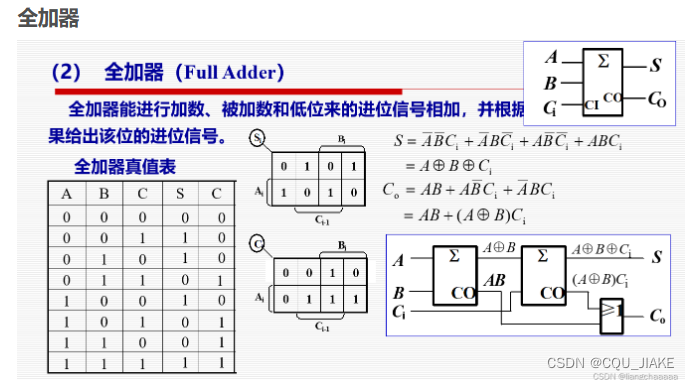

组合逻辑电路的特点是:输出只与当前的输入有关;它可以实现各种基本的逻辑运算,如与、或、非、异或、多路选择器等。典型的应用包括算术逻辑单元、编码器/译码器、加法器、比较器等。

时序逻辑电路:它是一种具有存储元件或状态(也称为有记忆)的逻辑电路。它的输出既依赖于当前的输入,也依赖于前一时刻的状态。时序逻辑电路的动态行为受到时钟信号控制,每当时钟信号发生变化时,它的状态才会更新或者转移。常见的时序逻辑电路包括:触发器、计数器、状态机等。

区别:组合逻辑电路是一种组合多个逻辑门进行的简单逻辑运算的电路,其输出由输入数值决定,并且不受之前任何状态或电路模块的影响。时序逻辑电路则是另一种类型,具有状态和输出两个属性,在每个时钟脉冲到来时,其状态会根据先前状态以及输入信号更新,使得输出与状态相关。在应用方面,时序逻辑电路通常用于实现计数器、定时器、开关模式控制器等需要存储状态或需要特定时序行为时使用;而组合逻辑电路通常用于构建数学操作电路和编码解码电路。

组合电路的输出仅取决于当前的输入,并且没有与时间相关的要求。而时序电路的输出不仅取决于当前的输入,还受到时钟信号和先前输入状态的影响。

锁存器与触发器

锁存器---对脉冲电平敏感的存储电路,在特定输入脉冲电平(高或低电平)作用下改变状态。

触发器---对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

只要涉及到锁存器、触发器,就一定是时序电路

它们都具有存储功能,只是锁存器是要通过特定信号触发,例如使能端,当使能信号为高电平时,锁存器将会接收输入数据并将其存储在内部。即使使能信号变为低电平,锁存器仍然会保持之前存储的数据,直到新的使能信号到来;触发器使用时钟信号,触发器只有在时钟信号的上升沿或下降沿到来时才会接收输入数据并将其存储在内部。触发器的输出也只会在时钟信号的边沿变化时才会改变。

同步清零与异步清零

异步清零是指与时钟不同步,即清零信号有效时,无视触发脉冲,立即清零,不需要时钟配合;

同步清零是时钟触发条件满足时检测清零信号是否有效,有效则在下一个时间周期的触发条件下,执行清零,需要时钟配合。

举个例子:从0000开始计数, 反馈清零的信号是1010,那么异步清零的芯片74X161计算模时1010不算有效状态(时间过短不稳定),M = 10;而在同步清零74X163芯片中,1010算一个有效状态,M = 11,和同步置数计算模过程一样。

进制转换

?

一位16进制,就要对应到4位2进制;一位8进制,就要对应到3位2进制,反之亦然

?

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 如何使用内网穿透搭建公网可访问的Serv-U FTP服务器轻松远程共享文件

- PMP第七版知识点梳理

- 鸿蒙开发之用户隐私权限申请

- Nvidia 推出了一款新型芯片,专为在家中运行人工智能而设计

- 基于JAVA的瑜伽馆管理系统 开源项目

- 【MFC】计算机图形学实验:熟悉开发环境及工具(代码)

- 快递物流怎么寄最便宜?你一定要知道的5个方法 !

- 大路灯护眼灯哪个牌子好?2024年大路灯护眼灯排名

- SpringBoot部署成jar包启动

- YashanDB携手深智城集团联合发布智慧城市解决方案