产品ESD测试

ESD(Electrical?Static?Discharge)产生的原因多种多样,对集成电路放电的方式也有所不同。为了保证集成电路产品的良率,提高可靠性,需要对电路ESD防护能力进行测试。一般测试分为两类:样品研究型测试和产品通过型测试:

(1)样品研究型测试:在芯片的研发阶段,研究器件ESD防护的功能测试。此阶段的测试广泛采用传输线脉冲技术(TLP)。通过TLP测试,可以获得防护器件的关键性能参数,便于在生产制造过程中调整相关的设计,从根本上提高产品的ESD防护能力,保证良率。

(2)在产品通过型测试中,为了更好地量化不同情况下的ESD冲击,分为四种不同的模型:包括工业界作为产品片上ESD等级衡量标准的HBM,CDM模型和针对板级ESD防护的IEC(International?electrotechnical?commission)模型和HMM人体金属模型(Human?metal?model)。

本文仅讨论各种情况下的产品HBM/IEC测试模型。

以下为用于实际测试的静电枪(NSG?437)参数:

一、HBM/IEC模型

(1)HBM模型

人体因摩擦等原因带上一定的静电荷之后,与集成电路的某些引脚接触且集成电路的另一部分引脚恰巧接触到地时,人体上的静电荷就会流经集成电路进入大地。人体能贮存一定的电荷,所以人体明显地存在电容。人体也有电阻,这电阻依赖于人体肌肉的弹性、水份、接触电阻等因素。大部分研究人员认为电容串电阻是较为合理的电气模型。

下图是人体各个位置估算出来的电容图:

Human-Body?Model?and?Electrostatic?Discharge?(ESD)?Tests?-?In?Compliance?Magazine

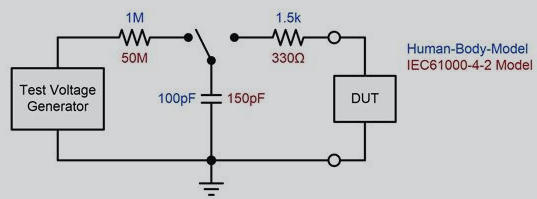

为了求一致,美国海军1980年提出了一个电容为100PF,电阻为1.5kΩ的所谓“标准人体模型”。这一标准得到广泛采用。

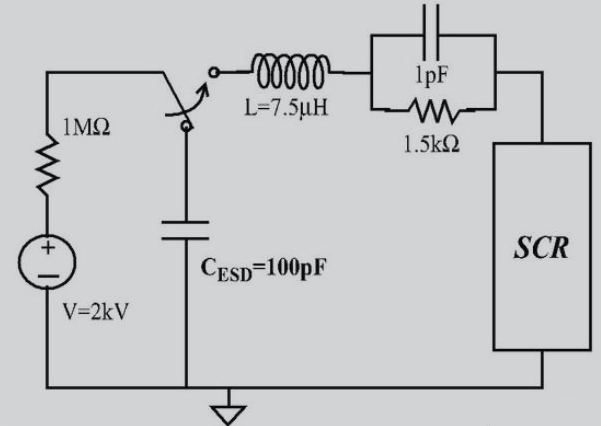

上图用于模拟带电人体的电路元件是一个100pF的电容,放电路径的电阻是1.5kΩ,?7.5μH电感和1pF电容是模拟实际测试仪中放电路径的有效寄生电感和寄生电容。对于不同的人体和测试情况,寄生电容和寄生电感的值有所不同。

(2)IEC模型

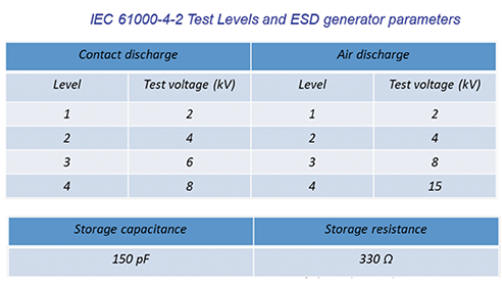

目前,人体最常见的IEC电路模型由150pF和330Ω组成(标准IEC/EN?61000-4-2)。

典型的RC组合有:

(3)NSG?437静电枪可选配置

?①IEC/EN?61000-4-2:2008标准(整机ESD标准):150pF+330Ω

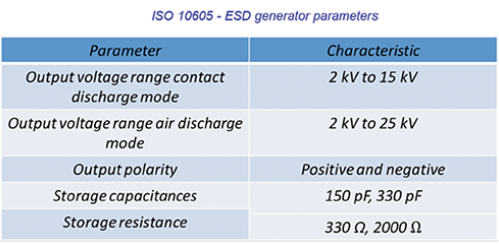

②ISO?10605:2008标准(车规ESD标准):150pF/330pF+330Ω/2000Ω

【注】:

IEC/EN?61000-4-2:2008标准,ESD测试要求为:

ISO?10605:2008标准,ESD测试要求为:

(4)电流上升时间

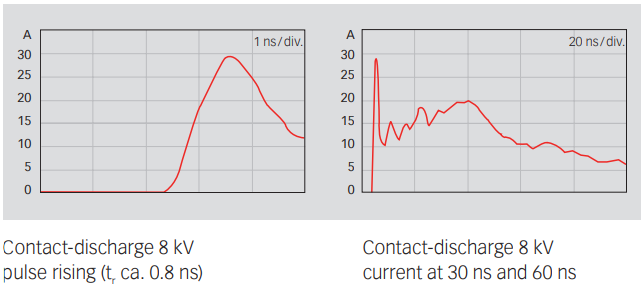

典型HBM波形是2~10ns的上升时间、0.67A/kv的电流,200ns脉冲宽度的双重指数信号衰减波形。

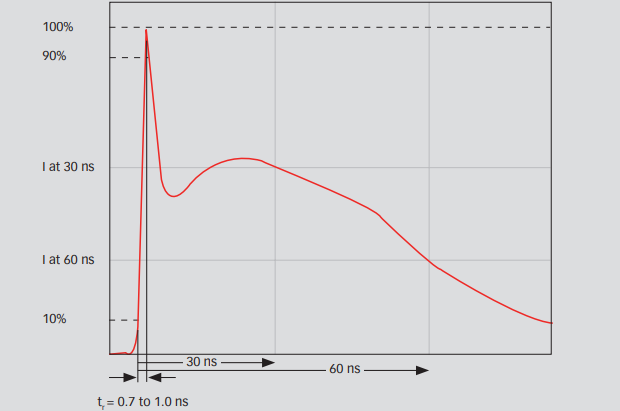

静电枪NSG?437默认上升时间0.8ns和脉冲宽度60ns:

静电枪符合IEC/EN?61000-4-2?(2001)标准,0.7~1.0ns的上升电流,3.75A/kv 的电流,60ns脉冲宽度,如下:

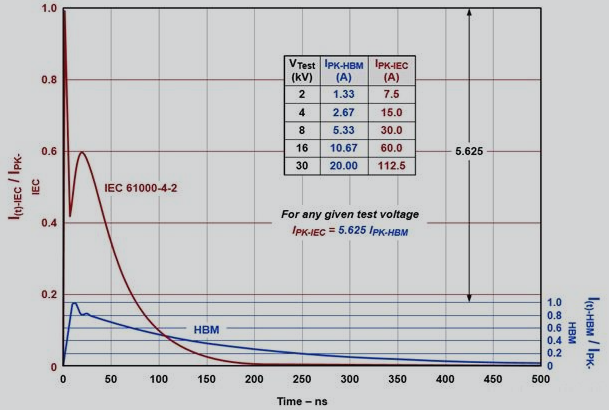

由于IEC?61000-4-2雷击电流的上升时间小于1ns,当暴露于?IEC-ESD冲??击时,设计用于处理HBM冲击(2~10ns)的ESD结构可能无法足够快地运行。因此,保护??电路不能充分发挥保护器件的作用,结果器件被损坏。峰值电流的大小对于组件能否经受?ESD冲??击至关重要。?IC有可能在8kV?HBM冲击下幸存下来,但在低得多的?2kV?IEC-ESD?冲??击下失效(电流更大,IEC电流约为HBM的5.625倍)。HBM规范中的ESD冲??击次数仅限于单次正极冲击和单次负极冲击,而IEC61000-4-2要求至少10次正极冲击和10次负极冲击。

即推荐使用NSG?437静电枪IEC模式分开进行10次正极冲击和10次负极冲击(不是正反极冲击连续交替),操作方式详见第二章第(3)节。

(5)引脚应力测试模式

对于HBM,根据芯片引脚的分类,主要是:

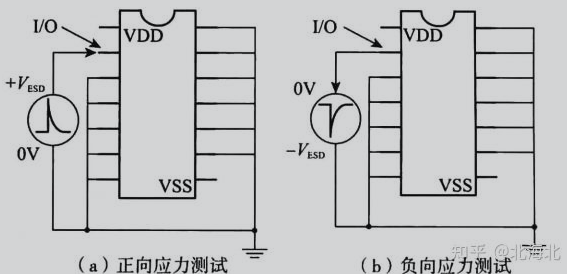

(1)I/O引脚对电源和地引脚的应力测试:对于每一个I/O引脚而言,其相对于正电源或者负电源都可能存在正向静电应力和负向静电应力,因此I/O引脚有四种测试模式,PS模式(positive?to?VSS),NS模式(negative?to?VSS),PD模式(Positive?to?VDD),ND模式(negative?to?VDD)。当某一引脚对电源进行应力测试时,其他引脚需处于悬浮状态

(2)I/O引脚到I/O引脚应力测试:不同I/O引脚之间也存在正、负两种应力情况,在实际静电放电过程中,通常是其中某一个I/O引脚遭受ESD应力而另一个或多个I/O引脚接地形成ESD路径。为了节约时间并更全面地模拟现实情况,通常对某一I/O引脚进行I/0引脚到I/O引脚的应力测试时,要将其他所有I/O引脚全部接地。电源VDD引脚和VSS引脚处于悬空状态

(3)VDD引脚到VSS引脚应力测试:电源引脚之间也存在正、负两种应力情况,在进行正电源VDD引脚到负电源VSS引脚的应力测试时,所有I/O引脚需处于悬浮状态

二、测试准备

(1)静电枪选择61000-4-2:2008标准,选择接触放电;

(2)暂定PS和NS模式

如下图,使用IEC61000-4-2?Model(深红色字体)方式,静电枪默认内阻50M。静电释放路径-->产品整机接地;

(3)分别选择正极冲击和负极冲击

正负极冲击分开进行各10次(每次间隔1秒),放电建议打完10次放1次电(产品和枪头接地)

(4)NSG?437静电枪放电

NSG?437静电枪支持空气放电:200v至30kv?(100v步进)或接触放电:200v至30kv?(100v步进)

选择接触放电,建议XX kv开始,以200v为步进,直接打在产品导电物质上(如金手指;

选择空气放电,建议XX kv开始,以1kv步进,打在PCBA绝缘物质上的多个固定位置(油墨上?提前划分好区域,便于管控及复现);

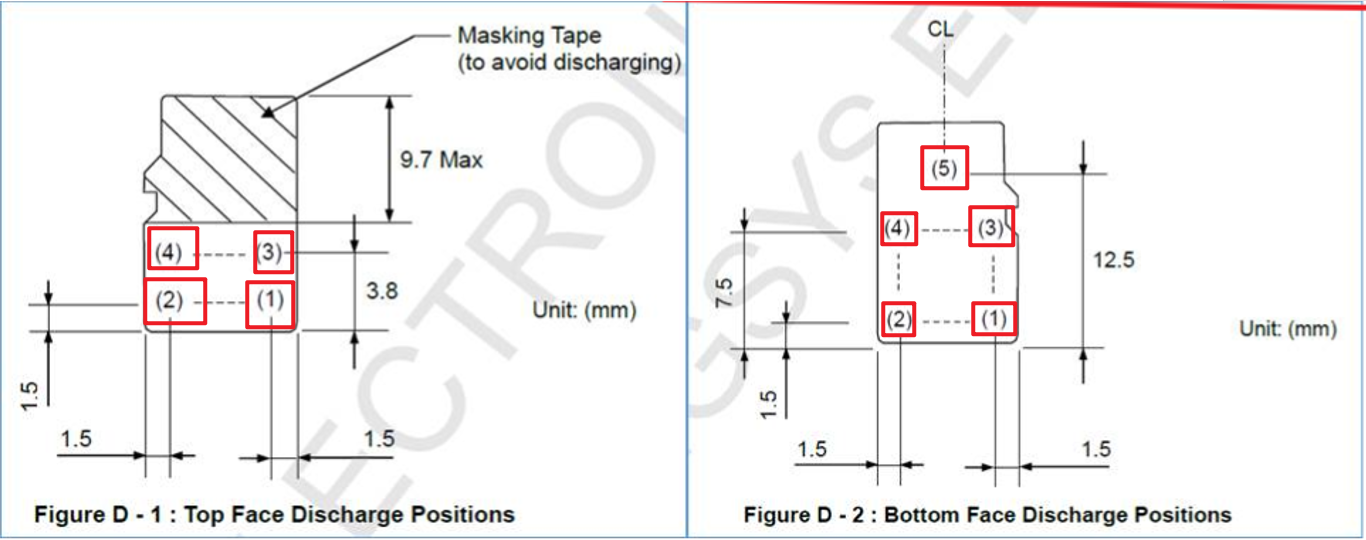

以下为MicroSD的空气放电点位图以供参考:

【注】:

①电压选择的参考标准:

EN301489-1(EMC测试规范)??第9.3章:接触放电的试验等级为±4kv,空气放电的试验等级为±8kv;

![]()

JESD22-A114-F-2008(HBM测试规范)?:接触放电的试验等级为±0.25kv~±8kv

IEC61000-4-2(IEC测试规范):接触放电的试验等级为±2kv/±4kv/±6kv/±8kv,空气放电的试验等级为±2kv/±4kv/±8kv/±15kv;

②到达一定的放电电压后观察一下是否拉弧,避免静电能量发散影响其他PIN

③?产品最高ESD电压测试:在每一测试模式下,DUT测试引脚先被打上某一ESD电压,而且在同一ESD电压下,IC的测试引脚需要被Zap三次,每次Zap之间的时间间隔约1秒,Zap三次之后再测试该引脚是否已被ESD所损坏(损坏的判断方式参照第三章),若DUT尚未被损坏,则按照每种模式规定的步进调升ESD的电压,再Zap三次,再测试,直到打坏样品——方法参考柯明道教授的ESD网站chap3-index?(nctu.edu.tw)

三、静电放电故障判断

在进行故障判断前需要妥善记录好样品的初始状态(电源及IO阻抗/IV曲线/IDD漏电流/开机标称频率等等)

(1)绝对漏电流:当IC被ESD测试后,其Input/Output脚的漏电电流超过1μA±30%。漏电电流会随所加的偏压增加而增加,在测漏电电流时所加的Breakdown?Point偏压有人用VDDX1.1,也有人用VDDX1.4

(2)相对I-V曲线漂移:当IC被ESD测试后,自Input/Ouput脚看进IC内部的I-V特性曲线漂移量在30%(20%或40%);

(3)功能观测法:?看DUT能否实现正常功能(电源阻抗是否正常,IO阻抗是否正常等等);

(4)芯片级分析:无损>SAT/X-RAY;有损>开盖分析

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- leetcode - 446. Arithmetic Slices II - Subsequence

- go语言(六)----slice

- 【异常】SecurityException: JCE cannot authenticate the provider BC

- 安防监控系统镜头选型分析,低噪声,低振动,多通道

- Javaassist:编写字节码,改变Java的命运

- 07. HTTP接口请求重试怎么处理?

- 汽车诊断软件开发

- 私域营销的误区:这几类企业你踩雷了吗?

- 【无标题】

- AR智慧校园三维主电子沙盘系统研究及应用