USB PHY for FPGA & layout

发布时间:2024年01月19日

https://blog.csdn.net/qq_41904778/article/details/123967670

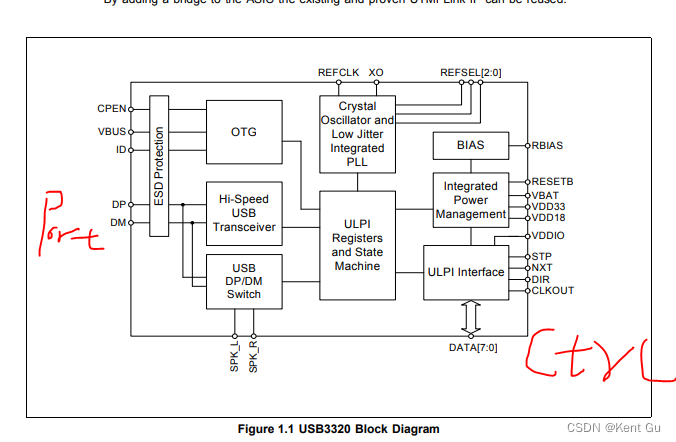

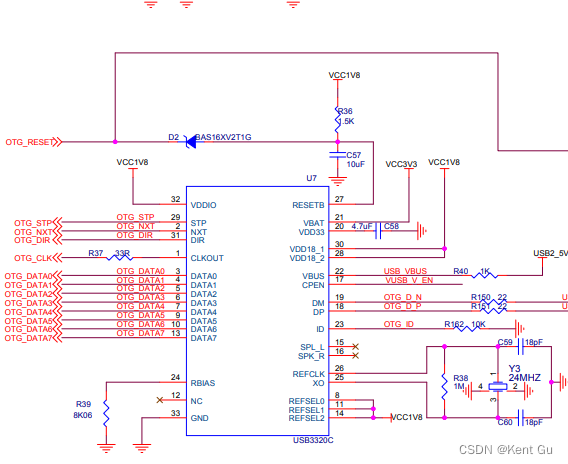

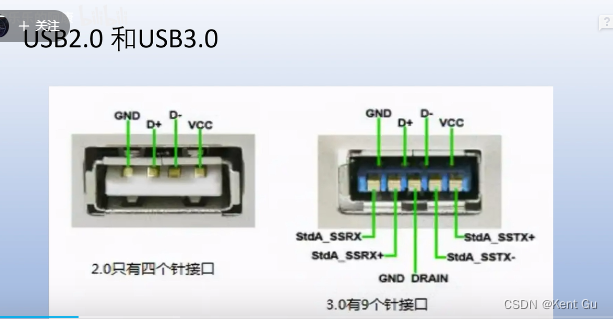

- ZYNQ7000内部没有USB PYH,我们通过USB 3320 PHY 芯片来连接FPGA 和外部的USB端口(DP+ & DP-)。

- USB 3320 PHY跟FPGA内部是t通过ULPI接口试下的,然后把数据转化为DP+、DP-模拟信号

- STM32内部带有了USB外设(PHY)

- 如网络芯片(PHY)就是把控制的RMI(其中的一种)转化为Tx_P/N, Rx_P/N.

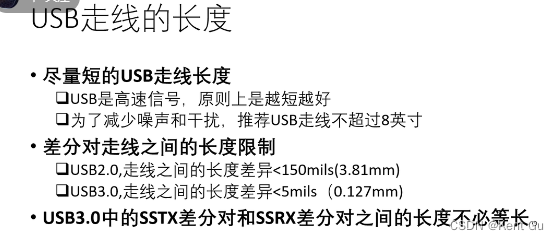

5. USB PCB layout

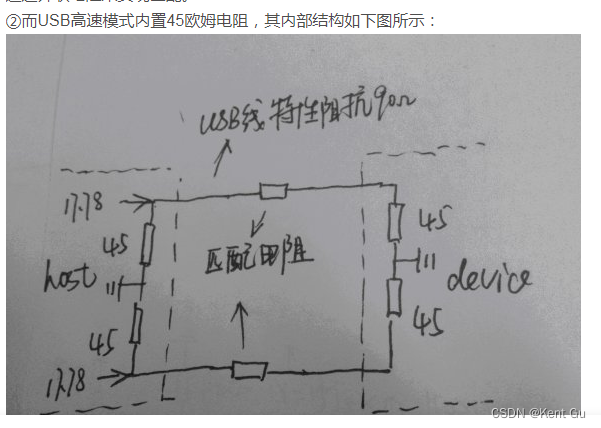

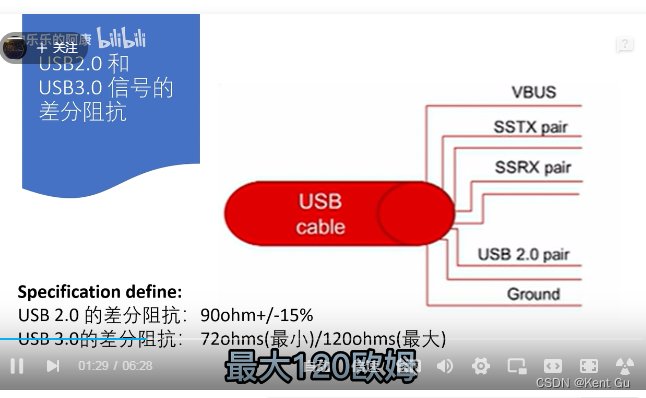

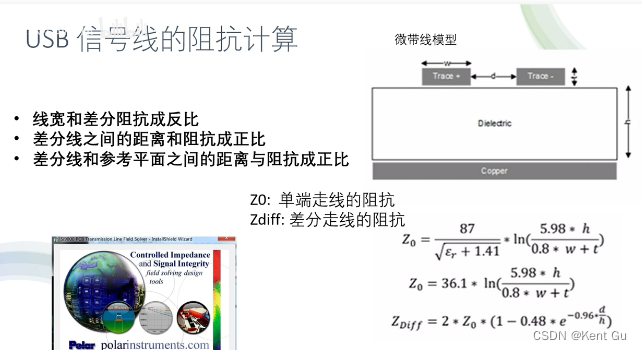

USB2.0 DP/DP-USB特征阻抗90Ω

总结:低速和全速时最好进行阻抗匹配 源端串联或终端并联90ohm ,高速时不需要。

匹配方式有:串联匹配、并联匹配、戴维南匹配等

USB全速驱动器的输出阻抗一般比较小,若输出阻抗<特性阻抗则可以通过串联电阻来实现匹配,E330使用iMX258处理器,其全速Host的输出阻抗Rs厂家预计为10ohm,而USB线的差分特性阻抗为90ohm,所以要实现驱动器和USB线的阻抗匹配必须在USB D+和D-上串联电阻,串联电阻的要求为Rs 10Ω+R串=USB线特性阻抗90Ω;当阻抗>特性阻抗时则要通过并联电阻来实现匹配

高速匹配阻抗=0

在低速和全速模式下是电压驱动的,驱动电压为3.3V,但在高速模式下是电流驱动的,驱动电流为17.78mA

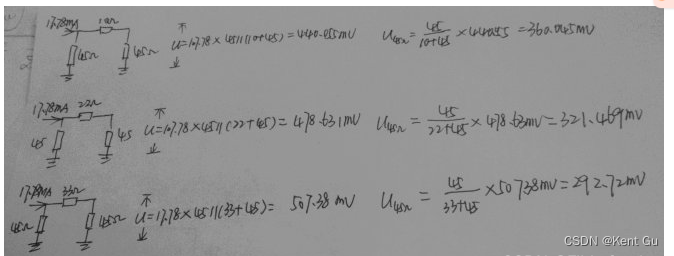

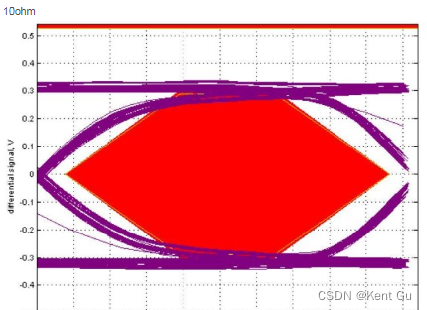

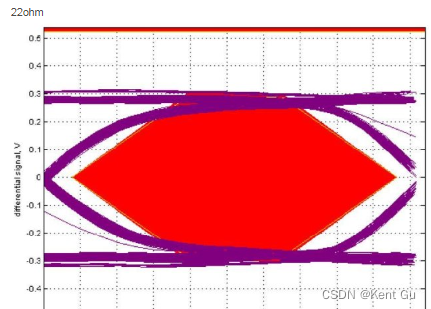

Host和device的D+和D-都有45ohm的电阻端接到地,所以每根线的并联电阻为22.5ohm,17.78x22.5=400mV,所以高速模式下的差分幅度为800mV (这时匹配电阻为0),但是匹配电阻选择10ohm,22ohm和33ohm时我们可以计算出单端信号的幅度如下图:

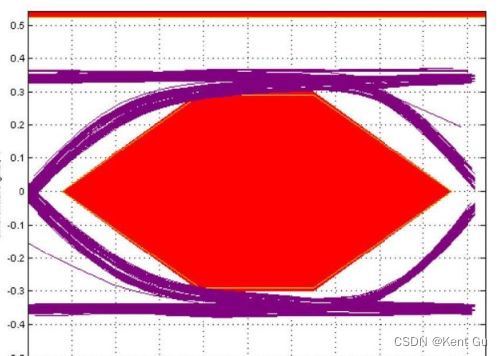

高速模式下加入匹配电阻会使信号幅度下降,使信号质量变差,加入匹配电阻后的眼图分别如下(紫色线与红色区域交叉越多,说明分界越明显,数据越容易出错

)

文章来源:https://blog.csdn.net/weixin_39305628/article/details/135692465

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 基于java的动漫论坛系统设计与实现

- 电子合同在物流运输中的场景应用

- 一、引言( C#与.NET框架的关系)

- EduChat账号密码登录

- 游戏策划:游戏开发中的关键环节

- GroupMixFormer:Advancing Vision Transformers with Group-Mix Attention论文学习笔记

- Jenkins实战指南:实现自动化代码拉取和Harbor私有镜像仓库上传

- python中threading多线程作用域及用法

- 数据结构实验八:排序的应用

- 【栈】LeetCode-10. 正则表达式匹配