verilog基础语法-计数器

发布时间:2023年12月17日

概述:

计数器是FPGA开发中最常用的电路,列如通讯中记录时钟个数,跑马灯中时间记录,存储器中地址的控制等等。本节给出向上计数器,上下计数器以及双向计数器案例。

内容

1. 向上计数器

2.向下计数器

3.向上向下计数器

1. 向上计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

output [3:0] y1 // output signal

);

reg [3:0] up_cnt;

assign y1 = up_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

up_cnt <= 0;

else if (en_clk)

if (load_enable)

up_cnt <= load_data;

else

up_cnt <= up_cnt + 1;

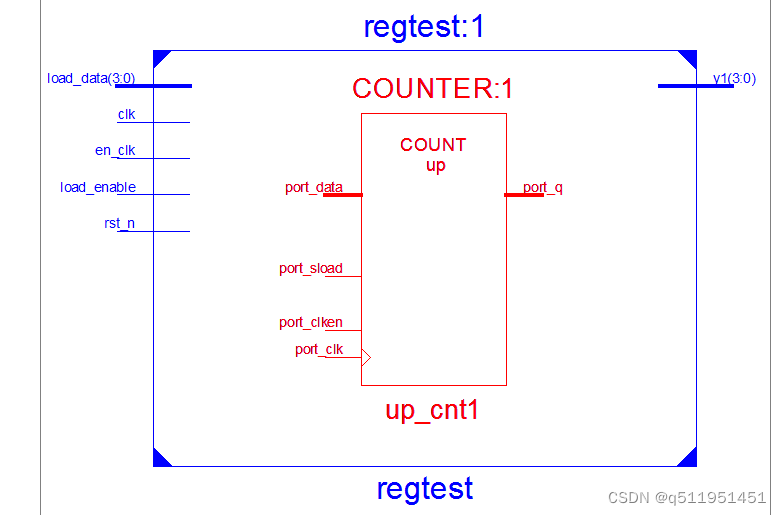

endmoduleRTL结构图

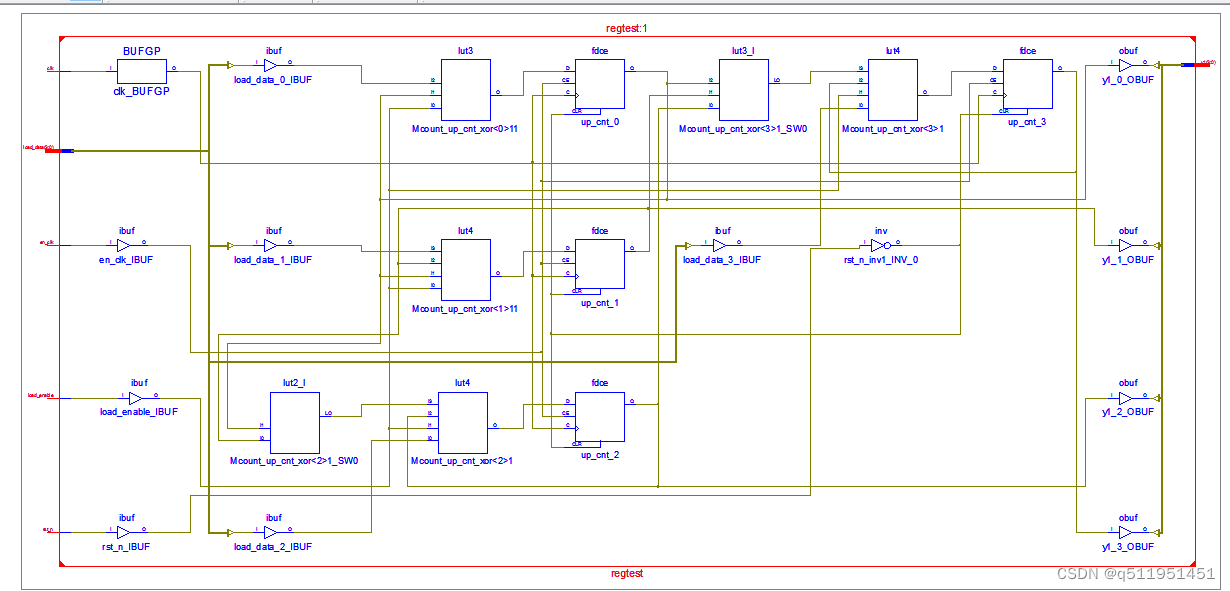

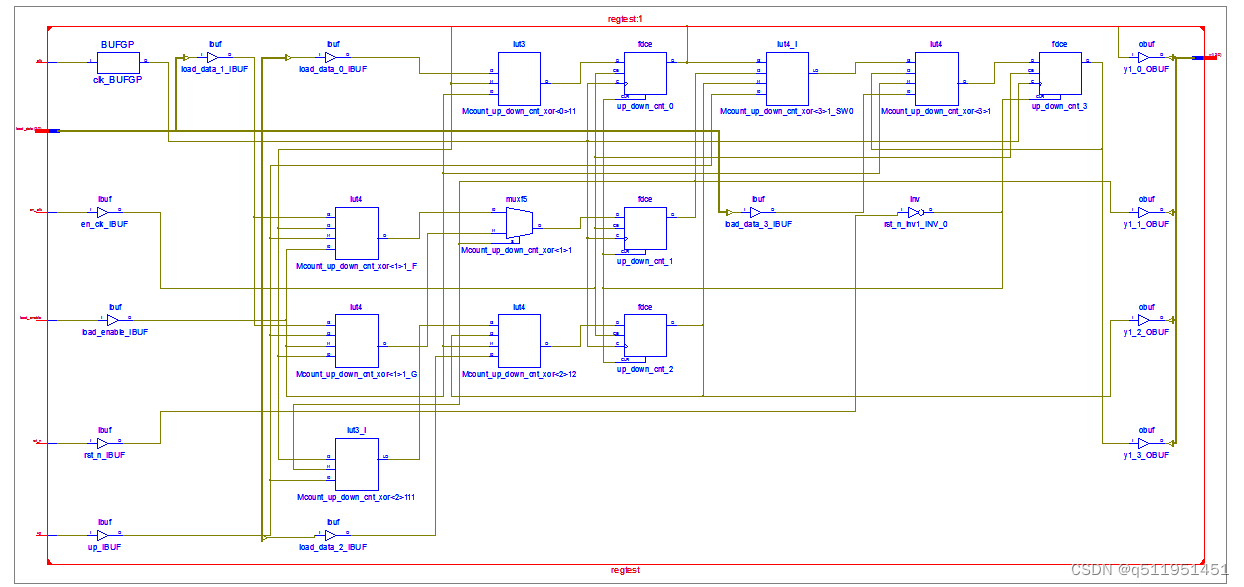

技术原理图,基本的计数器结构是由触发器与组合逻辑来设计的,在FPGA中触发器有fdc来实现,组合逻辑使用lut查找表来实现,

2.向下计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

output [3:0] y1 // output signal

);

reg [3:0] down_cnt;

assign y1 = down_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

down_cnt <= 0;

else if (en_clk)

if (load_enable)

down_cnt <= load_data;

else

down_cnt <=down_cnt- 1;

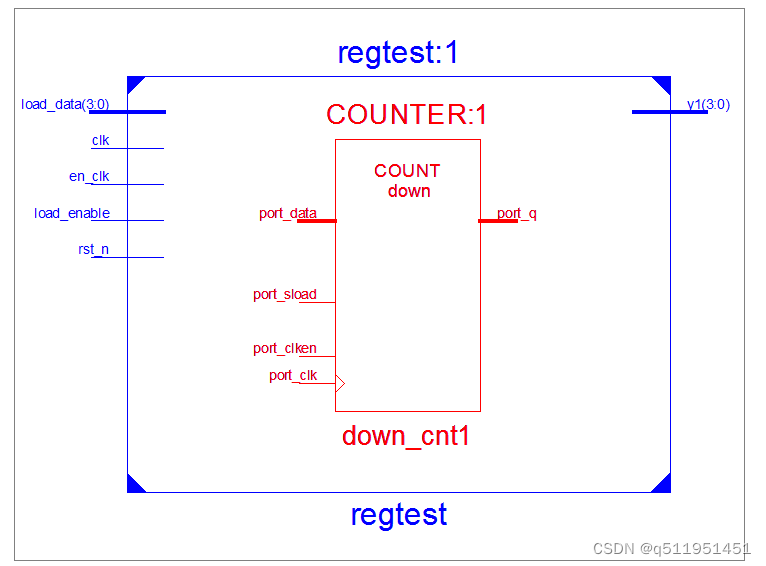

endmoduleRTL结构图

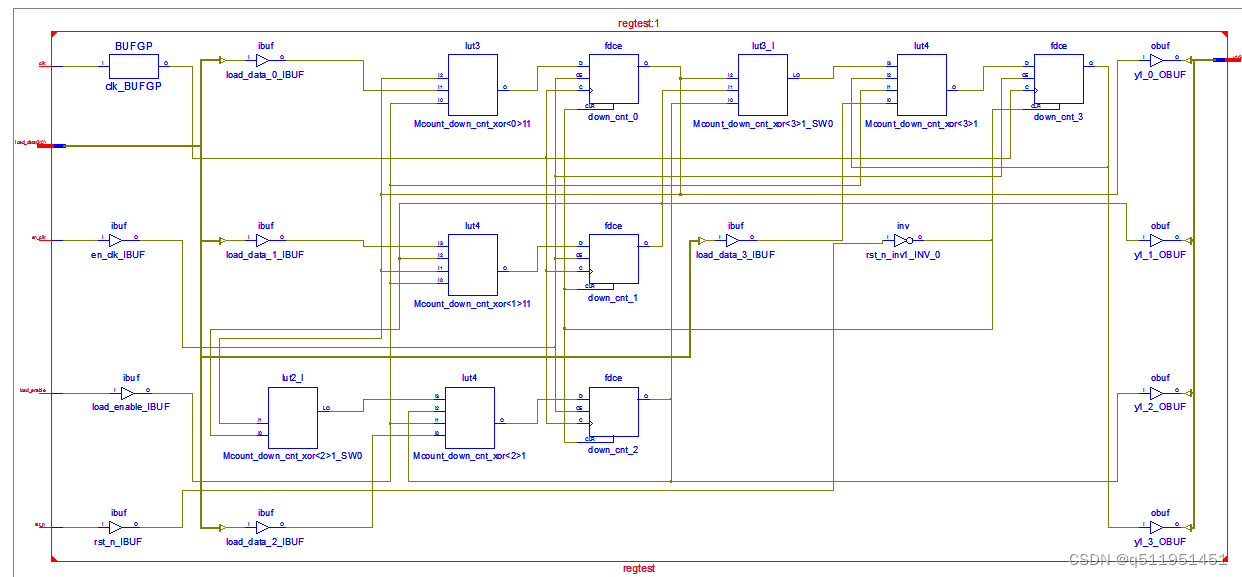

技术原理图

3.向上向下计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

input up,

output [3:0] y1 // output signal

);

reg [3:0] up_down_cnt;

assign y1 = up_down_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

up_down_cnt <= 0;

else if (en_clk)

if (load_enable)

up_down_cnt <= load_data;

else if (up)

up_down_cnt <=up_down_cnt+ 1;

else

up_down_cnt <=up_down_cnt- 1;

endmodule

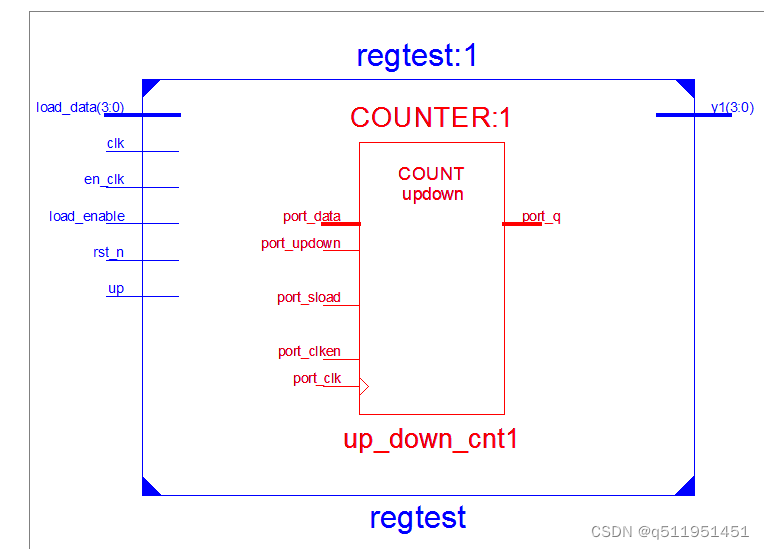

RTL结构图

技术原理图

总结:

计数器是基础,要理解它的设计电路图。

文章来源:https://blog.csdn.net/q511951451/article/details/135011980

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 鸿蒙原生应用/元服务实战-DevEco Studio 模拟器资源经常不足

- 【OJ题录】最大abcd(C++实现)

- async&await用法

- idea识别不了项目目录,而且报内存溢出错

- Windows 7错误恢复一直循环怎么办?

- 青龙面板的安装

- 【AI】使用LoFTR进行图像匹配测试Demo

- xv6 文件系统(上)

- burpsuite专业版破解2023.5.21教程并配置抓包(保姆级)

- 大模型、AI-Agent、langchain之间的关系