高速电路设计之单一网络的信号完整性

在上篇博客中,我们给出了高速电路领域的信号完整性、电源完整性、电磁兼容问题的6种分类,分别是:

1.单一网络的信号失真;

2.互连线中频率相关损耗引起的上升沿退化;

3.两个或多个网络之间的串扰;

4.作为串扰特殊形式的地弹和电源弹;

5.电源和地分配中的轨道塌陷;

6.来自整个系统的电磁干扰和辐射;

本篇博客将对上述6条中的第一条“单一网络的信号失真”做详细解析。

网络是由一个系统中所有连接在一起的金属组成,其中不仅仅包括信号的传输路径,还包括信号电流的返回路径。

图一

在单一网络中,噪声的最主要来源是反射:

引起反射的唯一原因是信号遇到的瞬时阻抗(也即传输线的特性阻抗)发生改变。如果有不清楚特性阻抗概念的小伙伴,可以观看我发在b站上的视频:

90%的电路小白都误解的概念---“阻抗匹配”三页ppt带你彻底搞懂_哔哩哔哩_bilibili

当信号从发射端口输出时,构成信号的电流和电压将互连线看成一个阻抗网络。当信号沿着网络传播时,它不断感受着互连线的瞬时阻抗。如果互连线的瞬时阻抗恒定,则信号不会失真。然而,一旦阻抗发生了改变,信号就会在变化处产生反射,并会不断地积累失真信号。如果阻抗变化程度较大,那么失真将会导致误触发。

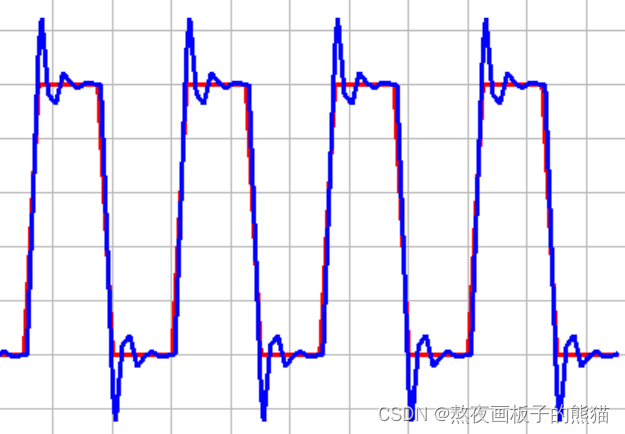

图二

以下6种情况,是信号在传输时,感受到瞬时阻抗发生改变的主要来源:

1.互连线末端

2.线宽变化

3.层转换

4.返回路径平面的间隙

5.接插件

6.路由拓扑的改变,比如分支线、T形线或者桩线。

图三

上图为不同角度走线导致的线宽变化示意图,很明显在拐角处,走线线宽产生了明显的变化,这便是导致阻抗不连续的一个重要原因。

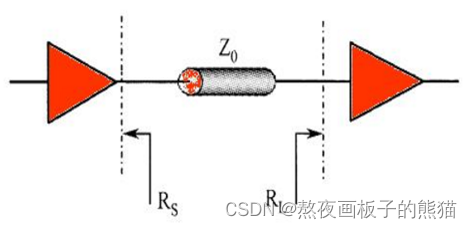

通常情况下,阻抗突变大多是由横截面、布线拓扑结构或附加元件产生的。最常见的突变发生在线条的末端处,通常遇到的是接收器的开路高输入阻抗或驱动器的低输出阻抗。

图四

为了使信号传输时感受到的瞬时阻抗恒定不变,减少信号反射产生的干扰,我们常常采用以下4种措施来优化设计。

1.使用互连线阻抗为常量或所谓的“可控的”电路板,也即使用均匀的传输线。

2.为了控制末端的反射,采用电阻器的端接匹配策略去控制反射,让信号看不到阻抗有变化。

3.使用沿线拓扑的阻抗维持恒定的布线原则。可以采用点到点布线、最小化支路长度、短桩线等。

4.设计不均匀的传输线结构,以减轻线的不连续性。要对线的几何特征进行精细设计,以修整边缘场。

图二分别给出了同一网络种有阻抗突变时的信号质量(产生了振铃现象)和使用端接电阻控制阻抗变化的信号质量(无异常)。

即使是端接完善的精密电路板布局,也能严重地影响信号质量。例如,当线条分为两路时,节点处地阻抗发生变化。一部分信号反射回信号源,另一部分信号继续沿着分支传播,但产生衰减和失真。如果以菊花链的方式重新布线,则能使信号沿着路径所感受到的阻抗保持不变,信号质量也得以恢复。

图五 菊花链示意

除了传输线,随着信号频率的升高以及上升边的缩短,器件封装也要采用可控阻抗(如引线架),如多层球栅阵列(Ball Grid Arrays,BGA)。如果没有,就要使引线尽量短,如芯片最小尺寸封装(Chip-Scale Package,CSP)。

在后续的博客中,我会继续针对高速电路领域的信号完整性、电源完整性、电磁兼容问题的6种分类进行逐一讲解,喜欢我的内容的朋友可以点个关注,我们会继续保持高强度更新!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!