ug871 Lab3

发布时间:2023年12月18日

实验平台

????????Vitis?HLS 2021.2

? ? ? ? Windows 10

实验内容

????????对Lab1的设计进行优化,优化目标如下:

- 吞吐量最高

- 能够处理输入信号提供的有效数据

- 产生输出数据并伴随一个有效的输出信号

- 滤波器系数将存储在FIR设计外的单端口RAM中

实验步骤

Step 1:创建一个新的工程

- 打开HLS命令行

- 将Lab2的run_hls.tcl和src文件夹移动到Lab3文件夹。

- cd到Lab3文件夹下,然后执行vitis_hls -f run_hls.tcl生成项目文件

- 执行vitis_hls -p?fir_prj打开Vivado的HLS GUI。

Step 2:优化I/O接口

- 端口设置的要求:

- 端口C必须有一个单独的RAM访问权限。

- 端口X必须有一个输入数据有效信号。

- 端口Y必须有一个输出数据有效信号。

- 创建solution2

- 点击Project

- 点击New Solution

- 点击Finish

- 将solution2设置为激活状态,就是solution2字体加深即可

- 添加优化指定定义所需的I/O接口

- 点开fir.cpp文件

- 点击左侧的Directive选项卡

- 实现 port c

- 双击该选项卡的中c

- 选中Destination中的Source File

- 在Directive下拉选项卡中选中BIND_STORAGE

- UG871需要选择RAM_1P_BRAM,而21版本的HLS中没有这个,用了以下的方法

- impl的选项卡中bram

- type的选项卡中选中ram_1p

- 点击OK

- 实现port x

- 双击x

- 在Directive下拉选项卡中选中INTERFACE

- 选中Destination中的Source File

- 选中mode选项卡中的ap_vld

- 点击OK

- 实现port y

- 同port x。

- 点击Run C Sythesis

Step 3:结果分析

- 点击Schedule Viewer

- 点开Shift_Accum_Loop

Step 4:优化最高吞吐量

- 限制吞吐量的因素有

- for循环使得前后按顺序执行,可以全部展开以允许所有操作并行。

- 块RAM被用于shift_reg。因为该变量是数组,因此,它被默认实现为一个块RAM。因此,可以将这个块RAM划分为单独的寄存器。

- 新建一个solution3

- 点击fir.c

- 双击Shift_Accum_Loop部分

- 选中Unroll

- 点击OK

- 双击shift_reg

- 选中Array_Partition

- 点击OK

- 点击solution3

- 点击constraints

- 点击directives.tcl

- 点击run C Synthesis

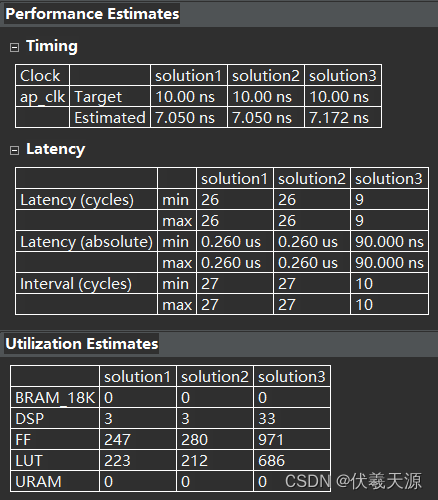

- 多个solution之间进行比较

- 点击Project选项卡

- 点击Compare Reports

- 添加solution1、solution2、solution3

文章来源:https://blog.csdn.net/qq_43209828/article/details/132693932

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Web前端 ---- 【Vue3】computed计算属性和watch侦听属性(侦听被ref和reactive包裹的数据)

- PyTorch——torchtext与PyTorch匹配的版本

- 安科瑞ARTM系列-无线测温解决方案

- 力扣322. 零钱兑换(java语言实现 完全背包问题)

- 19--集合框架

- YOLOv7 目标检测论文解释和推理

- JavaFX场景入门

- 【K8s】#1使用kuboard-spray安装K8s集群

- k8s的陈述式资源管理

- Harmonyos系统列表组件和video组件的使用