如何使用synplify综合vivado IP

摘要:肯定是可以综合的,但是不能直接把vivado ip放到synplify里面进行综合;而是把用到vivado ip的地方先设置成黑盒,让synplify不去分析;等到生成edf文件之后,把edf文件放到vivado中与相关ip进行link,这样才能够生成最终的bit;

我遇到的问题一般都是imp的时候,没有black box;问题和解决方法如下:

[DRC INBB-3] 黑匣子实例:单元格“...”具有未定义的内容,被视为黑匣子。必须定义此单元格的内容才能使 opt_design 成功完成。

Vivado如何处理Synplify pro生成的EDF网表内的黑盒?

1.vivado生成IP

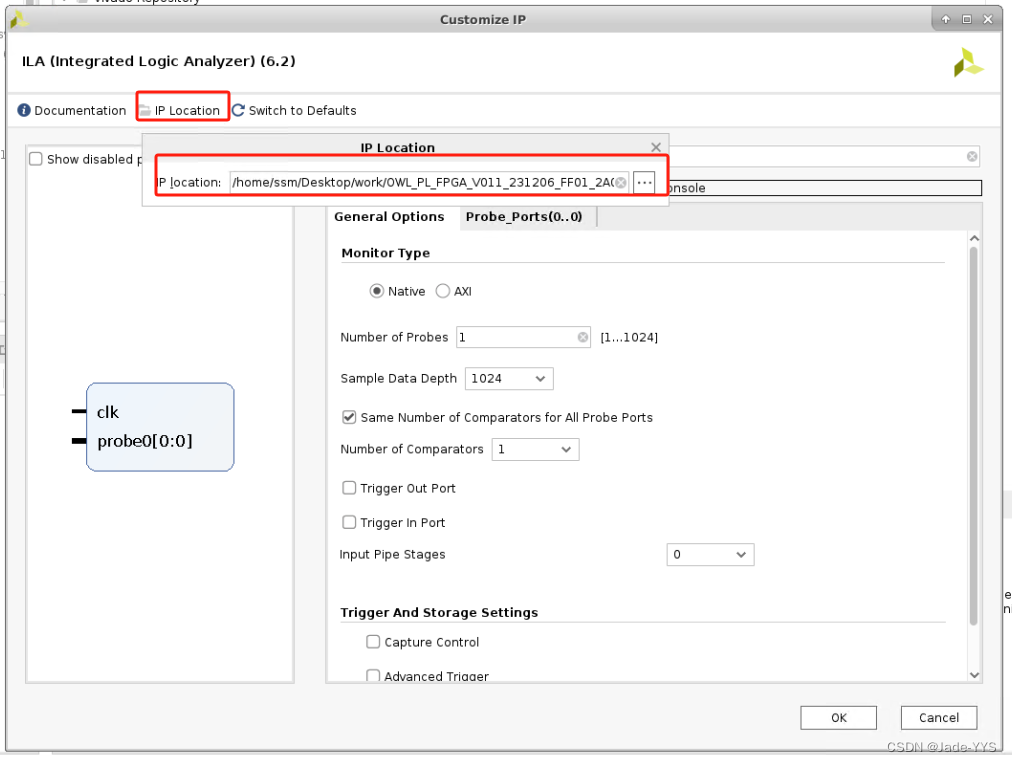

一般情况下,指定一个路径生成IP:

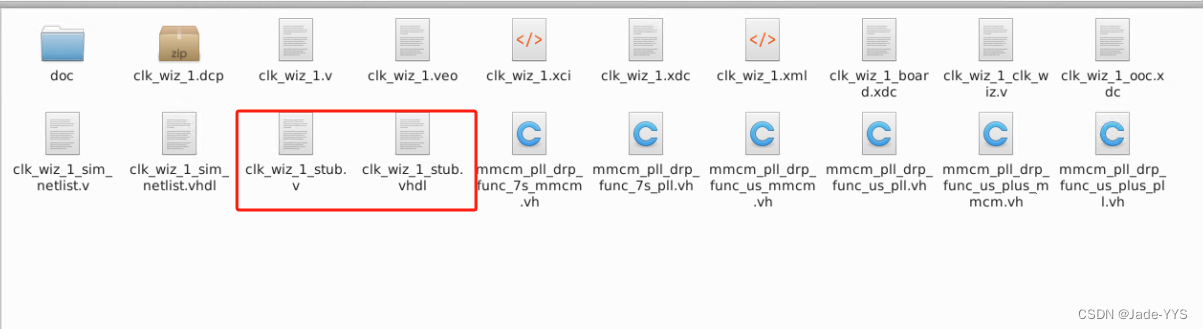

就会得到这些文件,需要的就是*stub.v或者*stub.vhdl:

2.添加文件到synplify

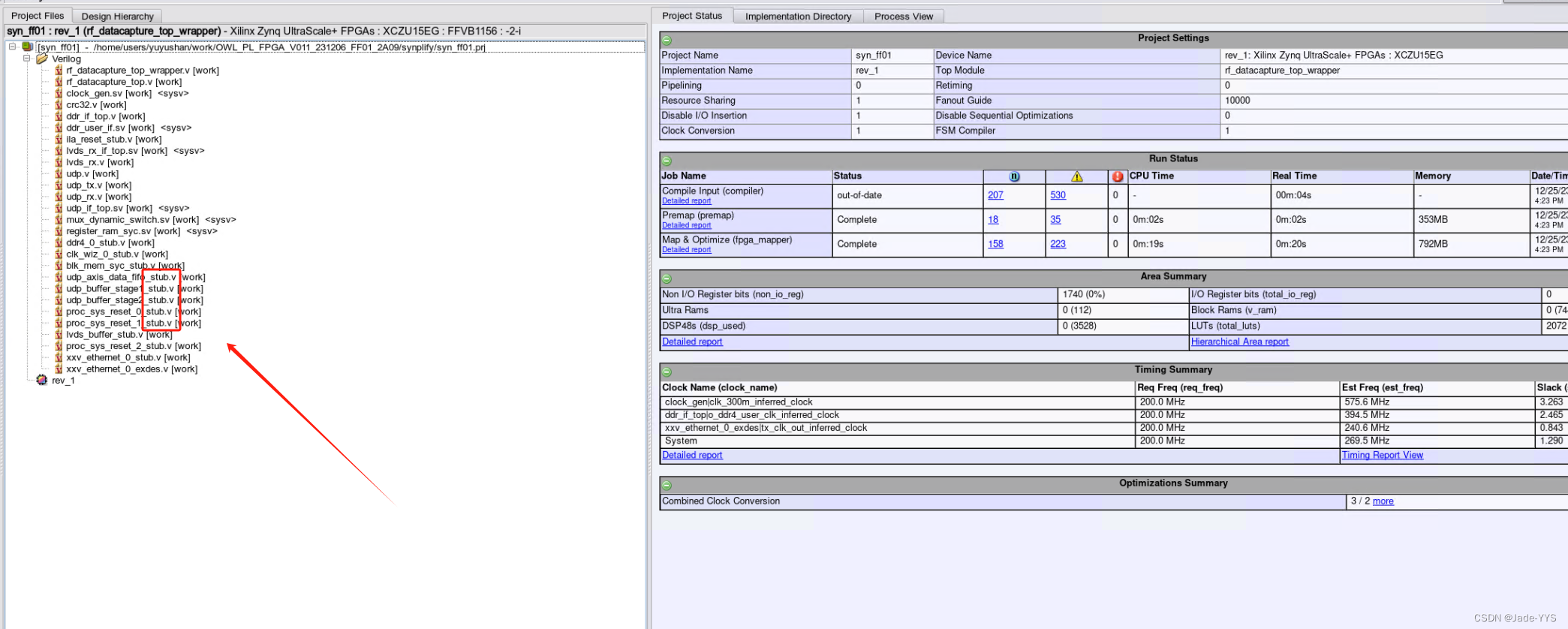

在使用IP的地方添加对应的stub.v或者stub.vhdl;

运行run之后会成功生成edf;

(可以在报告中看到,所有使用IP的地方全都是blak box的warning)

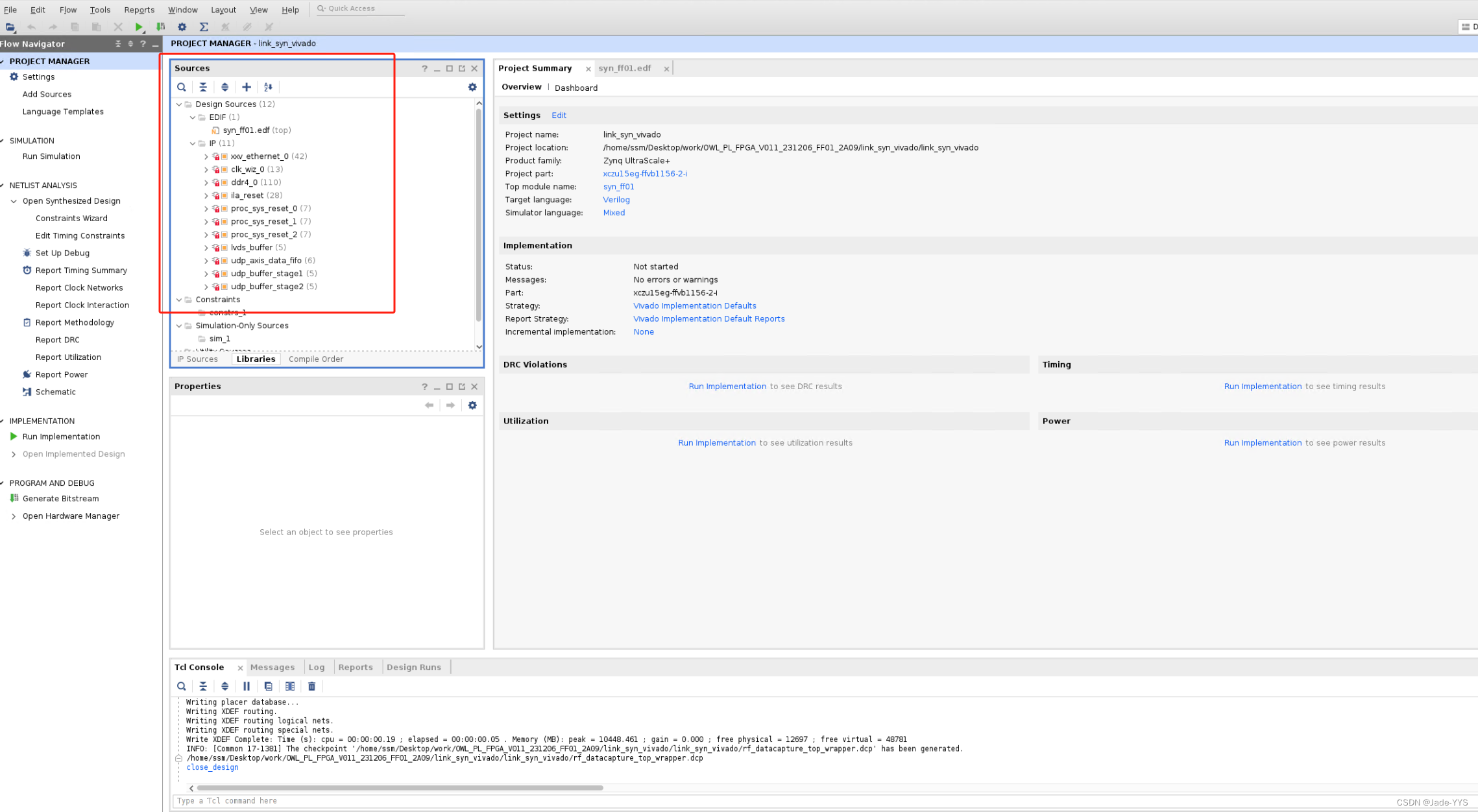

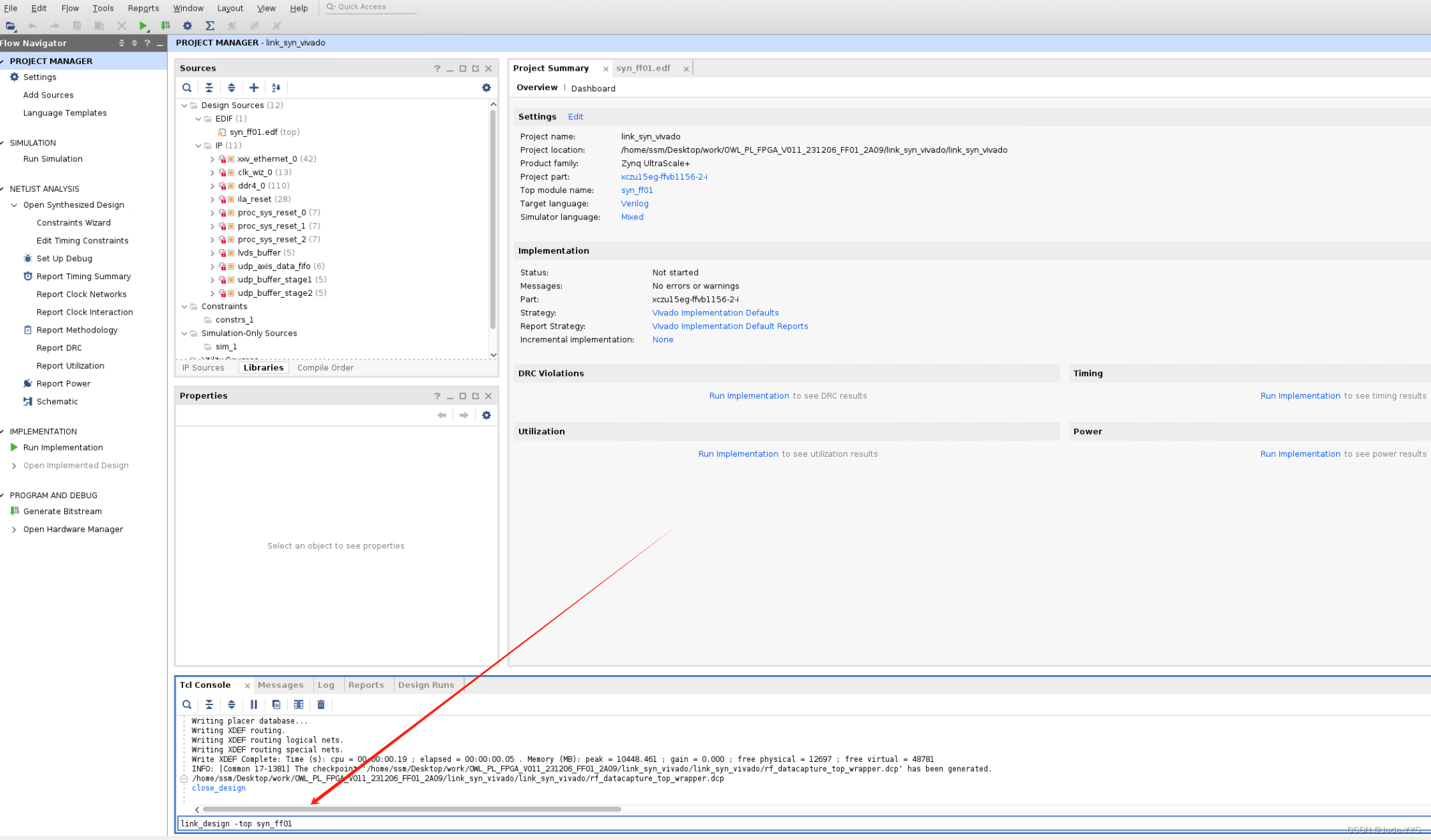

3.link_design

最好是单独建一个工程,不然原来的工程link design之后没有办法复原(我没发现怎么解决)

添加synplify生成的edf文件

添加edf使用到的所有IP

然后在Tcl Console里面输入:

link_design -top syn_ff01

(syn_ff01是我的edf文件名)

(xilinx回复中提到使用link_design -part XX -top XX,-part我的理解是一个一个IP添加吧,比较慢,好像我测试下来没有必要加-part)

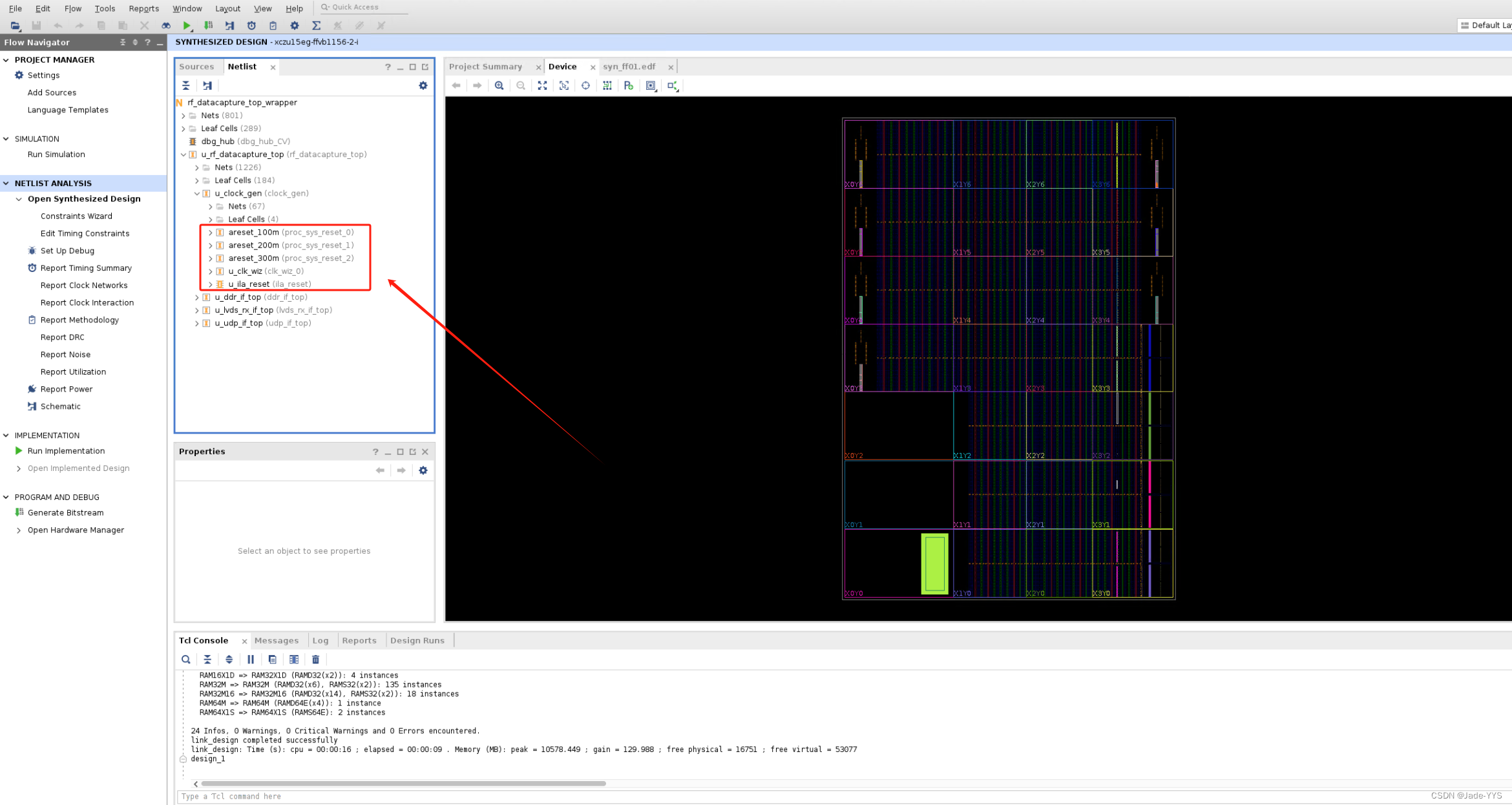

成功运行后就表明link成功了;

随后可以检查一下IP是否存在:

这种颜色就代表添加成功了;

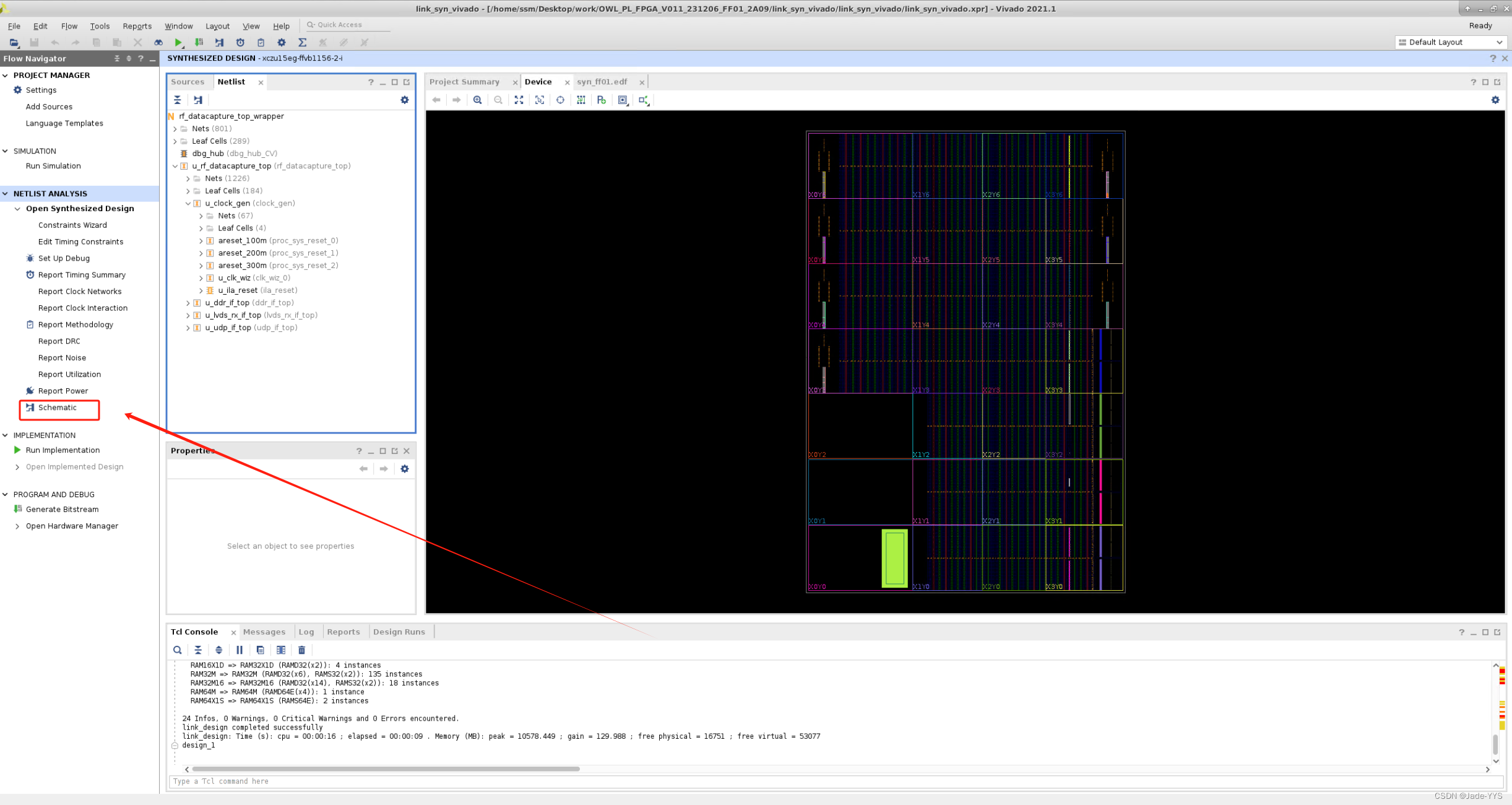

4.生成dcp文件或者edif文件

link成功之后需要借助这个link的工程导出dcp或者edif或者edf(edf没试过,但是感觉也行)

先要打开schematic:

然后在tcl console里面输入:

write_checkpoint XX.dcp

或

write_edif XX/XX.edif

生成edif和生成edf文件应该都需要一个.v进行配合;

不明白的可以去搜索edf的生成流程;

并且A.edf文件和A.v应该是平级文件;

(生成dcp合edif的文章很多,可以自行搜索)

参考文章:

Using AMD IP with Third-Party Synthesis Tools

[DRC INBB-3] 黑匣子实例:单元格“...”具有未定义的内容,被视为黑匣子。必须定义此单元格的内容才能使 opt_design 成功完成

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【Proteus仿真】【51单片机】自动除湿器系统

- Arduino stm32 USB CDC虚拟串口使用示例

- 喜讯|极狐GitLab 通过信通院汽车软件研发效能成熟度模型能力

- python基础语法总结

- Octomap使用记录

- 【R语言爬虫】使用rvest包爬取豆瓣读书Top 250,仅需50行代码(速度挺快)

- 【工具使用-A2B】32通道24bit传输的配置方法

- 统计出现过一次的公共字符串

- H5页面使用微信授权登录开发记录

- kubernetes面试之calico网络组件的实现原理