瑞萨e2studio(29)----SPI速率解析

概述

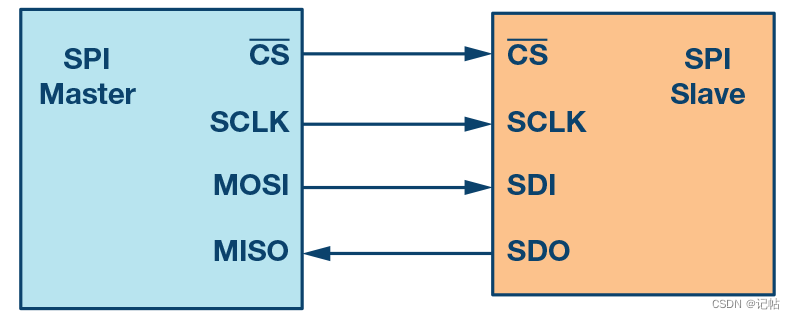

在嵌入式系统的设计中,串行外设接口(SPI)的通信速率是一个关键参数,它直接影响到系统的性能和稳定性。瑞萨电子的RA4M2微控制器为开发者提供了灵活而强大的SPI配置选项,确保可以根据不同的应用场景选择最佳的数据传输速率。本文将深入探讨RA4M2微控制器的SPI速率配置机制,并提供实用指南以帮助开发者实现精确的速率控制。

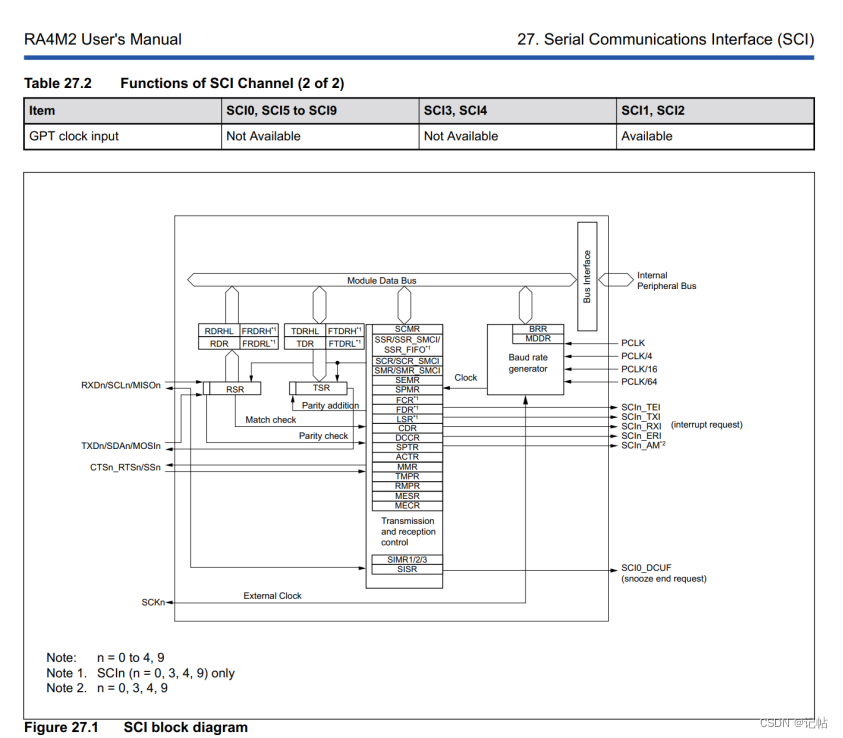

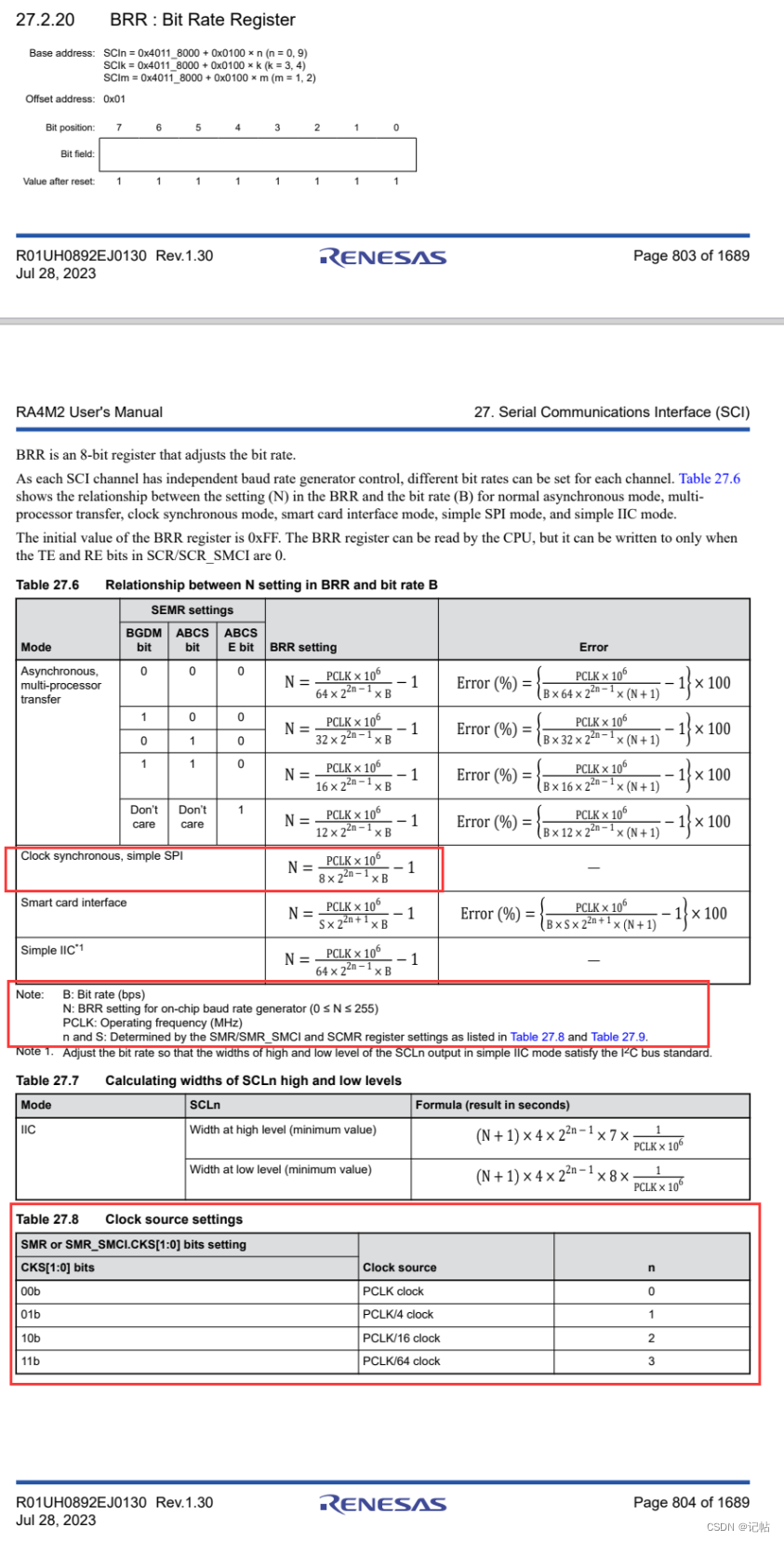

下面文档是瑞萨RA4M2微控制器用户手册中的一部分,显示了串行通信接口(SCI)的功能和其内部模块图。

时钟来源为PCLK,可以进行1、4、16、64分频。

最近在弄ST和瑞萨RA的课程,需要样片的可以加群申请:615061293 。

视频教学

听不到声音的请点击跳转进行观看。

样品申请

https://www.wjx.top/vm/wBbmSFp.aspx#

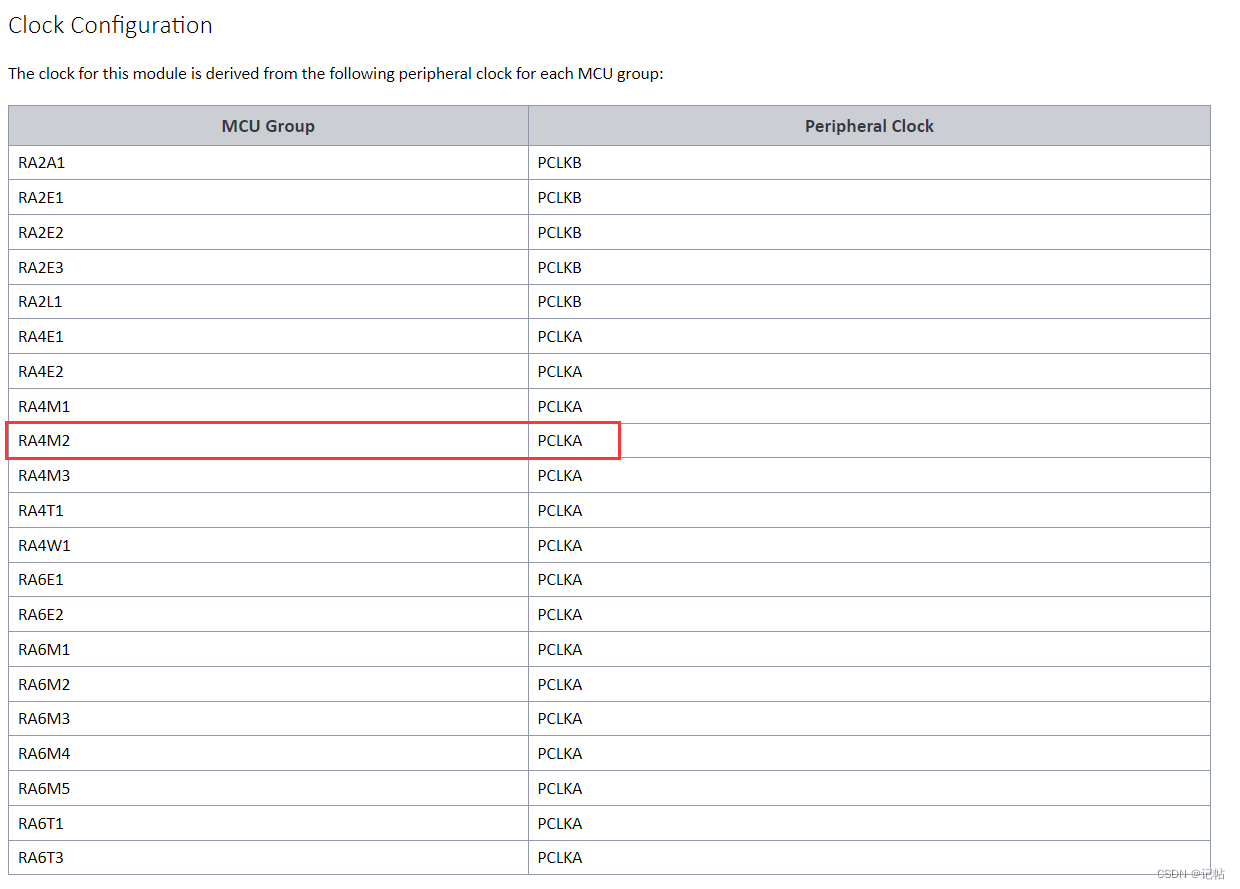

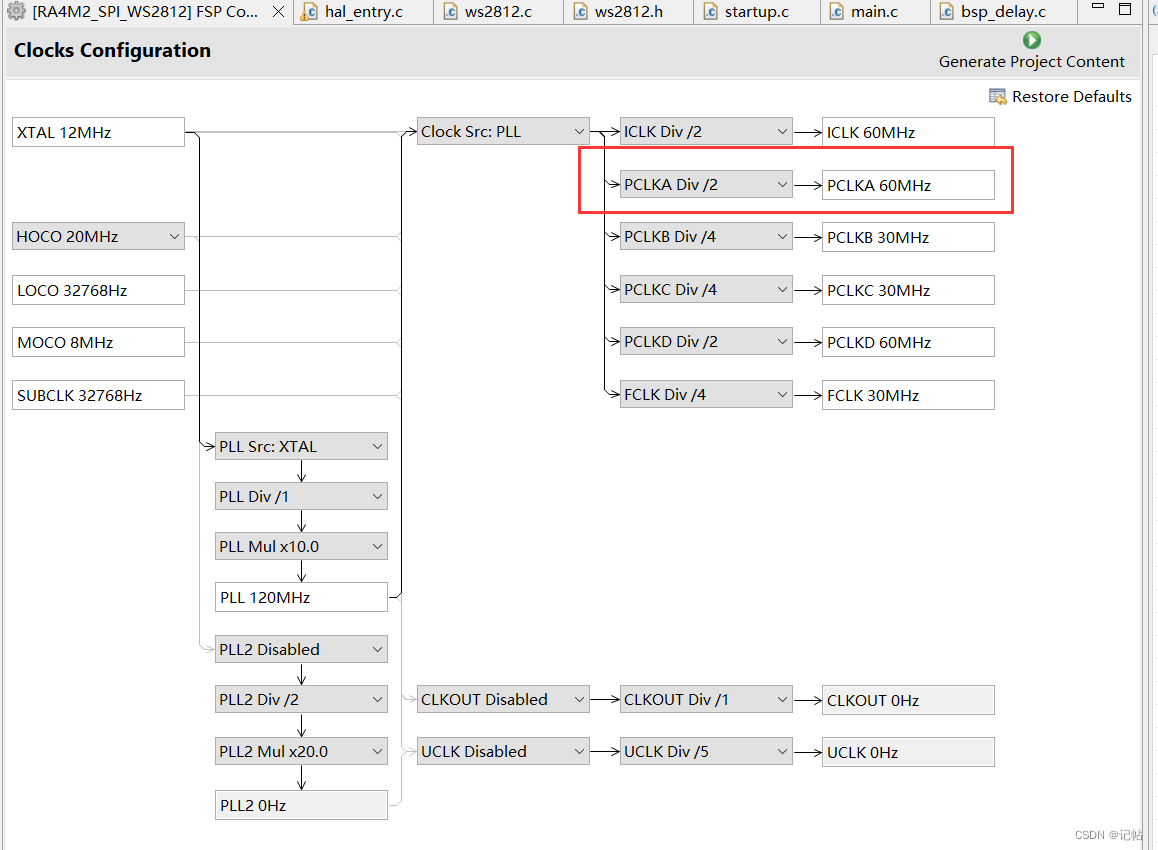

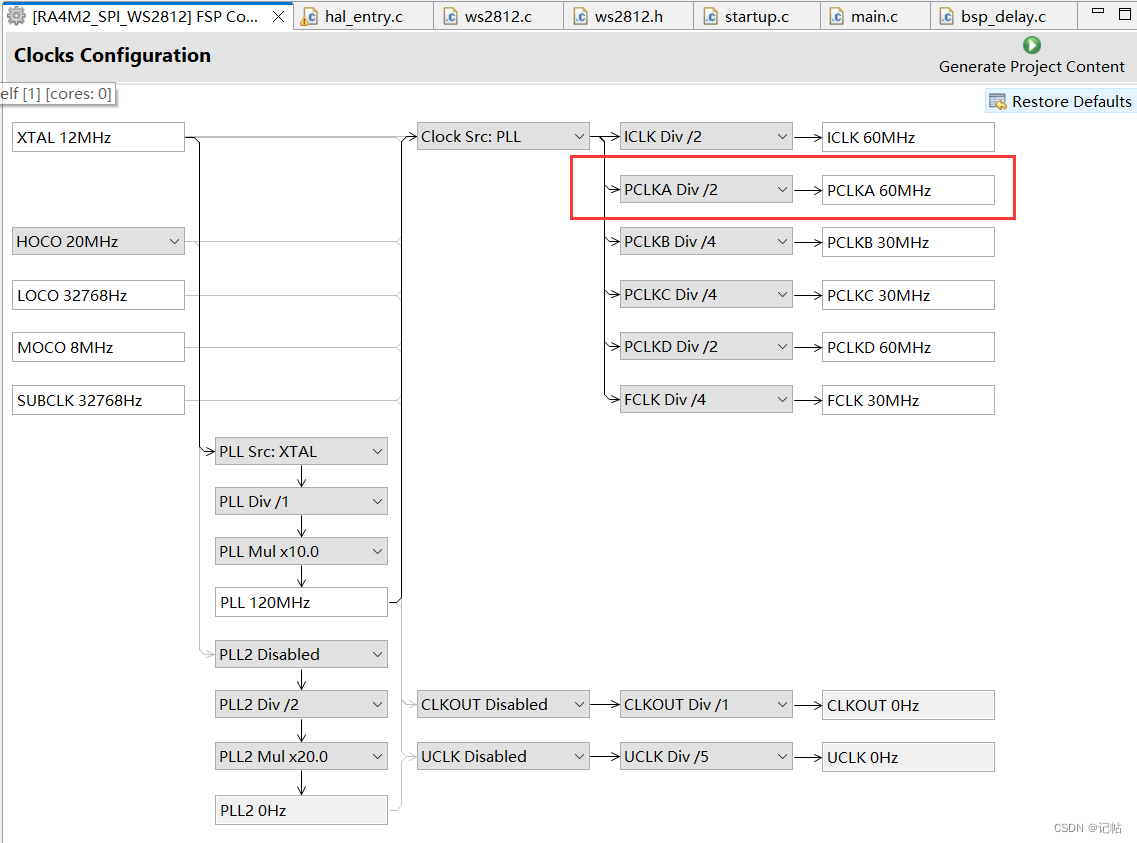

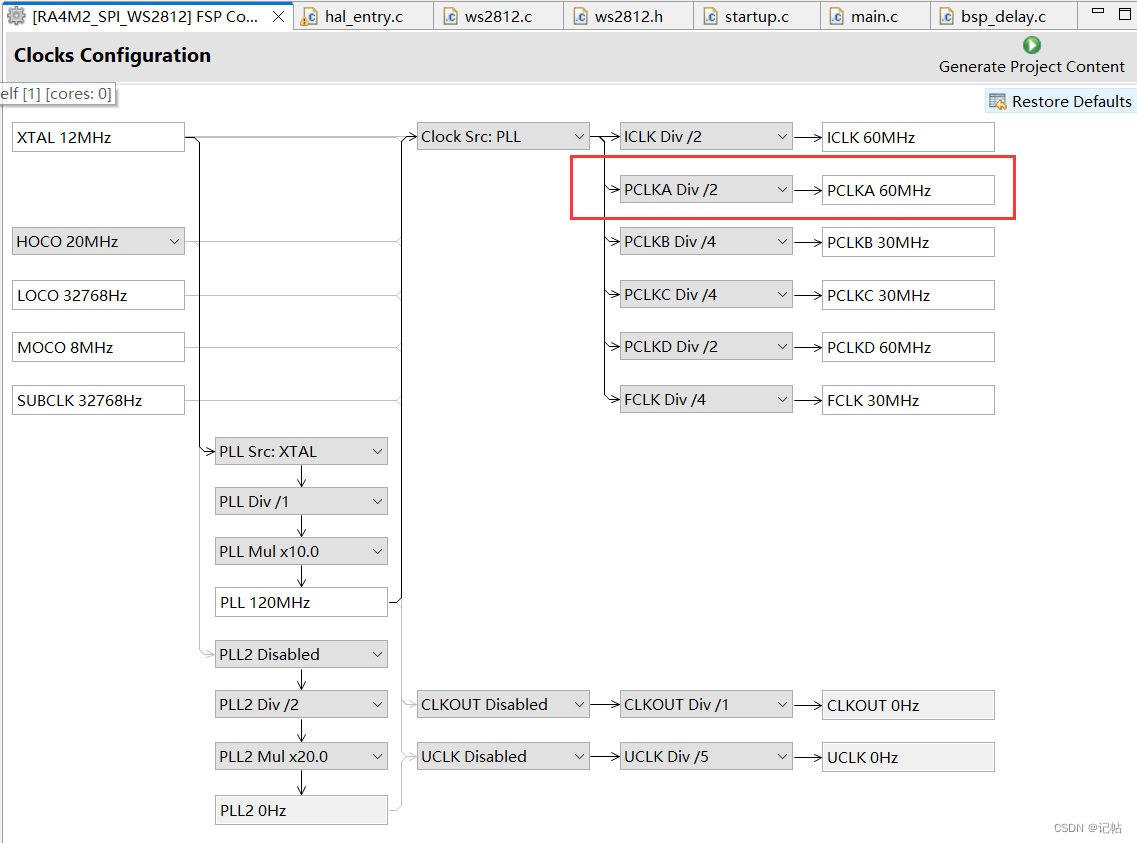

时钟配置

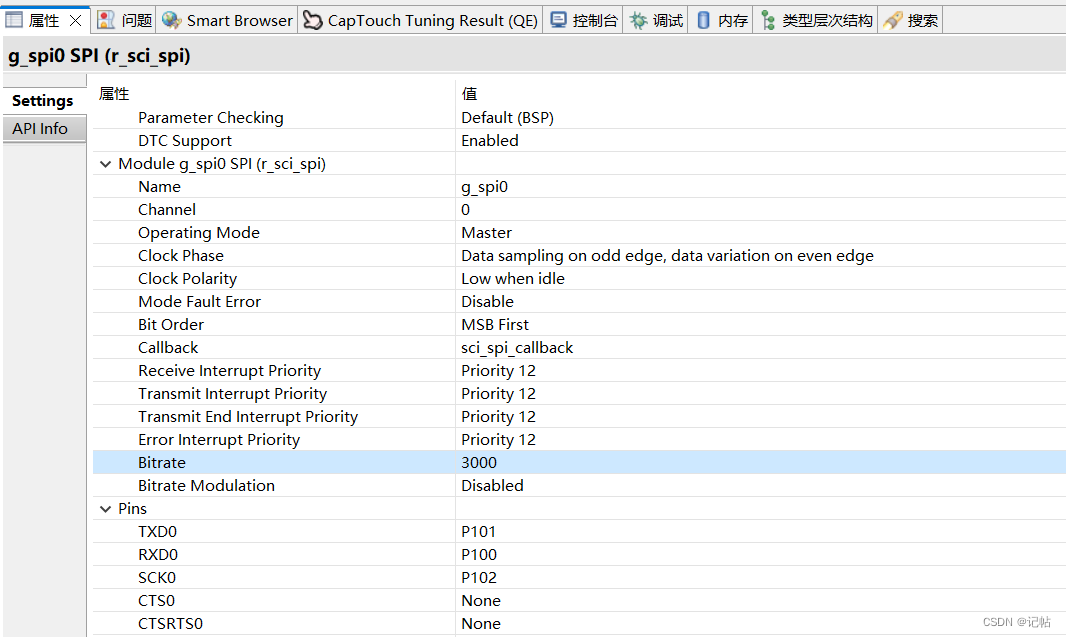

SPI (r_sci_spi)的时钟来自PLCKA。

这里使用的PLCKA为60MHz。

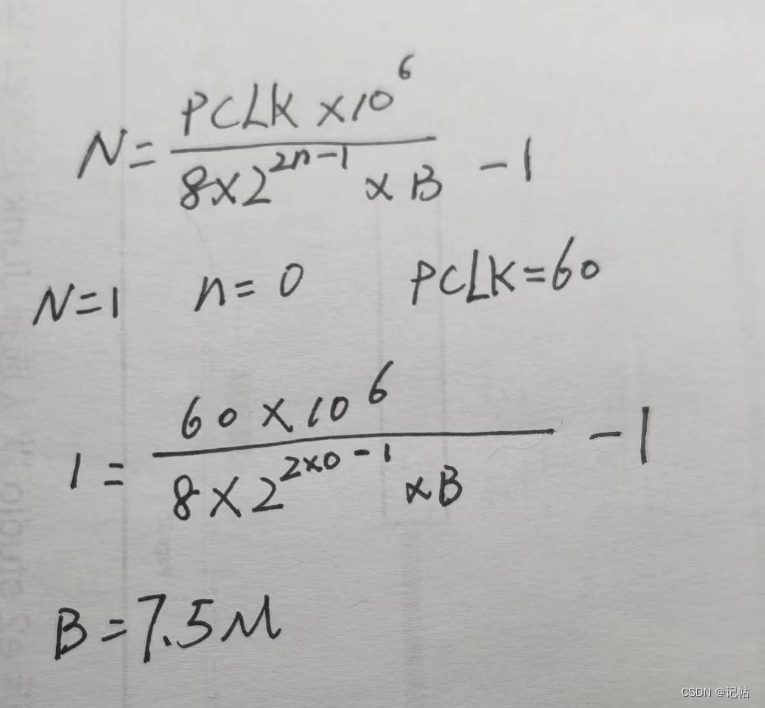

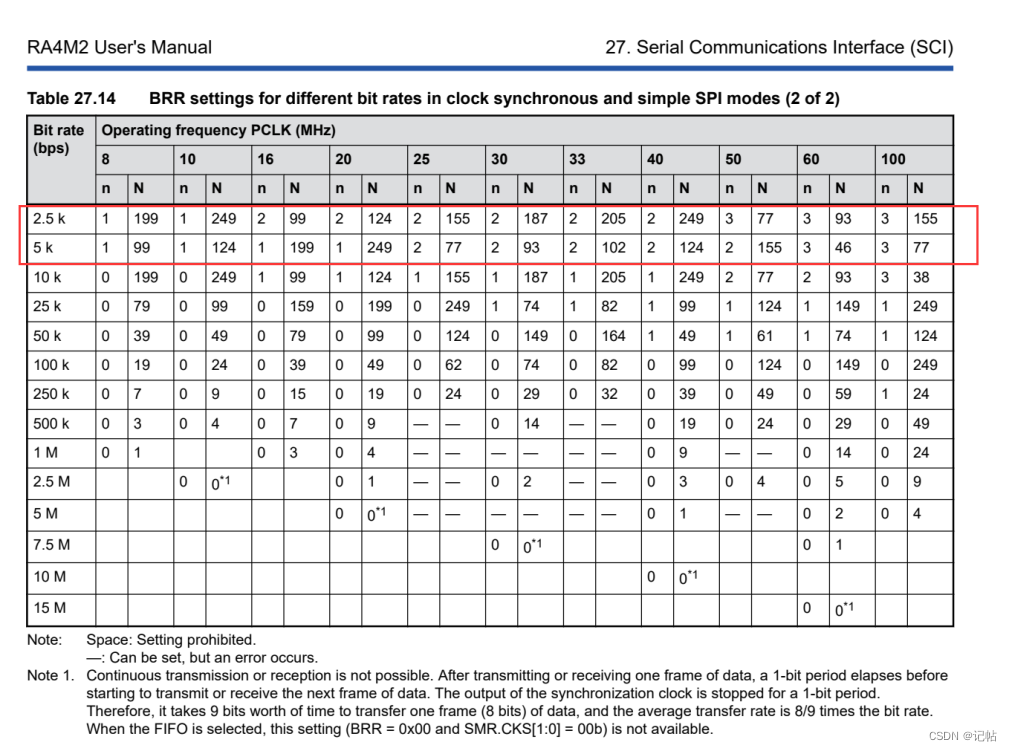

解析RA4M2的BRR值

为了确定适合特定PCLK频率和所需SPI通信速率的BRR值,RA4M2用户手册提供了详尽的表格。这些表格列出了各种PCLK频率与相应的SPI比特率组合,并指出了相应的BRR配置值。

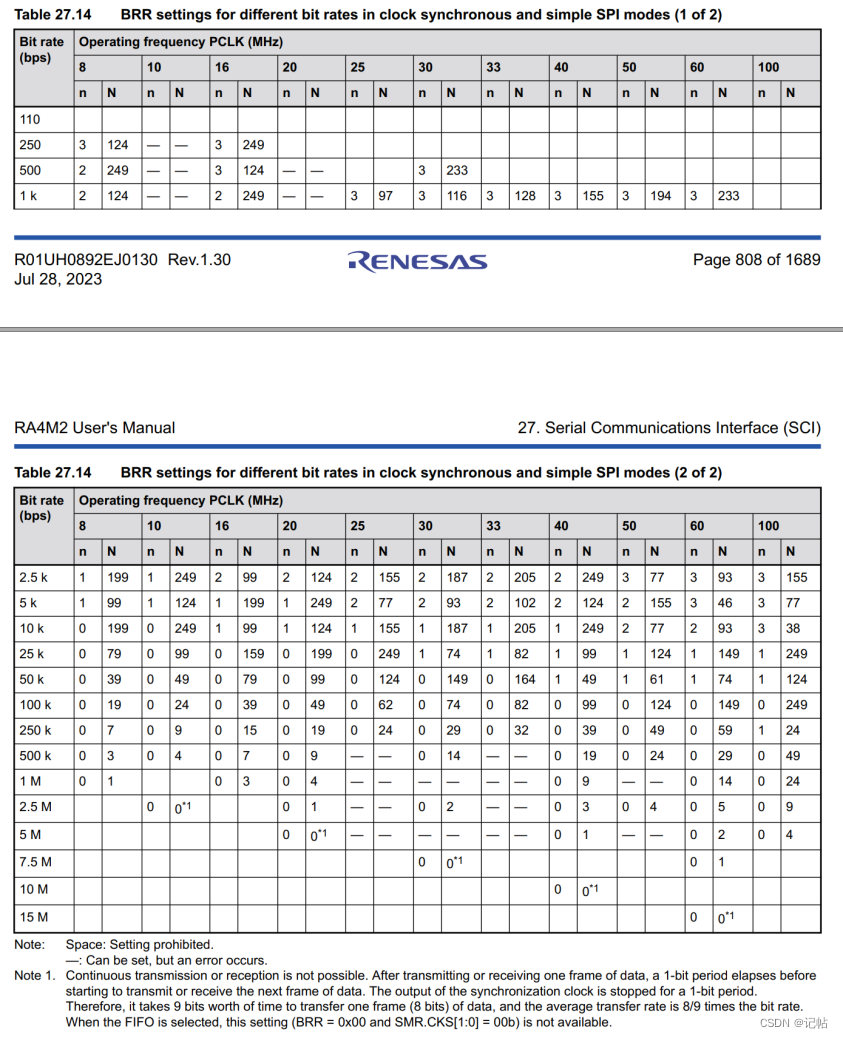

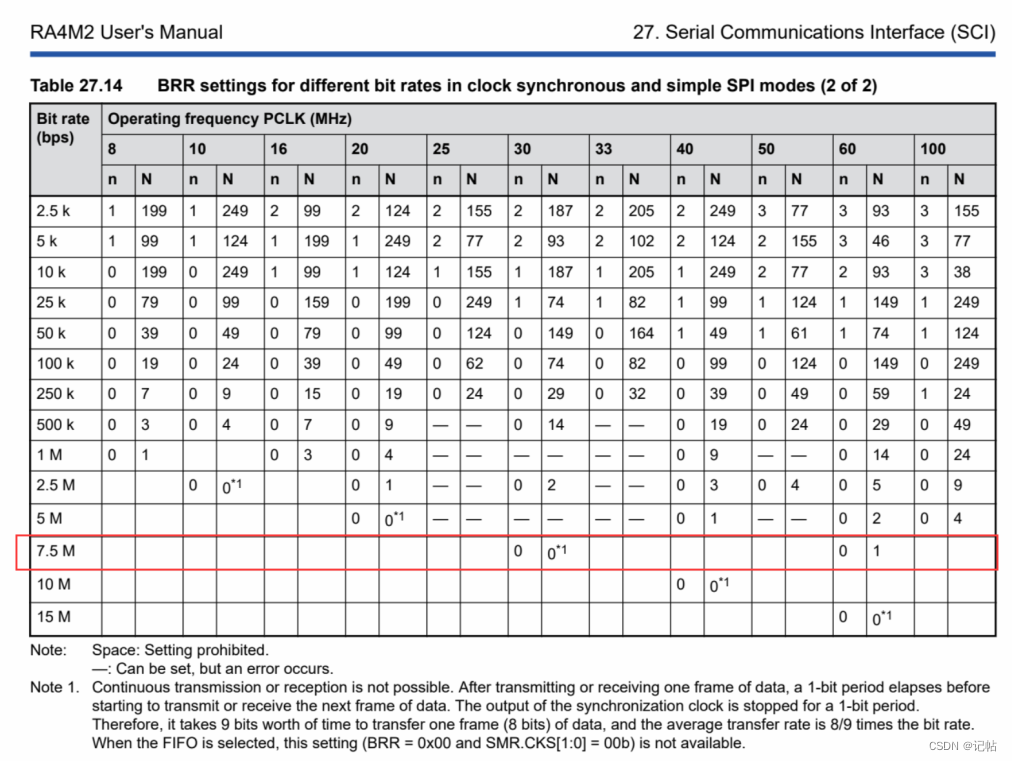

下图显示了瑞萨RA4M2微控制器用户手册的表格27.14,它列出了在时钟同步和简单SPI模式下不同比特率(bps)和操作频率(PCLK)组合的BRR(Bit Rate Register)设置。

每一行代表一个特定的比特率,从110 bps到1 Mbps,而每一列对应一个特定的PCLK值,从8 MHz到100 MHz。在表格中,n 表示PCLK分频值,而 N 是BRR寄存器的设置值。例如,要在25 MHz的PCLK上实现500 bps的比特率,BRR应该设置为249。

这个表格对于那些需要精确控制RA4M2微控制器上SCI通道比特率的开发者来说非常有用,因为它允许他们根据系统的PCLK频率来查找或计算出必须写入BRR寄存器的确切值。

注意的要点包括:

空格(" “)表示该设置是禁止的。

破折号(”—")表示虽然可以设置,但可能会导致错误。

时钟速率

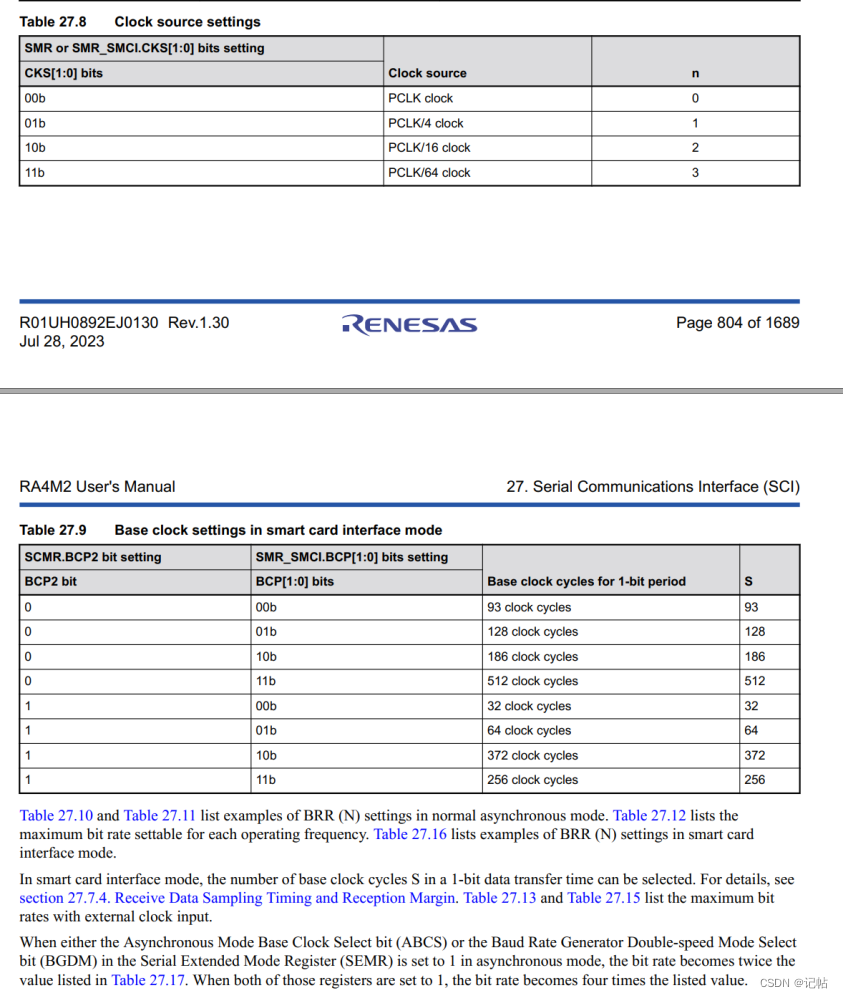

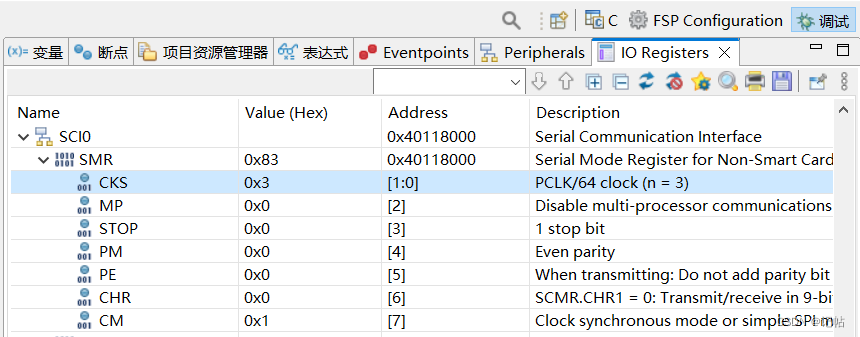

这里,CKS[1:0]的设置决定了SCI的时钟分频率,即PCLK的分频值。表格列出了以下选项:

00b:使用PCLK作为时钟源。

01b:PCLK的四分之一作为时钟源。

10b:PCLK的十六分之一作为时钟源。

11b:PCLK的六十四分之一作为时钟源。

每种设置都有一个对应的分频数n,它在编程时用于确定SCI时钟频率。

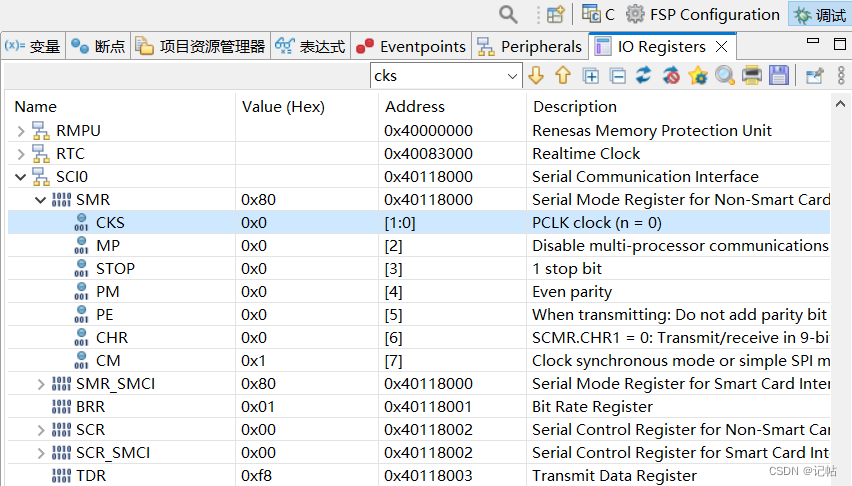

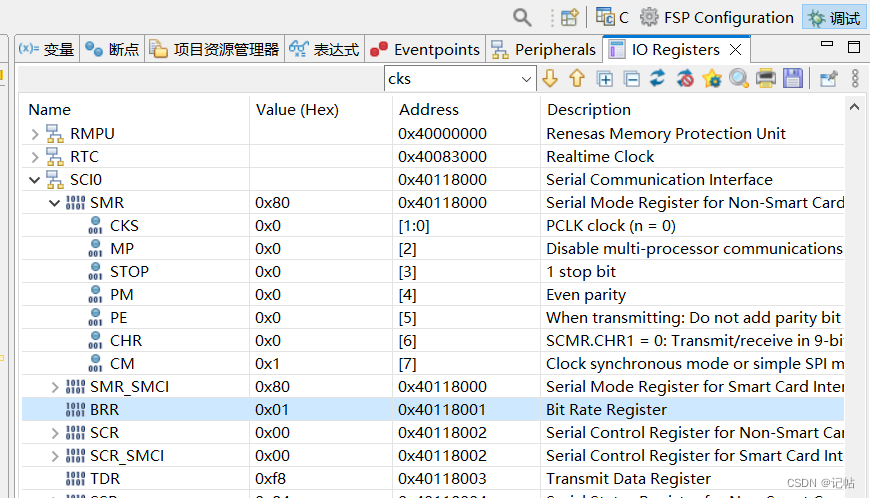

7.5M下寄存器值

PLCKA为60MHz,PCLK=60(MHz)

手册给出对应的参数设置。

查看CKS寄存器可以得知为0,n=0

BRR寄存器为1,即N=1

计算SPI速率为7.5M。

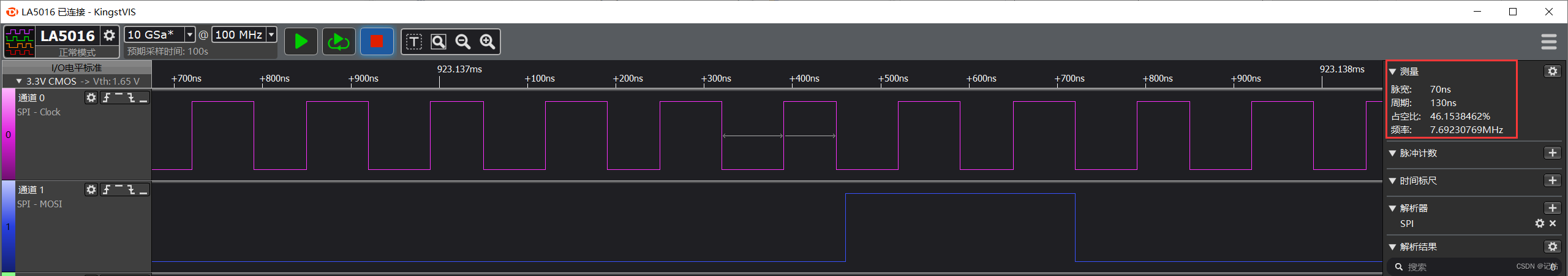

实际测试如下所示。

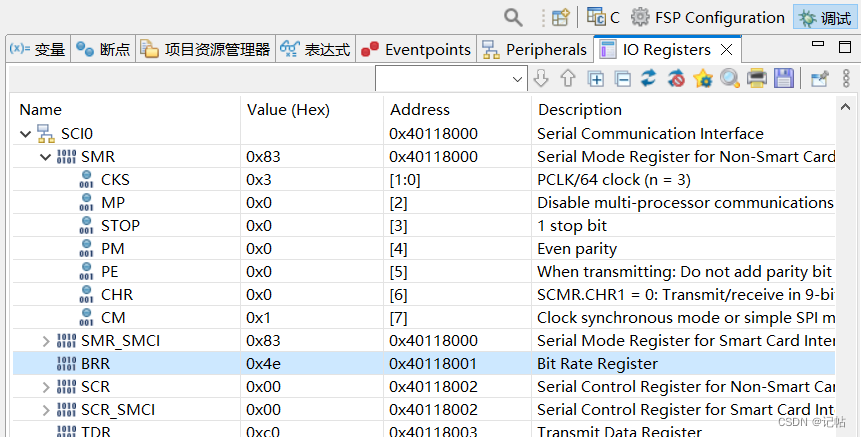

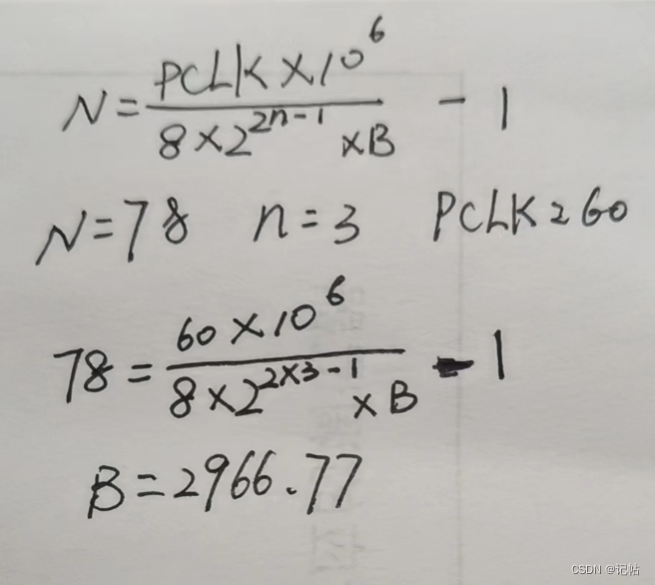

3K下寄存器值

设置速率为3k。

手册未给出对应的参数设置。

PLCKA为60MHz,PCLK=60(MHz)

查看CKS寄存器可以得知为3,n=3

BRR寄存器为0x4e(78),即N=78

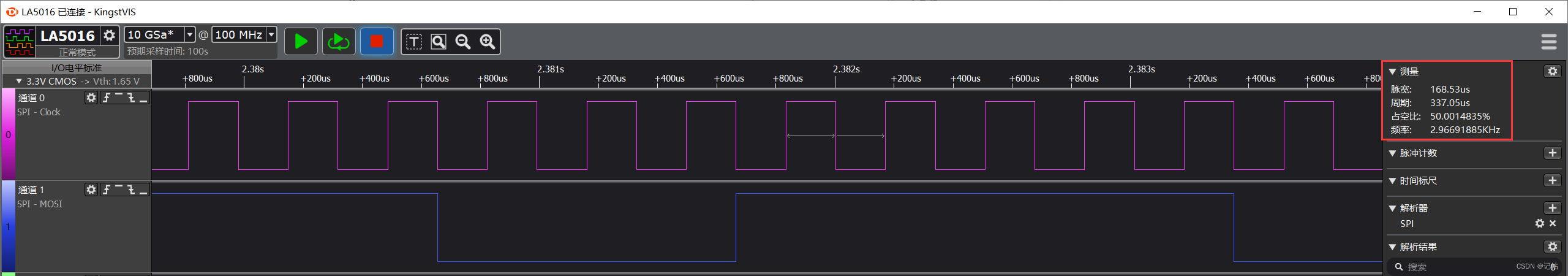

计算SPI实际速率为2966.77。

实际测试如下所示。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!