Verilog 和 System Verilog 的区别

当谈到VLSI设计和数字电路建模时,verilog和system verilog是两种常用的硬件描述语言。这些 HDL 在 VLSI 设计中用于描述电子电路的行为和结构。它们都广泛应用于半导体行业来设计和实现集成电路(IC)。

它们是设计和模拟复杂数字系统的强大工具。在本文中,我们将深入研究这两种 HDL 之间的主要区别,阐明它们在 VLSI 设计领域的特性和功能。

Verilog

Verilog 是一种硬件描述语言,几十年来一直广泛应用于数字设计领域。它提供了一种结构化且简洁的方式来描述数字电路的行为。它是一种用于描述电路的构造和行为的编程语言。 Verilog 于 1983 年开始作为 Gateway Design Automation Inc 的硬件建模专有语言,随后于 1995 年成为 IEEE 标准 1364,并开始普及。 verilog 测试平台基于模块级测试。

system Verilog 简介

另一方面,System verilog 是 verilog 的扩展,它添加了许多功能和增强功能,以促进复杂的数字系统设计。 2005年,系统verilog被指定为verilog的超集,并进行了一些补充,并成为IEEE标准1800,并于2012年升级为IEEE 1800-2012。系统 verilog 构建在动态的类级测试平台上。

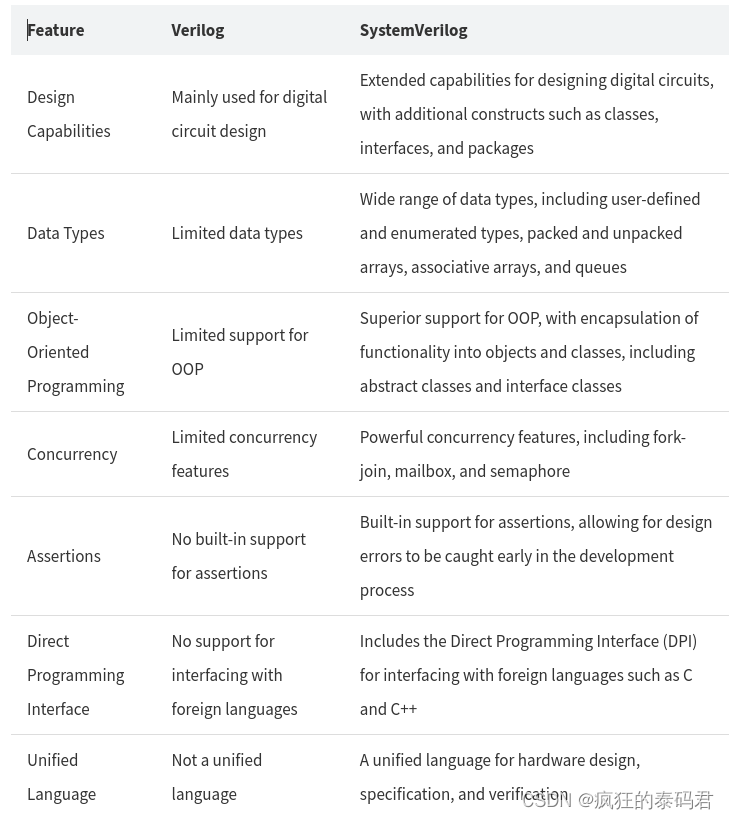

Verilog 和 system Verilog 之间的区别

抽象级别

verilog 和系统 verilog 之间最显着的区别在于它们的抽象级别。 verilog 主要是一种低级语言,专注于详细描述硬件行为。相比之下,系统verilog提供了更高层次的抽象,允许对复杂系统进行更简洁、更高效的建模。

验证能力

System verilog 以其全面的内置验证功能脱颖而出,使其成为验证工程师的首选。 Verilog虽然能够进行验证,但缺乏先进的构造和库。

测试台开发

System Verilog 提供更先进、更高效的测试平台开发功能。它提供了用于创建可重复使用的测试平台组件的构造,并简化了用于验证数字设计功能的激励和检查器的生成。

面向对象编程

System verilog 引入了面向对象的编程概念,例如类和对象,可以实现更好的代码组织和可重用性。 Verilog 缺乏这些高级编程功能。

结论

在不断发展的半导体行业中,熟练掌握硬件描述语言变得越来越重要。总之,这些 HDL 是 VLSI 设计人员的必备工具,学习这些语言是大多数 VLSI 设计工作的先决条件。 VLSI 设计课程通常教授学生如何使用硬件描述语言来设计、仿真和验证电路。这些语言还用于各种其他 VLSI 设计任务,例如综合、静态时序分析和形式验证。

强烈推荐 VLSI 培训和设计课程,为个人提供有关 Verilog 和系统 Verilog 的技能和知识。 Chipedge 是一家著名的 VLSI 培训机构,以其以行业为中心的课程和专家培训师而闻名。作为 VLSI 培训的倡导者,Chipedge 为个人提供在半导体和 VLSI 行业蓬勃发展所需的专业知识。立即加入 Chipedge,在 VLSI 行业中脱颖而出。

设计能力

Verilog主要用于数字电路设计,而SystemVerilog则提供了设计数字电路的扩展功能。 SystemVerilog 提供了额外的构造,例如类、接口和包,来描述复杂的硬件结构。它还通过断言和覆盖模型等结构为验证提供更好的支持。

数据类型

数据类型对于在数字电路中表示和操作数据的硬件设计至关重要。 SystemVerilog 提供更广泛的数据类型,包括用户定义和枚举类型、打包和解包数组、关联数组和队列。这些灵活的数据结构允许更有序、更高效地表示复杂的硬件结构。

面向对象编程

与 Verilog 相比,SystemVerilog 对面向对象编程 (OOP) 具有出色的支持,使代码更有条理且更易于阅读。使用SystemVerilog,设计人员可以将功能封装到对象和类中,包括抽象类和接口类。通过利用 SystemVerilog 中的 OOP,设计人员可以创建更加模块化和可重用的代码,从而有助于加快硬件设计过程。

并发性

SystemVerilog 强大的并发功能(包括 fork-join、邮箱和信号量)可实现硬件并行性或利用多个 CPU 内核的软件算法。 Fork-join 允许在顺序块内并行执行线程。邮箱支持并发进程或线程之间的通信,而信号量则同步对共享资源的访问。这些功能使 SystemVerilog 成为具有复杂并发系统的高级硬件设计项目的首选。

断言

SystemVerilog 提供了对断言的内置支持,而 Verilog 则没有。断言是检查设计中某些条件的语句,有助于在开发过程的早期发现设计错误。这是验证的一个重要特征。

直接编程接口

SystemVerilog 包括直接编程接口 (DPI),允许设计人员与 C 和 C++ 等外语进行交互。这是与设计流程中的其他工具交互并使设计过程更加高效的重要功能。

统一语言

SystemVerilog 是一种统一的硬件设计、规范和验证语言,包含 Verilog 的所有功能以及用于设计和验证的附加功能。这使得设计人员和验证工程师可以更轻松地在从设计到验证的整个设计流程中使用单一语言。

结论

虽然 Verilog 可能仍可用于较简单的数字电路,但 SystemVerilog 是设计和验证具有高级功能的数字电路的首选。通过了解两种语言之间的差异,设计人员可以就在设计或验证项目中使用哪种语言做出明智的决定。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!