【Verilog】运算符

系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter)

算术运算符

Verilog HDL中常用的算术运算符主要有五种,分别是加法(+)、减法(-)、乘法(*)、除法(/)和取模(%)。

算术操作结果的位宽。?算术表达式结果的长度由最长的操作数决定。?在赋值语句下,算术操作结果的长度由操作左端的目标长度决定。

关系运算符

关系运算符也是双目运算符,是对两个操作数的大小进行比较。关系运算符有大于(>)、小于(<)、大于等于(>=)和小于等于(<=)几种。

在进行关系比较时,如果成立则结果为“1”,否则返回的结果为“0”;若不确定则返回结果为不定值(x)。例如:10>15的结果为假(0),20>18的结果为真(1),而4’b1101<4’hx的结果为不定值(x)。

相等关系运算符

相等关系运算符是对两个操作数进行比较,比较的结果有三种:真(1)、假(0)和不定值(x)。Verilog HDL语言中有四种相等关系运算符:等于( == )、不等于( != )、全等(===)、非全等(! ==)。

“==”和“!=”称为逻辑等式运算符,其结果由两个操作数的值决定。

“ === ”和“ !== ”运算符则不同,它是对操作数进行按位比较,两个操作数必须完全一致,其结果才是1,否则为0。但是,若两个操作数对应位出现不定值x和高阻值z,则可认为是相同的。“ ===”和“!==”运算符常用于case表达式的判别,所以又称为“case等式运算符”。

逻辑运算符

逻辑运算符有三种,分别是逻辑与运算符(&&)、逻辑或运算符(||)、逻辑非运算符(!)。其中逻辑与和逻辑或是双目运算符,逻辑非为单目运算符。

逻辑运算符的操作数只能是逻辑0或者逻辑1。

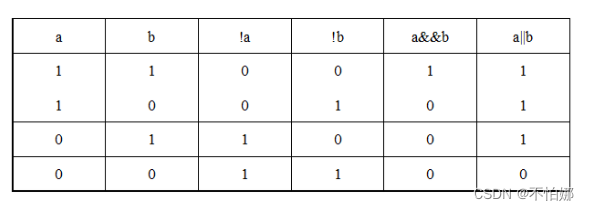

三种逻辑运算符的真值表如下所示:

在逻辑运算符的操作过程中,如果操作数是1位的,那么1就代表逻辑真,0就代表逻辑假;如果操作数是由多位组成的,则当操作数每一位都是0时才是逻辑0值,只要有某一位为1,这个操作数就是逻辑1值。例如:寄存器变量a、b的初值分别为4’b1110和4’b0000,则?!a=0,!b=1,a&&b=0;a||b=1。

需注意的是,若操作数中存在不定态x,则逻辑运算的结果也是不定态,例如:a的初值为4’b1100,b的初值为4’b01x0,则?!a=0,!b=x,a&&b=x,a||b=x。

按位运算符

数字逻辑电路中,信号与信号之间的运算称为位运算。Verilog HDL提供了以下五种类型的位运算符:按位取反(**)、按位与(&)、按位或(**|**)、按位异或(**^**)、按位同或(**^)。

按位运算举例:

module bit_tb;

reg[2:0]a;

reg[4:0]b;

initial

begin

a=5'b101;//运算的时候a自动变为5'b00101

b=5'b11101;

$display("%b",~a);//结果为3'b010

$display("%b",~b);//结果为5'b00010

$display("%b",a&b); //结果为5'b00101

$display("%b",a|b); //结果为5'b11101

$display("%b",a^b); //结果为5'b11000

end

endmodule

归约运算符

归约运算符按位进行逻辑运算,属于单目运算符。由于这一类运算符操作的结果是产生1位逻辑值,因而被形象地称为缩位运算符。

Verilog HDL中,缩位运算符包括&(与)、| (或)、^ (异或)以及相应的非操作&、|、^、^。归约运算符的操作数只有一个。

归约运算符的运算过程是:设a是一个4位的寄存器型变量,它的四位分别是a[0]、a[1]、a[2]和a[3]。当对a进行缩位运算时,先对a[0]和a[1]进行缩位运算,产生1位的结果,再将这个结果与a[2]进行缩位运算,再接着是a[3],最后产生1位的操作结果。

归约操作举例:

module cut_tb;

reg[5:0]a;

initial

begin

a=6'b101011;

$display("%b",&a); //结果为1'b0

$display("%b",|a); //结果为1'b1

$display("%b",^a); //结果为1'b0

end

endmodule

移位运算符

移位运算符有两种:左移位运算符(<<)、右移位运算符(>>)。运算过程是将左边(右边)的操作数向左(右)移,所移动的位数由右边的操作数来决定,然后用0来填补移出的空位。

条件运算符

条件运算符是Verilog HDL里唯一的三目运算符,它根据条件表达式的值来选择执行表达式,其表达形式为:<条件表达式>?<表达式1>:<表达式2>。其中,条件表达式的计算结果有真(1)、假(0)和不定态(x)三种。当条件表达式的结果为真时,执行表达式1,当条件表达式的结果为假时,执行表达式2。

连接和复制运算符

Verilog HDL语言中还有两个特殊的运算符:连接运算符({})和复制运算符({{}})。

连接运算符是把位于大括号({})中的两个或两个以上信号或数值用逗号(,)分隔的小表达式按位连接在一起,最后用大括号括起来表示一个整体信号,形成一个大的表达式。其格式为:{信号1的某几位,信号2的某几位,…,信号n的某几位}。

重复运算符({{}}) 将一个表达式放入双重花括号中,复制因子放在第一层括号中。它为复制一个常量或变量提供了一种简便方法。

连接和复制操作举例:

module con_rep_tb;

reg [2:0]a;

reg [3:0]b;

reg [7:0]c;

reg [4:0]d;

reg [5:0]e;

initial

begin

a=3'b101;

b=5'b1110;

c={a,b};

d={a[2:1],b[2:0]};

e={2{a}};

$display("%b",c); //结果为8'b01011110

$display("%b",d); //结果为5'b10110

$display("%b",e); //结果为6'b101101

end

endmodule

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 正则表达式第三四个作用:替换、切割

- 带大家做一个,易上手的家常葱油挂面

- day05_java中的流程控制

- windbg调试中文帮助文档

- 深入浅出RabbitMQ:顺序消费、死信队列和延时队列

- git提交代码报错Git: husky > pre-commit

- 基于Java SSM框架实现校园网络维修系统项目【项目源码】

- 黑马头条--day11-kafkaStream热点文章实时计算

- 万界星空科技MES系统的生产管理流程

- 电子学会2023年12月青少年软件编程(图形化)等级考试试卷(四级)真题,含答案解析