【ARM学习】Cortex- A系列程序员学习指南

Perface ARM简介

ARM处理器无处不在。

移动电话、个人计算机、电视或汽车。在大约30亿元的微处理器总出货量中,x86架构占据一个非常小的位置(但仍然非常有利可图的)。

ARM历史

ARM处理器不是一个单一的处理器,而是一个拥有相同指令集和程序员模型的同一处理器家族,并有一定程度的向后兼容性。

第一个ARM的处理器(ARM1)是由Acorn电脑有限公司中Sophie Wilson和Steve Furber领导的小组设计完成的,并在1985年4月生产了第一款硅片。

ARM1迅速被ARM2取代(其中新增乘法硬件), ARM2被用于实际系统中,包括Acorn的阿基米德个人计算机。

1990年11月,ARM成立于英国剑桥,作为高级RISC机器有限公司,它是苹果电脑、Acorn电脑和VLSI科技公司的合资企业,最初的12名员工主要来自Acorn电脑的团队。

ARM成为一个独立的公司的原因之一是处理器已经被苹果电脑用在了牛顿产品中。

新公司迅速决定,他们技术前进的最好方式是注册他们的知识产权(IP),而不是他们自己设计、制造和销售芯片,他们将出售设计权给半导体公司。

出名的战略,背后有很多有意思的故事。

ARM也注册了物理IP——单元库(NAND门、RAM等)、图形和视频加速器以及软件开发产品,如编译器、调试器和开发板。

片上系统(SoC)

由一个单独的公司来生产这种系统的所有部件是越来越罕见的。出于这一点,ARM以及其他半导体IP公司设计和验证组件(所谓的IP模块或处理器)。

半导体公司允许在他们自己的设计使用这些模块,如微处理器、DSP、3D图形和视频控制器及许多其他功能。

半导体公司将这些模块和特定系统的其他部分集成到芯片上,形成一个系统级芯片(SoC)。为了形成系统,这些设备的构造者必须选择适当的处理器、内存控制器、片上存储器、外设、互连总线和其他逻辑块(可能包括模拟或射频部分)。

ASIC(Application Specific Integrated Circuit)这个术语,这是一种为特定应用而设计的集成电路。一个单独的ASIC可能包含一个ARM处理器、内存和其他组件。

这跟那些被称为系统级芯片的设备显然有很多相似的地方。SoC通常是指一种具有高集成度的设备,即在单一的设备上包括系统的很多部分,可能包括模拟、混合信号或射频电路。

当然,像Linux这样强大的操作系统需要大量的内存空间,不仅仅是在单一的硅器件上运行。由于单个设备不能包含整个系统,因此,片上系统的命名未必完全准确。

抛开硅片面积的问题不谈,在通常的情况下,一个系统的许多部分需要专业的硅制造工艺并避免它们被放置到相同的晶片上。

在一定程度上,SoC概念的扩展就是封装内系统(SiP),在一个单一的物理封装内结合了许多单独的芯片,也被广泛认为封装堆叠。

SoC芯片采用的封装用于底部(用于连接到PCB)到顶部(包含连接到独立的软件包,可能包含一个闪速存储器或一个大的SDRAM器件)的连接。

嵌入式系统

嵌入式系统的常规定义是在一块计算机硬件上运行软件以执行特定的任务。例如,电视机顶盒、智能卡、路由器、磁盘驱动器、打印机、汽车发动机管理系统、MP3或复印机。

与计算机系统相比,不同之处在于计算机上具有各种各样的通用软件,以及输入和输出的设备,如键盘和某种类型的图形化显示器。

现在,这种区分变得越来越模糊,如移动电话,一个基本电话原型可能只能执行拨打电话的任务,但现代智能手机还可以运行一个复杂的操作系统,甚至可下载成千上万的应用程序。

嵌入式系统可能包含简单的8位微处理器,如Intel 8051或PIC微控制器,或者包含一些复杂的32位或64位处理器,如ARM系列。

系统需要一些RAM和某种形式的非易失性存储空间来保存系统执行的程序,需要一些额外的外围设备,对于这些设备的实际功能(通常包括通用异步收发器(UART)、中断控制器、定时器、GPIO控制器)也可能是相当复杂的模块,如DSP、GPU(图形处理器)或DMA控制器。

在嵌入式系统上运行的软件通常分为两个独立的部分:操作系统(OS)和在OS上运行的应用程序。

大量投入使用的操作系统,从简单的内核、复杂的实时操作系统(RTOS),到全功能的、存在于电脑上的复杂操作系统。

由于嵌入式系统上很多限制存在,与通用PC的编程相比,嵌入式系统的编程可能会面临更多的挑战。

- (1)内存占用。在许多系统中,为了最大限度地降低成本,内存的大小是被限制的。程序员可能会被迫考虑程序的规模,以及在程序运行时如何减少对内存的使用。

- (2)实时性。某些系统的特点是对外部事件的响应有一定的时间限制。这可能是“硬性”的要求(如汽车制动系统必须在一定时间内响应)或“软性”的要求(如音频处理必须某个时间帧下完成,以避免糟糕的用户体验,不能满足则可能导致这个系统不值钱)。

- (3)功率。许多嵌入式系统中的电源都是电池,程序员和硬件设计师必须最大限度地减少对系统的能源使用。这是可以做到的,例如通过减慢时钟、减少供应电压或在没有工作的时候关闭处理器。

- (4)成本。成本可能是一个系统设计的最大约束点。

- (5)上市时间。在竞争激烈的市场中,开发一个产品所用的时间是影响该产品的成功的一个重要因素。

ARM体系结构和处理器

RM本身并不生产硅器件。相反地,ARM创建微处理器设计,并授权给半导体公司和原始设备制造商(OEM),由原始设备制造商把微处理器集成到片上系统设备上。

为确保实施上的兼容,ARM定义的体系结构规范中明确了合格产品的行为。ARM体系结构中处理器的实现符合一个特定版本的体系结构,不同的处理器可能会有不同的内部实现和微架构,但不同的周期时间和时钟速度都符合同一版本的体系结构。

- (1)体系结构。

定义了常见的一组或一系列的处理器设计行为,也在ARM体系结构参考手册(ARM ARM)中定义,包括指令集、寄存器、异常处理和其他编程模块功能。该体系结构定义的是程序员可见的行为,例如,哪个寄存器可用以及单独的汇编语言指令能完成的功能。

- (2)微体系结构。

定义了体系结构的可见行为是如何执行的,如流水线级数;还会有一些程序员可见的效果**,如执行特定的指令要多久、停顿周期后的结果。**

- (3)处理器。

一个处理器是一个微体系结构的具体实现,一个处理器可能会被授权给多个公司制造生产,因此**,它可能已被集成到各种各样的设备和系统上,同时也有与之相应的存储器映射、外围设备和其他执行特定功能的模块**。处理器都在技术参考手册中介绍,这些手册可在ARM网站上找到。

- (4)核心。

我们使用这个词来描述一个多核处理器的一个单独的逻辑执行单元。

- (5)SoC。

一个片上系统包含一个或多个处理器,同时也包含存储器和外设,该设备可能包含一个或多个额外的处理器、存储器和外设系统的一部分。针对这些系统,一般都由独立SoC或平台的供应商的文档提供详细介绍。

体系结构的版本

ARM会定期发布体系结构新的版本,在现有功能的基础上新增新的功能或更新。这种更新通常是向后兼容的,这意味着运行在旧版本的用户编码在新版本上仍可以正确运行。

当然,利用新功能编写的代码就不一定能在旧的处理器上运行了,因为旧处理器通常缺少这个功能模块。

在所有版本的体系结构中,一些系统特性和行为留给具体实现来定义。例如,体系结构不定义高速缓存的大小、指令周期的时序,这是由具体实现的处理器和SoC决定的。

**每个体系结构的版本都定义了可选的扩展。**在处理器的具体实现中,这些扩展可能并没有被实现。例如,在ARMv7的体系结构中,高级SIMD(NEON)技术就是一个可选扩展。

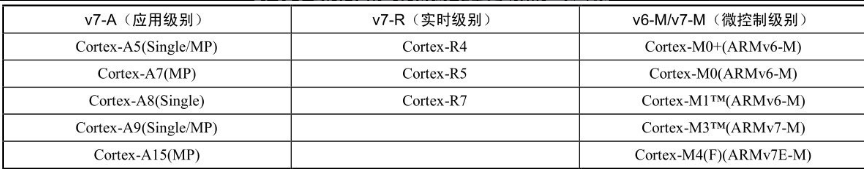

**ARMv7体系结构还具有配置属性的概念。针对处理器的不同市场和用途,产生了这些体系结构的变种。**简介如下。

- (1)A:应用程序配置系列,定义了一种针对高性能处理器的体系结构,它支持使用内存管理单元(MMU)的虚拟内存系统,能够运行复杂的操作系统,同时支持ARM和Thumb指令集。

- (2)R:实时配置系列,定义了一种系统的实时结构,这种结构需要确定的时序和较低的中断响应延迟,不需要对虚拟内存系统和MMU的支持,而是使用一个简单的内存保护单元(MPU)。

- (3)M:微控制器的配置系列,定义了一种低成本和低性能系统的体系结构,其中低延迟的中断处理是非常重要的。相比其他配置系列,它使用了一个不同的异常处理模型,并只支持一种Thumb指令集的变体。

这里就不展开了,因为基本上都是基于V8了。

体系结构的历史与扩展

从20世纪80年代中期的第一款测试硅片到20世纪90年代初的第一个ARM6和ARM7设备,ARM体系结构的变化相对较小。

-

在第1版本的体系结构中,ARM1实现了大部分异常模式的加载、存储和算术运算,以及寄存器组。

-

第2版本增加了乘法和乘法累加指令,以及对协处理器的支持,再加上一些进一步的创新。这些早期的处理器只支持26位的地址空间。

-

第3版本的体系结构分离了程序指针寄存器和程序状态寄存器,并增加了一些新的模式来支持32位的地址空间。

-

第4版本增加了对半字的加载和存储操作以及一个额外的内核级特权模式。

-

ARMv4T体系结构推出的Thumb(16位)指令集已经在ARM7TDMI?和ARM9TDMI?的处理器上应用,并已出货数十亿美元的产品。

-

ARMv5TE体系结构添加改进了DSP类型操作和饱和算术和ARM/Thumb互相配合。

-

ARMv6的提出了一些增强功能,如支持未对齐的内存访问,对存储器结构的重要改变和对多处理器的支持,再加上对32位寄存器内字节或半字的SIMD操作的支持,它还提供了许多可选的扩展,主要是Thumb-2和安全扩展(TrustZone)。Thumb-2将Thumb扩展到混合长度(16位和32位)的指令集。

-

ARMv7-A体系结构对Thumb-2进行强制性扩展,并增加了高级SIMD扩展(NEON)。

-

数年以来,ARM在ARM9中采用了连续编号处理器系统,

-

ARM9是从ARM8发展来的,ARM8又是继ARM7而来的。

在整个ARM家族中,用附加的各种数字和字母来表示不同的变种。例如,ARM7TDMI处理器用T来表示Thumb,用D表示Debug, M表示快速乘法器,I表示嵌入式ICE。

对于ARMv7体系结构,ARM公司采用商标Cortex,并补充表明处理器支持哪种配置系列(A、R还是M)。

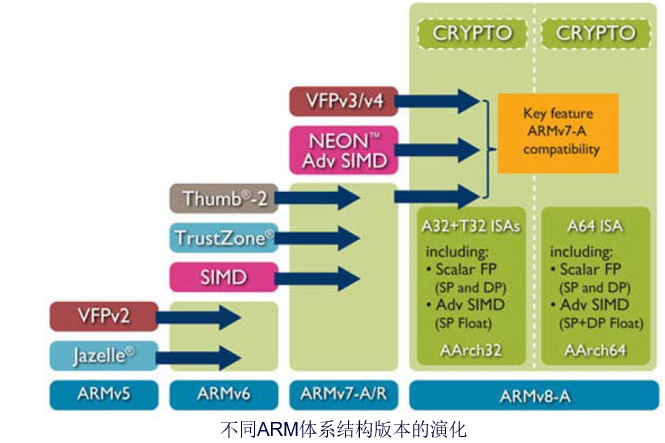

图显示了不同版本的体系结构如何对应于不同的处理器实现。

注意,这个图不全面,也不包括所有体系结构的版本或处理器实现。

整几张图给大家看看:原创见水印

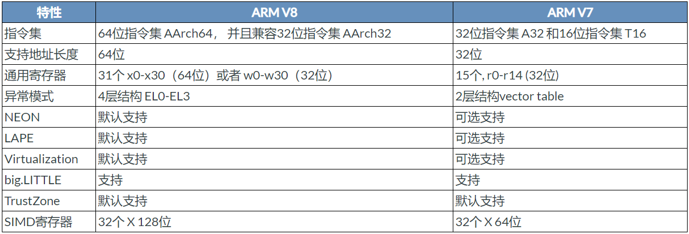

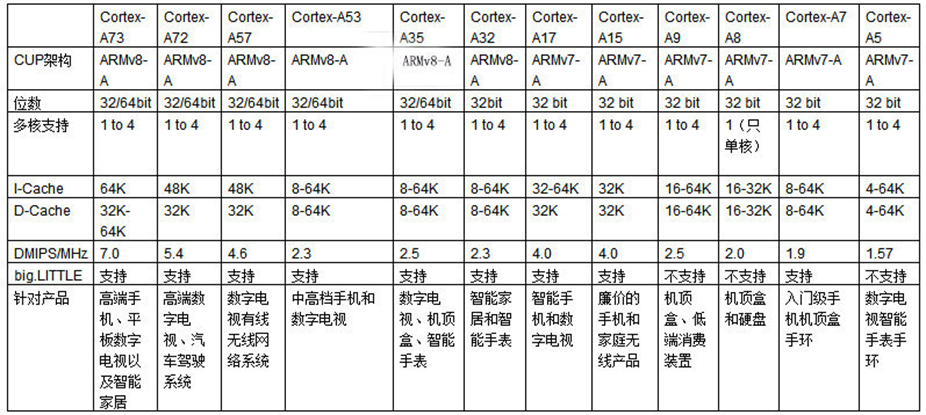

ARM V7与V8的比较:

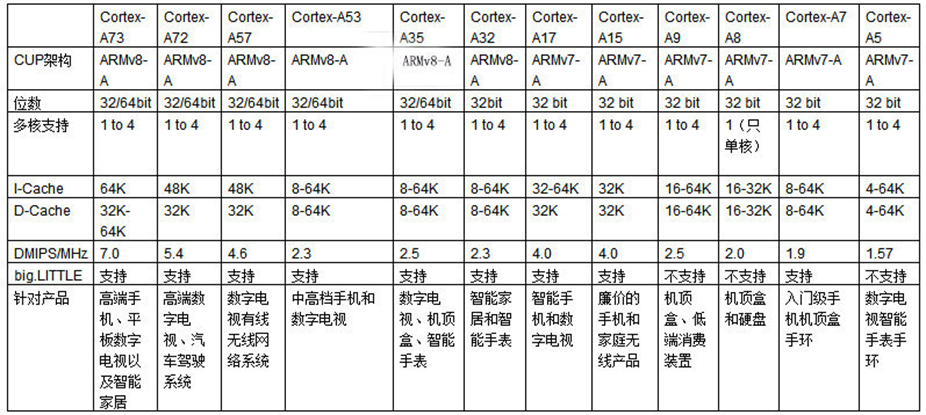

ARM V7与V8的CPU核:

以上这些东西再ARM官网都能找到相应的图,到这里咱们有个感性的认识即可。

最后在这里,我们将简要地介绍了一些基本结构单元。

一些基本结构单元

1.DSP乘累加和饱和算术指令

加入到ARMv5TE体系结构中的这些指令,改善了数字信号处理和多媒体软件的能力,并由字母E来表示。

这些新的指令提供了许多不同种类的带符号乘累加、饱和加减、前导零计数,并且在更高版本的体系结构上保留下来。在许多情况下,这使得可以在系统中省掉一个简单的独立DSP。

2.Jazelle

当需要节省电量时,Jazelle DBX(直接字节码执行)被ARMv5TEJ用来改善执行Java代码的性能,增加内存的可用性和即时(JIT)编译器的改进,降低处理器的应用价值。因此,许多的ARMv7-A处理器不需要硬件加速。

在非常有限的内存中提供给系统高性能的Java性能时,Jazelle DBX是最适合的,例如,功能型手机或低成本的嵌入式应用。在当今的系统中,它主要是用于向后兼容。

3.Thumb执行环境(ThumbEE)

由于ARMv7-A的引进和要求,ThumbEE有时也被称为Jazelle-RCT(运行时编译目标)。它涉及对Thumb指令集微小改变,使它能更好地在受控环境中运行而生成代码(如管理语言中的Java、Dalvik、C#、Python或Perl)。

ThumbEE被用在实时(JIT)或提前(AOT)编译器中,它可以减少重新编译的代码大小。管理代码的编译不属于本书的讨论范围。

4.Thumb-2

在ARMv6T2中引进Thumb-2技术,此技术也是ARMv7所需。该技术将原来的16位Thumb指令集扩展到32位指令集。

16位和32位Thumb指令集的组合实现了原始Thumb指令集的相似代码密度,但性能类似于32位ARM指令集。由此产生的Thumb指令集提供了几乎所有的ARM指令集的功能,以及额外的功能。

5.安全扩展(TrustZone)

ARMv6K引入的可选安全扩展TrustZone已经在所有ARM Cortex-A处理器中实现。TrustZone提供了一个独立的安全区域,可以将敏感代码和数据从包含操作系统和应用程序的普通区域分离出来。

因此,安全区域中的软件旨在为普通(非安全区域)提供安全服务。

6.VFP

在ARMv7之前,VFP的扩展被称为矢量浮点结构,并用于矢量运算。VFP是一种实现单精度和可选双精度浮点运算的扩展,符合ANSI/IEEE标准的浮点运算。

7.高级SIMD(NEON)

ARM NEON技术使得高级单指令多数据(SIMD)指令集拥有独立的寄存器表(与VFP共享),一些具体实现有单独的NEON流水线后端,支持8位、16位、32位和64位整数,以及单精度(32位)浮点数据,并可以在64位和128位的寄存器上进行运算。

8.大物理地址扩展(LPAE)

LPAE是v7-A体系结构的可选部分,并且在Cortex-A7和Cortex-A15处理器上实现,它允许32位处理器由原来通常最大的4 GB访问空间扩展到1 TB的访问空间,这1 TB是通过把32位虚拟内存地址转换成40位物理内存地址得来的。

9.虚拟化

ARM处理器的虚拟化扩展也是ARMv7-A体系结构文件的可选扩展,此扩展可支持通过虚拟机监视器(称为虚拟机超级管理员)从一个操作系统切换到另一个。

当在一个单处理器和多处理器系统中执行时,虚拟化扩展可支持在一个处理器上运行多个虚拟机。

10.big.LITTLE大小模式

big.LITTLE大小模式处理被引入到ARMv7体系结构中,可解决行业当前的的挑战,即如何创建既有高性能又有极佳节能效果的片上系统(SoC)以延长电池使用寿命。

big.LITTLE采用了高性能的Cortex-A15处理器,再加上一个高效节能的Cortex-A7处理器,Cortex-A15处理器可被用于繁重的工作量,Cortex-A7处理器可以承担移动设备的大部分工作。

ARM Cortex-A系列处理器架构关键点

许多关键点对于Cortex-A系列器件都是相同的。

- ● 32位RISC处理器,具有16×32位的寄存器和以模式为基础的寄存器集合;

- ● 改进型哈佛体系结构(独立的、指令和数据的并发访问);

- ● load/store(加载/存储)体系结构;

- ● 以Thumb-2技术为标准;

- ● VFP和NEON的选项,有望成为通用目的应用处理器的标准功能;

- ● 对来自于以前ARM处理器的代码向后兼容;

- ● 4GB的虚拟地址空间和最小4 GB的物理地址空间;

- ● 虚拟地址转换到物理地址的硬件转换表;

- ● 虚拟页面大小为4KB、64KB、1MB和16MB,可缓存属性和存取权限可以在每个页面上进行单独设置;

- ● 大端和小端字节数据访问支持;

- ● 基本加载/存储指令的未对齐访问支持;

- ● 对称多处理器SMP支持MPCore?变种,具有L1级别高速缓存的完整数据;

- ● 自动缓存和转换后备缓冲器(TLB)维护传播提供高效率的SMP操作;

- ● 物理索引,物理标记(PIPT)的数据高速缓存。

处理器和路径

Cortex-A系列处理器

Cortex- A5处理器

Cortex-A5处理器支持ARMv7-A所有的架构功能,包括TrustZone安全扩展和NEON媒体处理引擎。

它的面积和功耗效率是极高的,但比其他Cortex-A系列处理器的最高性能都低。Cortex-A5处理器有单核和多核版本。

如图所示的Cortex-A5处理器在某些情况下可以同时执行一个非分支跳转指令和紧接着的分支跳转指令,并且包含一个复杂的分支预测逻辑,以避免因分支跳转导致流水线被冲刷并重新填充。

NEON和浮点硬件的支持是可选的。Cortex-A5处理器还支持ARM和Thumb指令集以及Jazelle DBX和Jazelle-RCT技术。

Cortex-A7处理器

Cortex-A7多核处理器是一个高性能,低功耗的处理器,与其他在本书提到的Cortex-A系列处理器完全兼容。单核Cortex-A7处理器框图如图所示。

Cortex-A7处理器包含高性能的Cortex-A15处理器的所有功能,包括虚拟化、大的物理地址的扩展(LPAE)、NENO和AMBA4 ACE的一致性。Cortex-A7 MPCore处理器具有以下特点:

- ● 改进内存管理和总线接口;

- ● LPAE,可寻址高达1 TB的内存;

- ● 通过AMBA4技术解决多核处理器集的一致性问题;

- ● AMBA4缓存一致性互连技术(CCI)保证在多个Cortex-A7 MPCore处理器之间实现所有的缓存一致性。

Cortex-A8处理器

Cortex-A8处理器是第一个实现ARMv7-A体系结构的处理器。许多不同的处理器都使用它,包括三星S5PC100,德州仪器的OMAP3530和飞思卡尔的i.MX515,拥有很广泛的应用,有些能超过1 GHz的主频。

与以前的ARM处理器相比,Cortex-A8处理器有更复杂的微体系结构。

图是单核Cortex-A8处理器框图,展示了Cortex-A8处理器的内部结构,包括路径。

独立的指令和数据的一级高速缓存的大小为16KB或32KB,是对集成的统一二级高速缓存的一种补充,二级高速缓存可高达1MB的大小。一级和二级高速缓存都可为处理器提供128位宽的数据接口。

一级数据缓存虚拟索引,但物理标记,而二级高速缓存的索引和标记都使用物理地址。在默认情况下,NEON使用的数据是不通过L1来缓存的(虽然NEON可以读写L1数据高速缓存中的数据)。

Cortex-A9处理器

Cortex-A9 MPCore处理器和Cortex-A9单核处理器提供比Cortex-A5和Cortex-A8处理器更高的性能,支持ARM、Thumb、Thumb-2、TrustZone、Jazelle RCT和DBX等技术单核Cortex-A9处理器框图如图所示。

一级高速缓存系统在硬件上支持1~4个处理器的多核软件的高速缓存一致性。ARM提供外部的二级高速缓存控制器(L2C-310,以前称为PL310),支持高达8MB的高速缓存大小。

该处理器还包含一个集成的中断控制器,ARM通用中断控制器(GIC)结构规范的实现,这可以被配置为对多达224个中断源的支持。集成Cortex-A9处理器的设备,有nVidia的双核Tegra-2、ST的SPEAr1300和TI的OMAP4平台。

Cortex-A15处理器

Cortex-A15 MPCore处理器是目前ARM处理器中性能最高的(在本书即将完成时,ARM已推出了更新的Cortex-A57),并且与本书中描述的其他ARM处理器的应用程序是兼容的。

Cortex-A15 MPCore处理器推出了一些新功能,包括支持完整的硬件虚拟化和大物理地址扩展(LPAE),这就可以寻址高达1 TB的内存,其框图如图所示。

Cortex-A15 MPCore处理器具有以下特点:

- ● 无序的超标量流水线;

- ● 紧密耦合的低延迟的二级高速缓存(高达4MB的大小);

- ● 改进的浮点和NEON媒体性能;

- ● 全硬件虚拟化;

- ● 寻址高达1 TB内存的大物理地址扩展(LPAE);

- ● 容错性的纠错能力和软件故障恢复;

- ● 通过AMBA4总线技术形成了多个相干的多核处理器集;

- ● AMBA4缓存一致性互连(CCI),允许多个Cortex-A15 MPCore处理器之间的全缓存一致。

高通公司的Scorpion

设计兼容ARMv7-A指令集结构的处理器的不只有ARM公司。2005年,美国高通公司宣布,在ARM的许可下创建了它自己的实现,用了同样的名称——Scorpion。

Scorpion处理器是高通公司Snapdragon平台的一部分,其中包含了上网本、智能手机或其他移动互联网设备的主要功能。

高通面向公众提供了较少的信息,尽管它提到了Scorpion与Cortex-A8处理器有很多相似点,也是基于ARMv7-A体系结构的实现,ARMv7-A——超标量和双发,以及对VFP和NEON(在高通的新闻稿上称为VeNum媒体处理引擎)的支持。

然而相比之下还是有很多差异的,Scorpion可以在其NEON执行中并行处理128位数据,具有1个13级的加载/存储流水线和2个整数流水线,其中一个是10级,只能执行简单的算术运算指令(如加减),而另一种是12级,可以执行所有的数据处理操作,包括乘法。

Scorpion还有1个23级的floating-point/SIMD的流水线和VFPv3操作流水线。

这点内容确实有点老了,现在大多数都是基于v8的架构。但是技术都是向后兼容的,所以也不用太过纠结。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 通信入门系列——傅里叶级数和傅里叶正反变换

- 计算机找不到msvcr100.dll无法继续执行的5种解决方法,实测有效

- Lowest cost with low-power CPLD

- YOLOv8改进 | 检测头篇 | 利用DySnakeConv改进检测头专用于分割的检测头(全网独家首发,Seg)

- 【Linux】网络诊断 traceroute命令详解

- CentOS Linux操作系统源码安装最新Redis版本,使用JSON数据类型踩入新坑

- Spark避坑系列一(基础知识)

- 算法-从树某节点到顶级的id,拼接成字符串

- 《计算机科学中的建模技术》复习点

- Nginx+Promtail+Loki+Grafana 升级ELK强大工具