【INTEL(ALTERA)】F-tile 参考时钟和系统 PLL 时钟英特尔? FPGA IP无法锁定在特定频率?

发布时间:2024年01月20日

??

说明

由于在英特尔? Quartus? Prime Pro Edition 软件 22.2 及更早版本中存在一个问题,您可能会观察到 F-tile 参考时钟和系统 PLL 时钟英特尔? FPGA IP无法锁定:

- 999.9 MHz,参考时钟频率设置为 323.2 MHz。

- 506.88 MHz,参考时钟频率设置为 245.76 MHz。

解决方法

要变通解决此问题,您需要执行以下步骤:

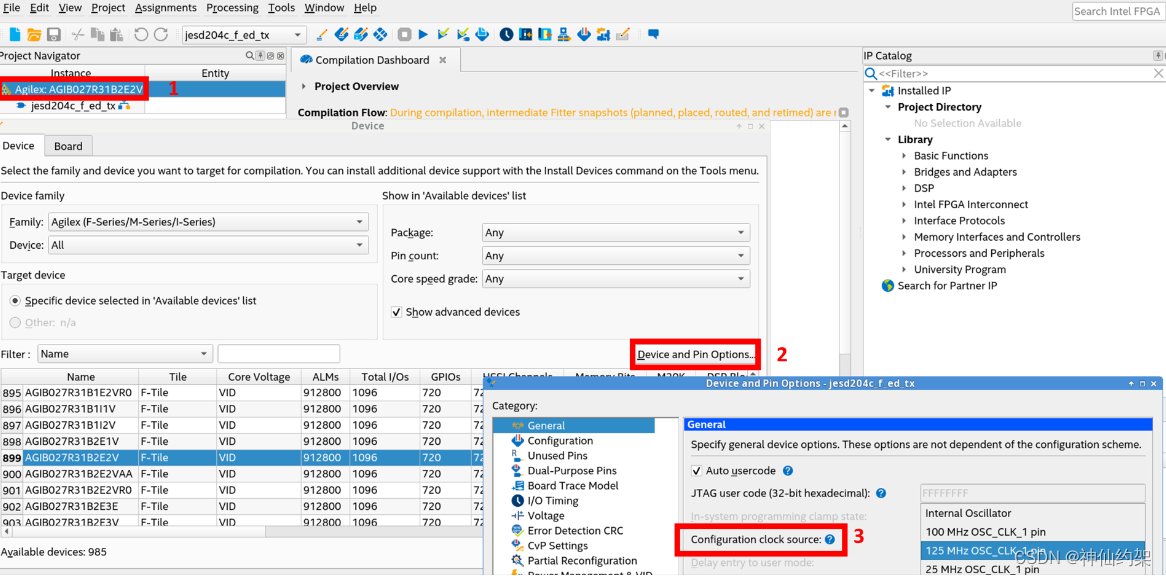

- 在项目导航器中,?双击?OPN(订购部件号)。

- 在弹出窗口中,单击“设备和引脚选项”按钮。

- 在“常规”类别中,将“配置时钟源”参数从“内部振荡器”更改为:

- 100 MHz OSC_CLK_1 引脚,或

- 125 MHz OSC_CLK_1引脚

- 重新编译设计。

- 为?OSC_CLK_1引脚提供一个频率正确的?外部参考时钟?。“OSC_CLK_1”引脚位置可在开发套件原理图中找到。

注意:对于 OPN 以后缀 VR0、VR1 和 VR2 结尾的 Intel Agilex? F-tile 设备,您需要使用 Prime Programmer 英特尔? Quartus? 21.4 版本来运行上述解决方法。

文章来源:https://blog.csdn.net/sqqwm/article/details/135658045

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 解析在线教育系统源码架构:构建可扩展的企业教学平台

- 抖店怎么做?新手又该如何从头开始运营?

- mysql5.7之从入门到放弃

- [Spring 基础] IOC控制反转

- 【NTN 卫星通信】Starlink,费用、服务、市场(二)

- Java学习系列(九)

- 算法学习系列(二十五):质数

- 力扣精选算法100题——水果成篮(滑动窗口专题)

- JAVA开发的源码-供应商采购招标管理系统源码

- element input组件自动失去焦点问题解决