ARM day4 汇编及硬件编程

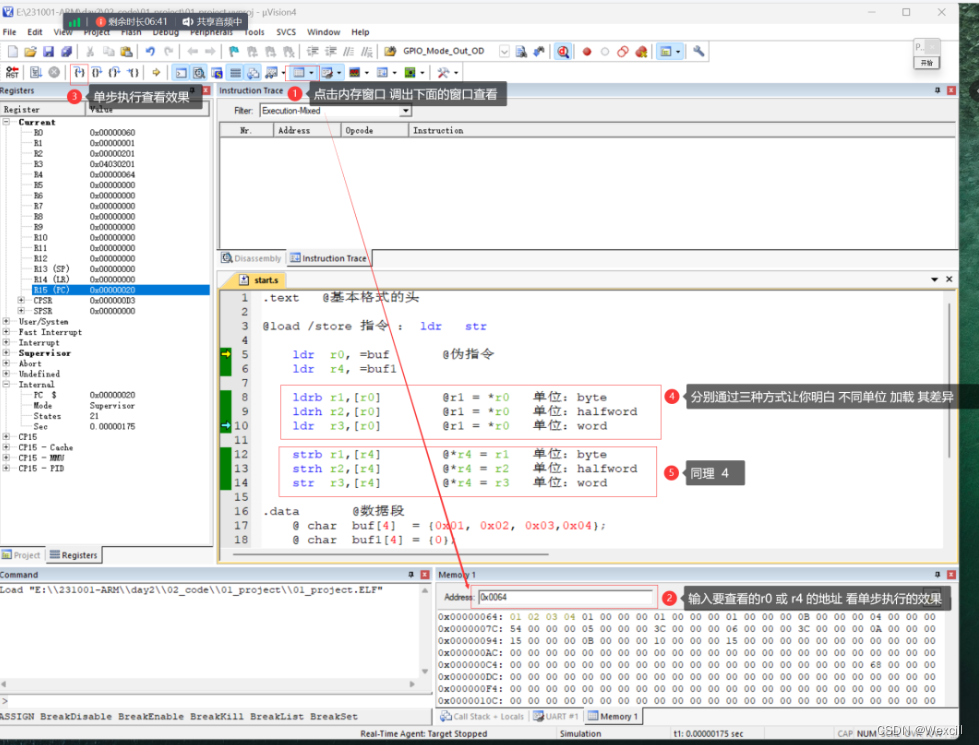

一、指令--数据从内存到cpu--ldr、str

| load -- 加载 读 store -- 存储 写? 在ARM 架构下, 数据从内存到cpu 直接的移动只能通过 LDR/STR来完成? |

| str ?r2, ?[r0] ? //把r2 的数据 ?存储(写)到 r0 地址 ? ? ?*((int *) r0) ?= r2 往右写 往左读 |

| ? ? 三种索引方式: ? ? LDR R0,[R1, #4] ?//r0 = *((int *)(r1 + 4))? ? ? ? 只读取数据 ? ? LDR R0,[R1, #4]! // r0 = *((int *)(r1 + 4)) ?r1 += 4? ? ? ?读取数据且更新r1地址 ? ? LDR R0, [r1],#4 ?//r0 = *((int *)r1) ?r1 += 4? ? ? ? ?读取数据后更新r1地址? |

二、pre or post indexed寻址

?

| ldrb | 存一个数据 |

| ldrh | 存两个数据 |

| ldr | 存四个数据 |

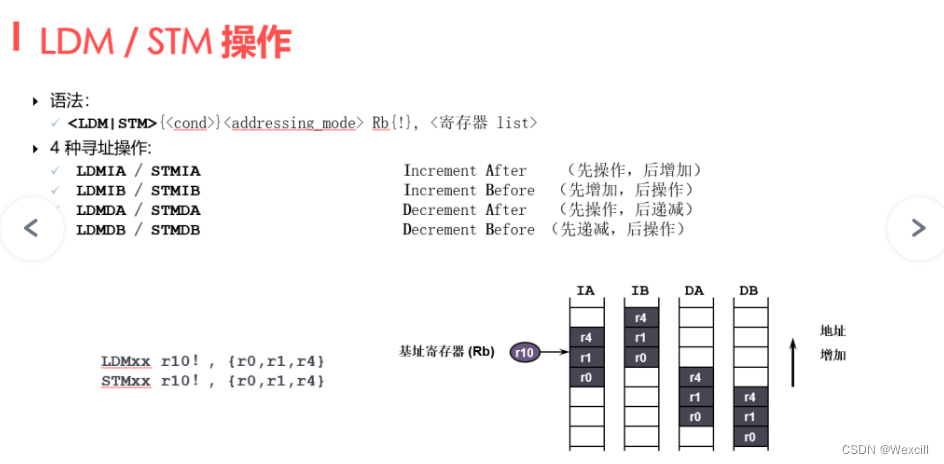

三、stmXX / ldmXX

| ?? ? stm ?---store ?much ? | 多数据存储(写),将寄存器的值 存到地址上? |

| ??????ldm ? --- load much ? | 多数据加载(读),将地址上的值加载到寄存器 |

XX有八种类型

| IA(increase After ) | 每次传送后地址加 4 ,寄存器从左到右执行 STMIA ?R0, {R1, LR} //先存R1, 将R0的地址 加上4 再存 LR //将r0 地址中的值 逐个写入 寄存器 r0, r1, r2? |

| IB(increase Before ?) | 每次传送前 地址加 4 ,同上 |

| DA (decrease ?After) | 每次传送后 地址 减 4寄存器从右往左执行 STMDA R0, {r1, lr} ?//先存LR,再存 r1? |

| DB(decrease ?Before) | 每次传送前 地址减4 ,同上? |

| FD满递减堆栈 | 每次传递前 地址减4 (LDMFD--LDMIA ? ?STMFD--STMDB ) |

| FA满递增堆栈 | 每次传送后地址减4 (LDMFA--LDMDA; STMFA--STMIB) |

| ED空递减堆栈 | 每次传送前地址加4 (LDMED--LDMIB; STMED--STMDA) |

| EA空递增堆栈 | 每次传送后地址加4 (LDMEA--LDMDB; STMEA--STMIA) |

| ? ?四种栈 | ? ? ? ? 空栈:栈指针指向空位,每次存入时可以直接存入然后栈指针移动一格;而取出时需要先移动一格才能取出 ?? ??? ?满栈:栈指针指向栈中最后一格数据,每次存入时需要先移动栈指针一格再存入;取出时可以直接取出,然后再移动栈指针 ?? ??? ?增栈:栈指针移动时向地址增加的方向移动的栈 ?? ??? ?减栈:栈指针移动时向地址减小的方向移动的栈 |

?? ?eg: 一般出栈/入栈

?? ??? ?ldmfd sp!,{r0,r1,r2} ? //将sp中值逐个写入到寄存器r0 R1 R2中

?? ??? ?stmfd sp!,{r0,r1,r2} ? //将寄存器r0 R1 R2中逐个写入到sp中

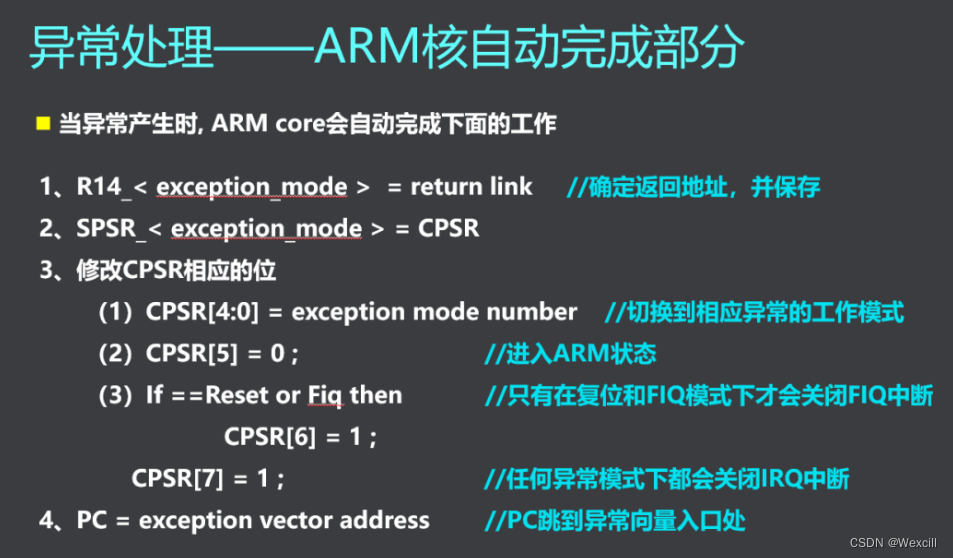

重要:异常处理

?? ??? ?ldmfd sp!,{r0-r12,pc}^ --- 出栈 恢复现场

?? ??? ?stmfd sp!,{r0-r12,lr} ?--- 入栈 保护现场

?? ?SP后面的!表示要更新sp的值 sp -= n

?? ?^的作用:在目标寄存器中有pc时,会同时将spsr写入到cpsr,一般用于从异常模式返回。

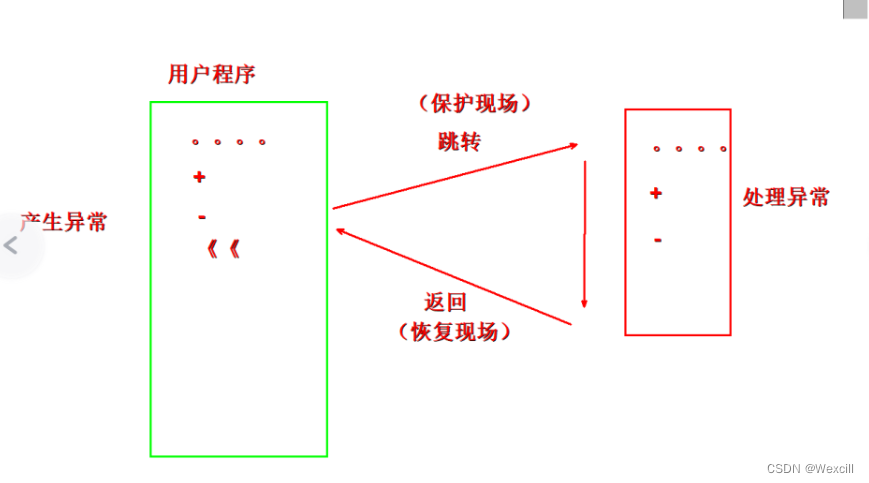

四、中断和异常

| 异常的定义 | 芯片内部的调度 |

| 异常(exception ?)机制 | 处理器,顺序执行程序指令的过程中,突然遇到异常的事情,而中止执行的当前程序,转而去处理异常。? |

| 异常与中断的最大区别 | 中断--外部因素引起? 异常--内部因素引起 (内因:本身硬件故障,程序故障,非法指令,或执行等特殊的系统服务指令等引起的) |

异常源

?

| ? ? 1、复位异常 reset ? ? 2、数据异常 ? data abort ? ? 3、FIQ 异常 ? fiq? ? ? 4、IRQ 异常 ? irq ? ? 5、预取指 异常 ? ?prefetch abort? ? ? 6、软中断 异常?? ?swi? ? ? 7、未定义指令异常 ? undefined ?instruction? |

异常优先级

| ?? ?异常优先级{ 为什么FIQ的响应速度比IRQ快? FIQ优先级更高 FIQ向量位于异常向量表的最末,异常处理程序可以从异常量处连续执行 FIQ有五个额外的私有寄存器,中断处理必须保护其使用的非私有寄存器 |

异常处理过程

?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 什么台灯护眼效果好医生解答?解锁那些效果好的护眼台灯

- 【基础知识】大数据组件HDFS简述

- Segment Anything model部署和使用

- Linux学习(1):目录结构、编辑器和用户管理

- Unity Shader 的模板测试效果

- BC115超级圣诞树

- 如何在 Windows 10/11 上恢复已删除的 Word 文档

- 【全网最细】爆肝3天,2023年年度音乐+图片+热词终于出来了,来看看你知道几个?

- Copilot插件:解放你的生产力

- 数据结构与算法教程,数据结构C语言版教程!(第一部分、数据结构快速入门,数据结构基础详解)一