高云GW1NSR-4C开发板M3核串口通信

1.PLLVR频率计算

高云的M3核要用到PLLVR核,其输出频率=FCLKIN*(FBDIV_SEL+1)/(IDIV_SEL+1),但同时要满足FCLKIN*(FBDIV_SEL+1)*ODIV_SEL)/(IDIV_SEL+1)的值在600MHz和1200MHz之间。例如官方示例,其输入频率FCLKIN=50MHz,要输出80MHz,则pllvr_inst.IDIV_SEL = 4,pllvr_inst.FBDIV_SEL = 7,pllvr_inst.ODIV_SEL = 8,计算可知50*(7+1)/(4+1)=80,同时50*(7+1)*8/(4+1)=640,满足要求。

2.官方代码在27M时钟下的适配

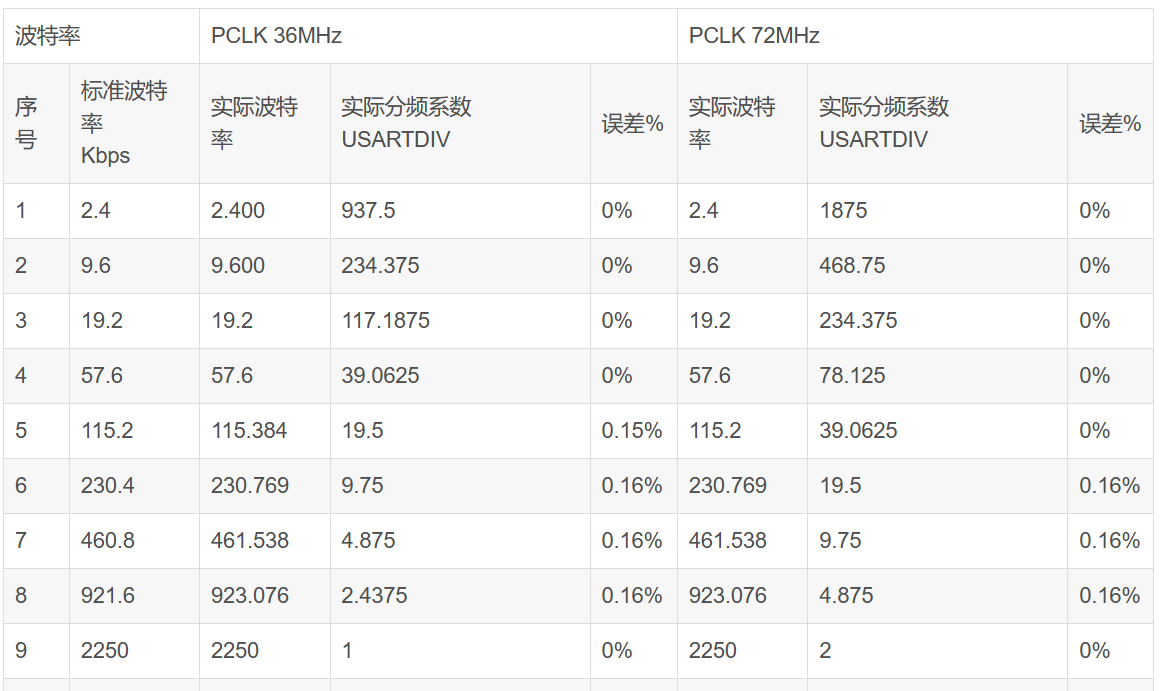

已知主频和波特率之间的误差如下:

取115200bps,选择72M主频,50M输入频率下,PLLVR配置,可以看出实际频率只能是71.875M:

相应参数如下:

defparam pllvr_inst.IDIV_SEL =15;

defparam pllvr_inst.FBDIV_SEL = 22;

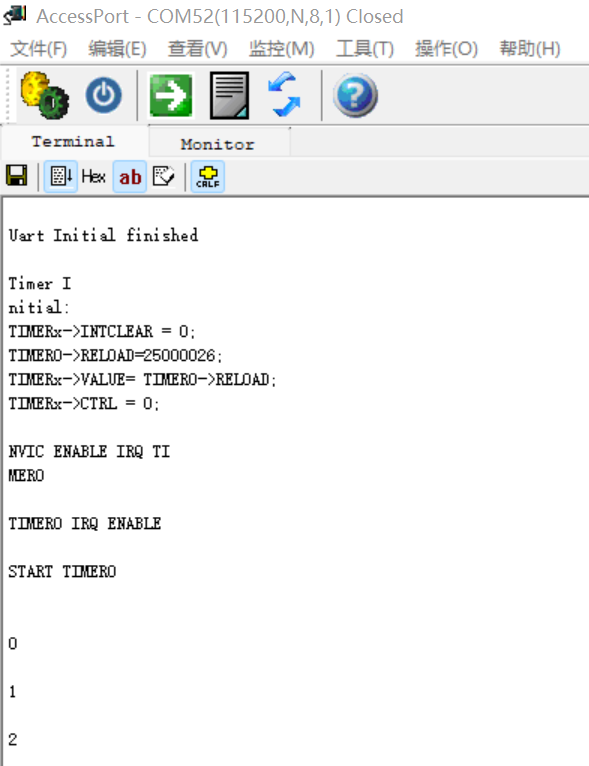

defparam pllvr_inst.ODIV_SEL = 16;已知高云GW1NSR-4C开发板板载时钟为27M,根据以上参数,可知其实际频率为27*(22+1)/(15+1)=38.8125,同时有27*(22+1)*16/(15+1)=621,满足大于600小于1200的要求。以上是FPGA工程的修改,MCU工程进行相应的修改,打开\EMPU(GW1NS-4C)_V1.2\ref_design\MCU_RefDesign\Keil_RefDesign\uart\SYSTEM\system_gw1ns4c.c文件第65行找到?#define __XTAL,把值改为77625000。编译EMPU(GW1NS-4C)_V1.2\ref_design\MCU_RefDesign\Keil_RefDesign\uart\PROJECT下的uart工程,上传,串口调试助手测试效果如下:

FPGA工程中gowin_pllvr.v文件的defparam pllvr_inst.FCLKIN参数为输入频率,但不宜直接更改,必须按照以上计算以符合规范。也就是说,虽然FPGA工程代码所写晶振频率50M,但实际用的是27M,PLL输出频率38.8125M,而MCU工程则按照38.8125M(晶振为77.625M)主频配置。另外要特别注意,PLL输出频率不要超过80M,否则有很大可能导致MCU无法运行。

3.PLLVR主频特别说明

高云M3内核应用时,需要PLLVR核,默认时钟输入为50M,若根据开发板实际改为27M,经广泛测试,有可能会出现不可预料的问题:(1)MCU无法启动;(2)MCU可以硬启动(即上电启动),但reset按键会导致死机;(3)串口无法通信。而且这些问题随机出现,甚至不同开发板出现的问题都不同。故而,代码中保持50M输入频率不变,MCU编程中根据实际对主频作出调整。

4.官方代码

Embedded M3 Hard Core in GW1NS-4C - 科技 - 广东高云半导体科技股份有限公司 (gowinsemi.com.cn)

5.pllvr另外一种设置方法

先用27M晶振进行设置pll输出(不大于43.5M。代码生成后将FCLKIN改为50。建议pllvr输出频率选择40.5M,),此时FBDIV_SEL=2,IDIV_SEL=1,ODIV_SEL=16,换成50后输出为75M,小于80M,代入FCLKIN*(FBDIV_SEL+1)*ODIV_SEL)/(IDIV_SEL+1)得1200,全都符合要求,经测试115200bps串口工作稳定可靠。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- springboot/java/php/node/python博物馆信息管理【计算机毕设】

- 企业电子招投标系统源码之电子招投标系统建设的重点和未来趋势

- hyperf 二十三 分页

- 【Leetcode】2696. 删除子串后的字符串最小长度

- Java研学-Tomcat服务器

- 宠物空气净化器哪个品牌高质量?猫用空气净化器五大品牌推荐

- 河南选调生报名照片上传成功,不能大于50kb

- [Probability] 1.5 story proof and non-naive def

- el-radio-button自适应充满盒子的写法

- R 语言中的 pnorm 方法与 Python scipy 的 norm.cdf、norm.sf 等价