关于FPGA仿真复位信号和实际板子复位信号的吐血大坑

发布时间:2024年01月08日

最近在研究mipi dphy IP下载到板子上进行验证的初步流程问题

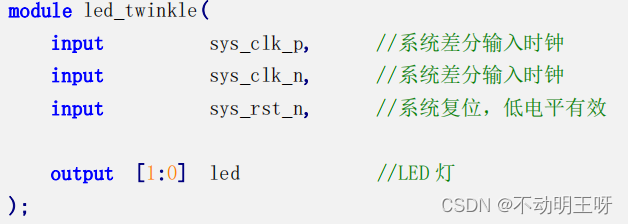

IP的example案例里面,系统复位全是高电平复位,低电平工作

想当然的打通IP流程,写工程的时候也使用了高电平复位,低电平复位

结果调试了N轮,init_done信号一直没有拉高。

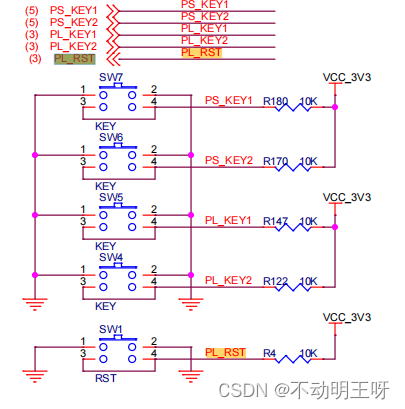

后来查询了电路图,发现是高电平工作,低电平复位

再重新看例程,是低电平复位,吐血!!!

记录一下

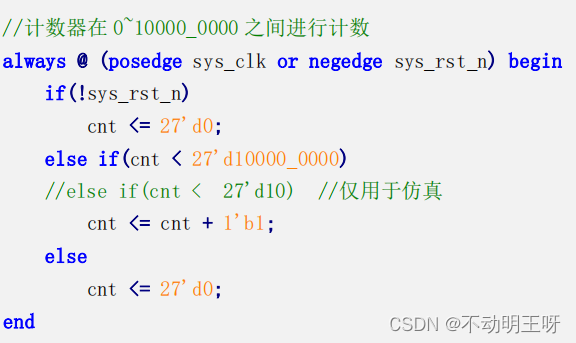

FPGA例程仿真没问题,下载到板子出错,因素之一可能是复位信号不一样。

文章来源:https://blog.csdn.net/qq_36683398/article/details/135462928

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- php之 校验多个时间段是否重复

- 「第四章」python-docx 为word添加表格、设置表格边框

- 【机器学习】决策树

- 如何预防最新的.halo勒索病毒感染您的计算机?

- Linux下配置静态ip地址

- 【Docker-Dev】Mac M2 搭建docker的redis环境

- conda环境下nvrtc: error: invalid value for --gpu-architecture解决方法

- NLP论文阅读记录 - 2021 | WOS 智能树提取文本摘要深度学习

- CRC循环冗余校验

- 2.5 运输层01