【FPGA & Modsim】 抢答器设计

实验题目:??抢答器设计 ????????????????????????????????????

实验目的:??掌握应用数字逻辑设计集成开发环境进行抢答器设计的方法;掌握时序逻辑电路设计的过程。?????????????????????????

实验内容:

1、设计支持3名参赛者的抢答器,并具有主持人控制的复位功能;

2、当一名参赛者按下抢答键时,对应的LED灯亮起,屏蔽其他选手;

3、分析实验结果,验证电路的功能是否符合设计要求。

实验步骤:

1、在数字逻辑集成开发环境中新建一个抢答器工程;

2、编写Verilog?HDL源程序;

3、编译和逻辑综合源程序;

4、编写Verilog?HDL仿真测试程序;

5、调用数字逻辑设计仿真环境对源程序进行仿真;

6、安装输入/输出端口建立约束文件;

7、下载到实验开发板,观察实践运行结果。

实验数据记录:

- 写出编写的Verilog?HDL源程序。

module question_counter (

????input wire clk,

????input wire reset,

????input wire [2:0] button_pressed,

????output reg [2:0] led_on

);

????always @(posedge clk or posedge reset) begin

????????if (reset) begin

????????????led_on <= 3'b000;

????????end else begin

????????????case (button_pressed)

????????????????3'b001: led_on <= 3'b001; // Player 1

????????????????3'b010: led_on <= 3'b010; // Player 2

????????????????3'b100: led_on <= 3'b100; // Player 3

????????????????default: led_on <= 3'b000;

????????????endcase

????????end

????end

endmodule

- 写出编写的Verilog?HDL仿真测试程序。

module tb_question_counter;

????reg clk, reset;

????reg [2:0] button_pressed;

????wire [2:0] led_on;

????// 实例化抢答器模块

????question_counter uut (

????????.clk(clk),

????????.reset(reset),

????????.button_pressed(button_pressed),

????????.led_on(led_on)

????);

????// 生成时钟信号

????always #5 clk = ~clk;

????// 初始化信号

????initial begin

????????clk = 0;

????????reset = 1;

????????#10 reset = 0;

????????#10 button_pressed = 3'b001; #10 button_pressed = 3'b010; #10 button_pressed = 3'b100; #10 $finish;

????end

endmodule

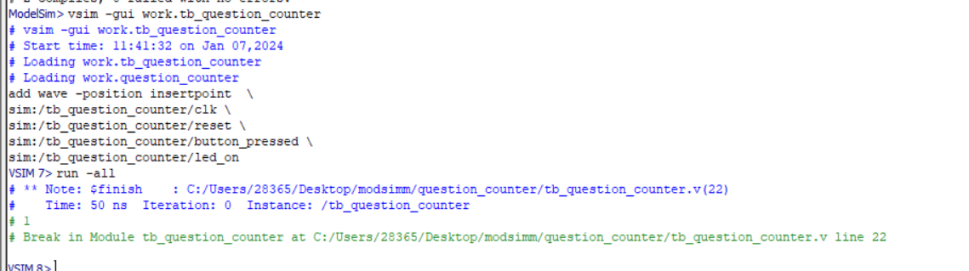

3、画出仿真环境中测试波形图。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- [数据集][目标检测]人员持刀数据集VOC+YOLO格式6923张1类别重制版

- 【AI】YOLO学习笔记

- 医院信息化-6 大模型与医疗

- 教你一篇使用java策略模式实战干起来

- 大华 DSS 数字监控系统 itcBulletin SQL 注入漏洞复现

- PCL 点云SUSAN关键点提取

- CMMI3.0认证的卓越方案!

- react优劣势

- Spring Cloud和Zookeeper的集成,构建高可扩展的分布式系统

- 什么是“私域流量”?