Verilog语法——5.测试文件

发布时间:2024年01月16日

参考资料

【明德扬_verilog零基础入门语法HDL仿真快速掌握-手把手教你写FPGA/ASIC代码设计流程中的应用】

5. 测试文件

5.1 认识测试文件(testbench)

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。

但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估

那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟

平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和

校验。

5.2 测试文件编写流程

小贴士:ps是皮秒,ns是纳秒

- 1ns 【纳秒】= 1000ps【皮秒】(纳秒是-9次方,皮秒是-12次方)

5.2.1 定义时间标尺

`timescale 1ns / 1ps

5.2.2 定义信号类型

//时钟和复位

reg clk ;

reg rst_n ;

//uut 的输入信号

reg[3:0] din_0 ;

reg din_1 ;

//uut 的输出信号

wire dout_0 ;

wire[4:0] dout_1 ;

//时钟周期,单位为ns,可在此修改时钟周期

parameter CYCLE = 20;

//复位时间,此时表示复位3个时钟周期的时间

parameter RST_TIME = 3;

5.2.3 例化测试模块(.v文件)

//待测试的模块例化

module_name uut(

.clk (clk) ,

.rst_n (rst_n) ,

.din_0 (din_0) ,

.din_1 (din_1) ,

.dout_0 (dout_0) ,

.dout_1 (dout_1)

// ,更多...

);

5.2.4 输入信号驱动

//生成本地时钟:50M

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

//产生复位信号

initial begin

rst_n = 1;

#2;

rst_n = 0;

#(CYCLE*RST_TIME);

rst_n = 1;

end

//输入信号din0赋值方式

initial begin

#1;

//赋初值

din_0 = 0;

#(10*CYCLE);

//开始赋值

end

//输入信号din1赋值方式

initial begin

#1;

//赋初值

din_1 = 0;

#(10*CYCLE);

//开始赋值

end

5.3 常用信号的编写方法

**

注意,下面三个信号的initial是同时执行的!

**

不相关的信号可以分别单独initial

5.3.1 时钟信号

//生成本地时钟:50M

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

5.3.2 复位信号

如果需要间隔较长一段时间才复位,可以修改RST_TIME值,将其变大些,即间隔更多周期才复位

//产生复位信号

initial begin

rst_n = 1;

#2;

rst_n = 0;

#(CYCLE*RST_TIME);

rst_n = 1;

end

5.3.3 其他信号

#1; 是指时钟上升沿后的一点时间进行变化,目的是在上升沿期间保持信号稳定

//输入信号din0赋值方式

initial begin

#1;

//赋初值

din_0 = 0;

#(10*CYCLE);

//开始赋值

end

5.4 测试文件模板(整体)(不厌其烦)

module TestBench_name();

//时钟和复位

reg clk ;

reg rst_n ;

//uut 的输入信号

reg[3:0] din_0 ;

reg din_1 ;

//uut 的输出信号

wire dout_0 ;

wire[4:0] dout_1 ;

//时钟周期,单位为ns,可在此修改时钟周期

parameter CYCLE = 20;

//复位时间,此时表示复位3个时钟周期的时间

parameter RST_TIME = 3;

//待测试的模块例化

module_name uut(

.clk (clk) ,

.rst_n (rst_n) ,

.din_0 (din_0) ,

.din_1 (din_1) ,

.dout_0 (dout_0) ,

.dout_1 (dout_1)

// ,更多...

);

//生成本地时钟:50M

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

//产生复位信号

initial begin

rst_n = 1;

#2;

rst_n = 0;

#(CYCLE*RST_TIME);

rst_n = 1;

end

//输入信号din0赋值方式

initial begin

#1;

//赋初值

din_0 = 0;

#(10*CYCLE);

//开始赋值

end

//输入信号din1赋值方式

initial begin

#1;

//赋初值

din_1 = 0;

#(10*CYCLE);

//开始赋值

end

endmodule

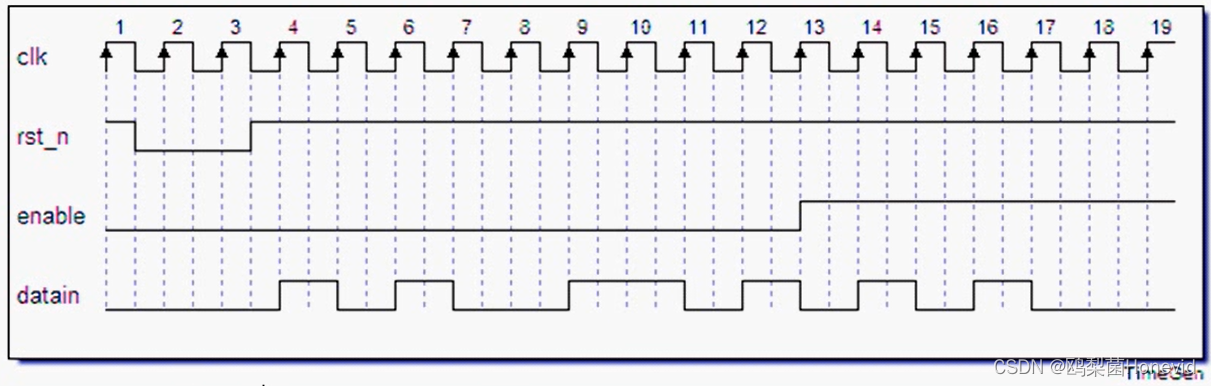

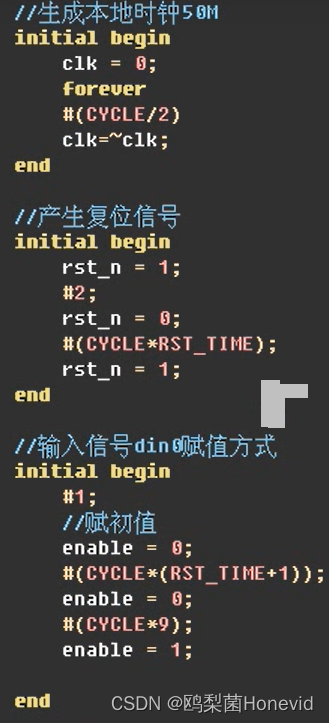

5.5 编写测试文件例题

要求输入的波形图

- 时钟clk和复位信号rst_n照抄模板即可

- enable要数间隔几个时钟周期后置1

- datain要在相应的时钟周期出取0或1

文章来源:https://blog.csdn.net/qq_48035645/article/details/135575542

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!