计算机体系结构----重排序缓冲(ROB)

发布时间:2024年01月10日

ROB的思想:不按顺序完成指令,但在使结果对体系结构状态可见之前重新排序

- 当指令被解码时,它会在 ROB 中保留下一个顺序条目

- 当指令完成时,它将结果写入 ROB 条目

- 当指令在 ROB 中最早并且无一例外地完成时,其结果移动到寄存器堆或存储器中

- 缓冲有关已解码但尚未停用(retire)/提交(commit)的所有指令的信息

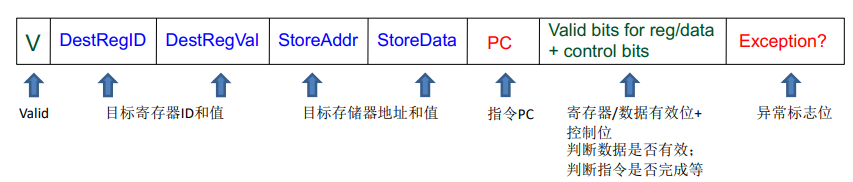

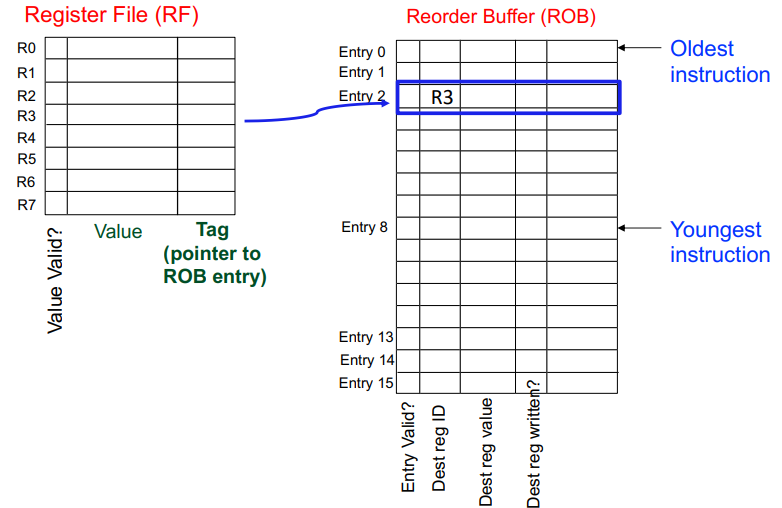

重排序缓冲的条目ROB Entry

- 正确地将指令重新排序回程序顺序

- 使用指令的结果更新架构状态,如果指令可以毫无问题地退出

- 精确处理异常/中断,如果需要在停用指令之前处理异常/中断

- 需要有效位来跟踪结果的准备情况,并找出指令是否已完成执行

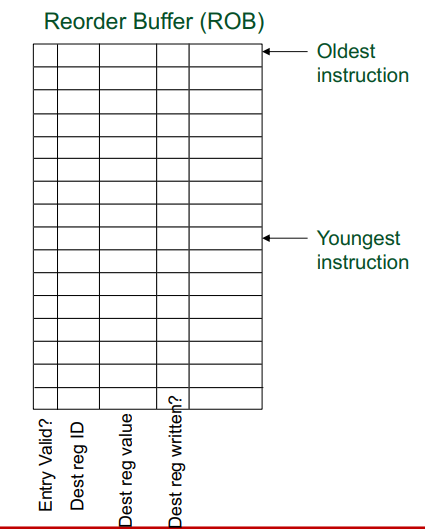

ROB是环形缓冲器

ROB存在两个指针,一个用来指示最早进入ROB的指令,一个用来指示最晚的。

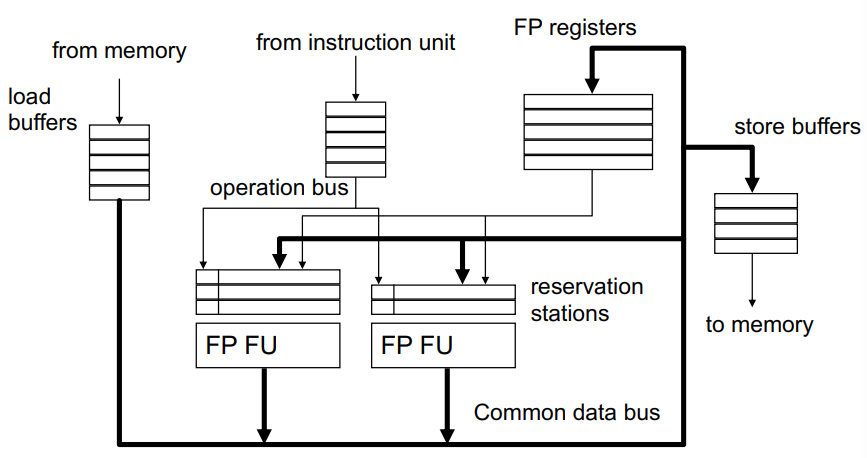

Tomasulo系统复习

详细的Tomasulo系统解释点击这个:计算机体系结构----寄存器重命名/Tomasulo算法

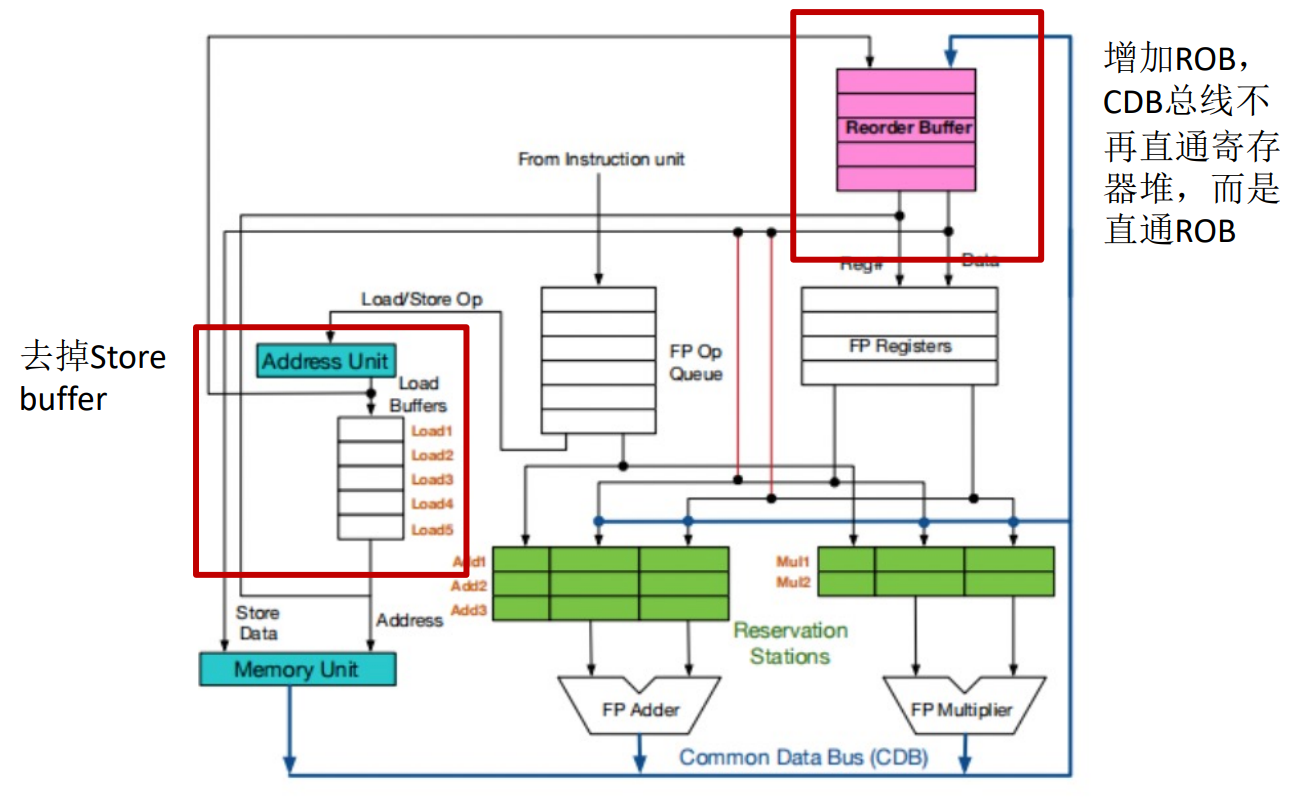

Tomasulo+ROB

- 在指令完成时首先将结果写入 ROB

- 在提交时将结果写入寄存器堆

- 如果后面的指令需要重排序缓冲区中的值怎么办?

- 一种选择:流水线停顿

- 更好的做法:从重排序缓冲区中读取值。

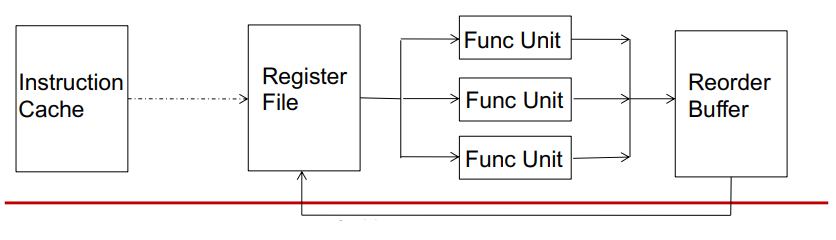

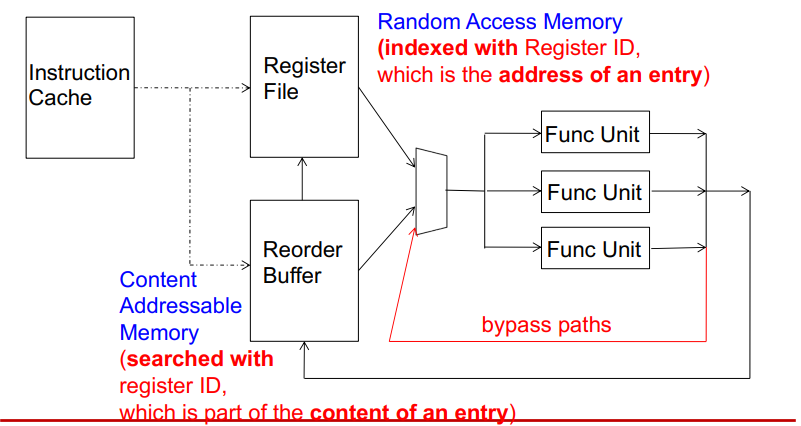

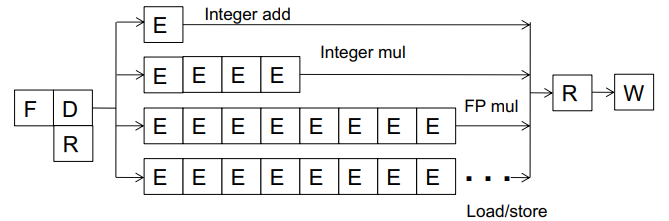

一个简易的假如ROB的流水线示意图如下:

访问ROB的方法1

寄存器值可以位于寄存器堆、重新排序缓冲区(或旁路/转发路径)中。

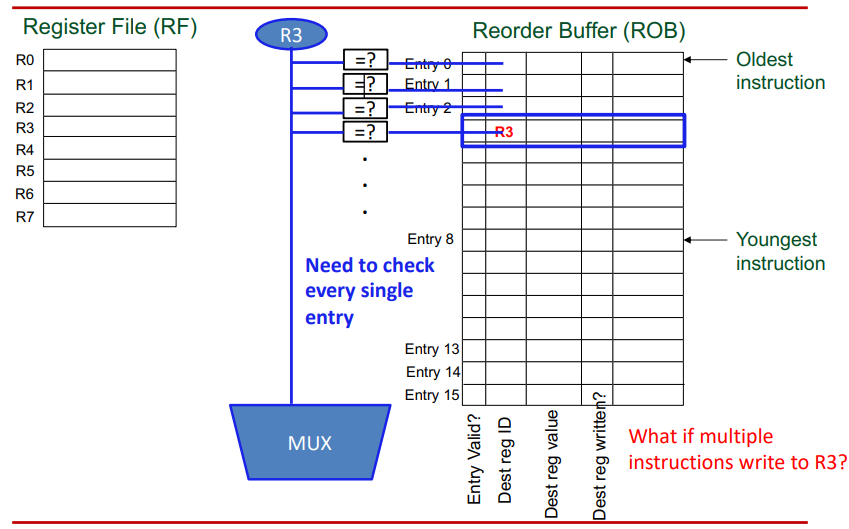

看上图可以发现,访问ROB中所需求的寄存器的值就是遍历法,从上往下一一比对ROB Dest reg ID 直到一样。

访问ROB的方法2

- 首先访问寄存器堆(检查寄存器是否有效)

- 如果寄存器无效,寄存器堆存储包含(或将包含)寄存器值的重新排序缓冲区条目的 ID

- 寄存器到 ROB 条目的映射: 如果寄存器堆有写入寄存器的飞行指令,则寄存器堆将寄存器映射到重新排序缓冲区条目

- 访问重新排序缓冲区

- 现在, 重新排序缓冲区不需要是内容可寻址的

相较于访问ROB方法1,方法2在寄存器堆中添加了Tag位,用于直接映射到ROB的条目,方便寻找。

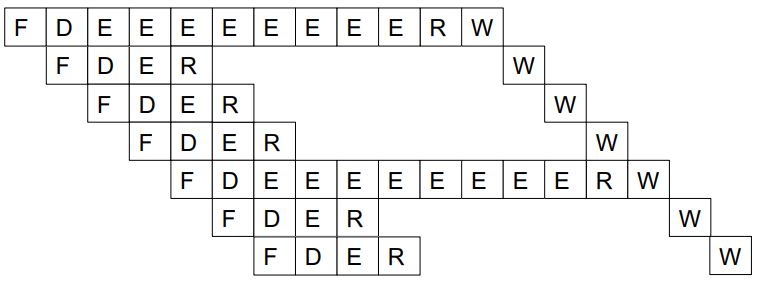

ROB的流水线构造

- Decode(D):访问regfile/ROB,在ROB中分配条目,检查指令是否可以执行,如果可以,则调度指令

- Execute (E):指令可以无序完成

- Completion (R):将结果写入重新排序缓冲区

- Retirement/Commit (W):检查异常;如果没有,则将结果写入架构寄存器文件或存储器;否则,刷新流水线并从异常处理程序开始

- 按顺序调度/执行、无序完成、按顺序停用(retirement)

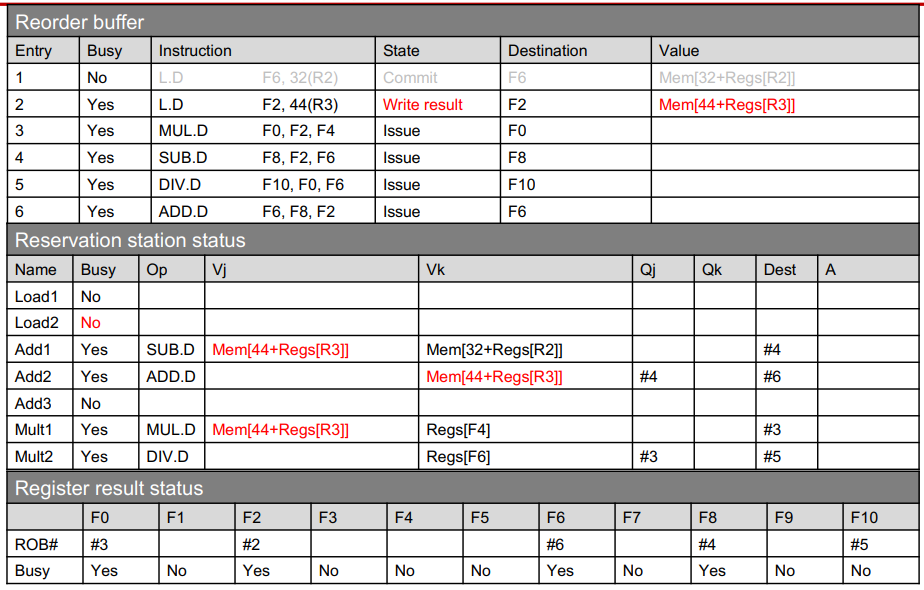

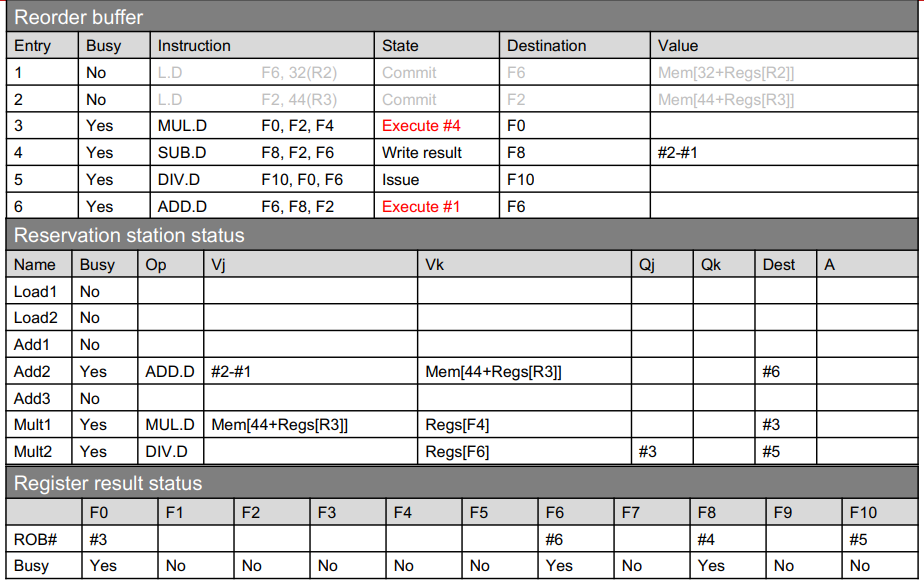

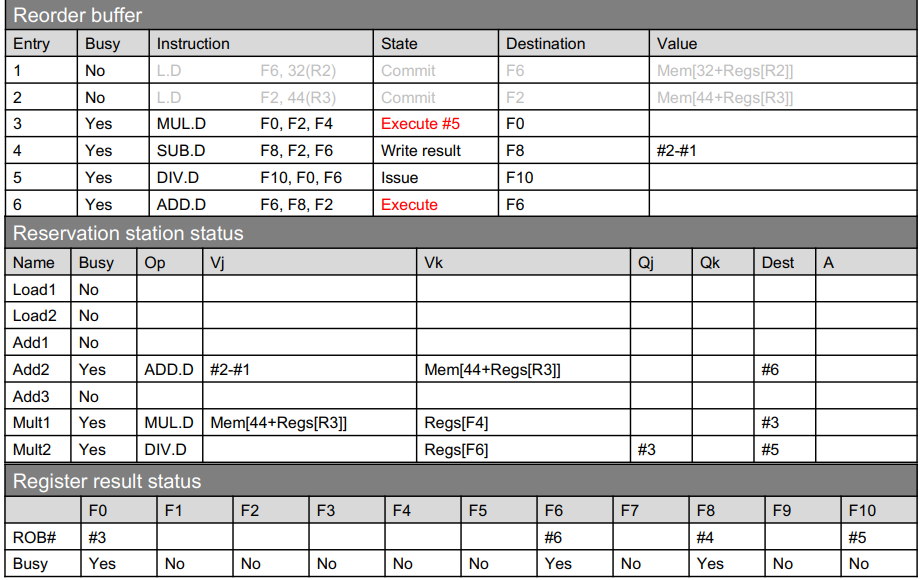

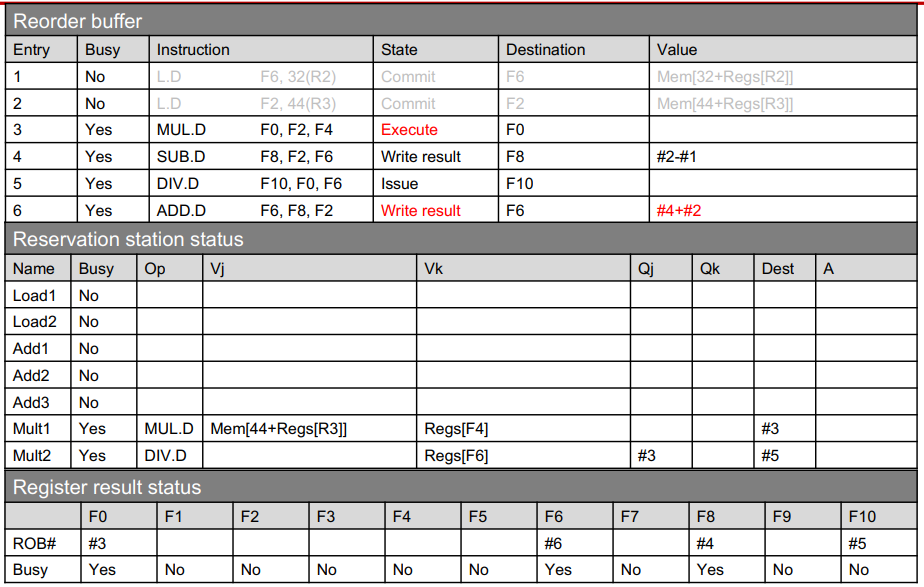

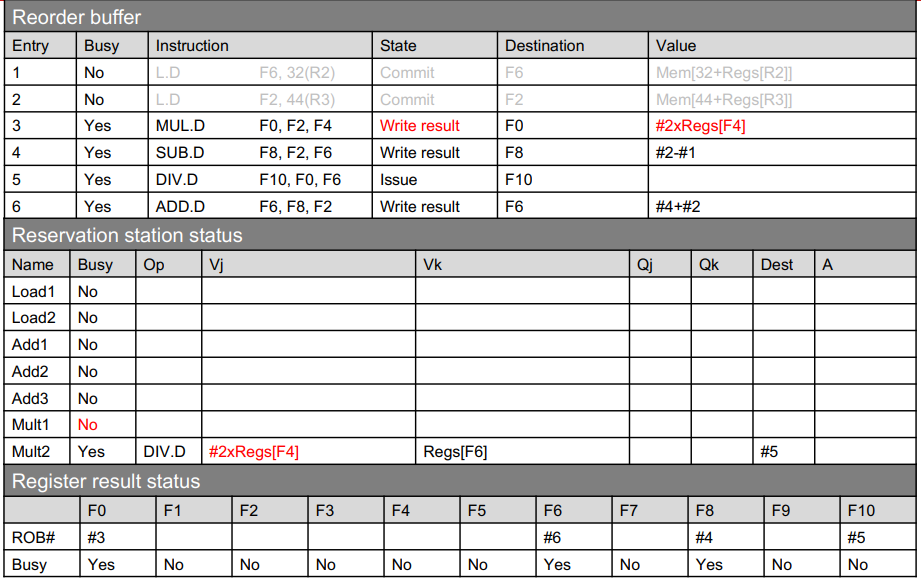

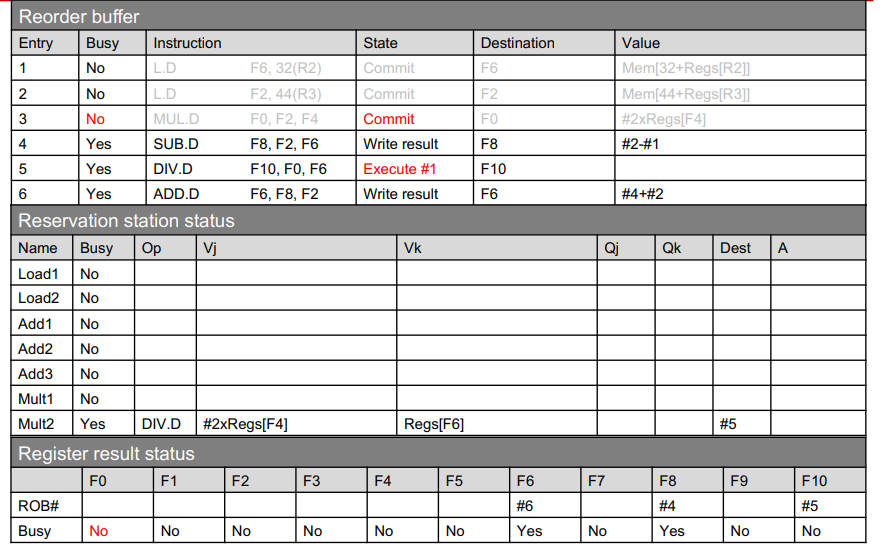

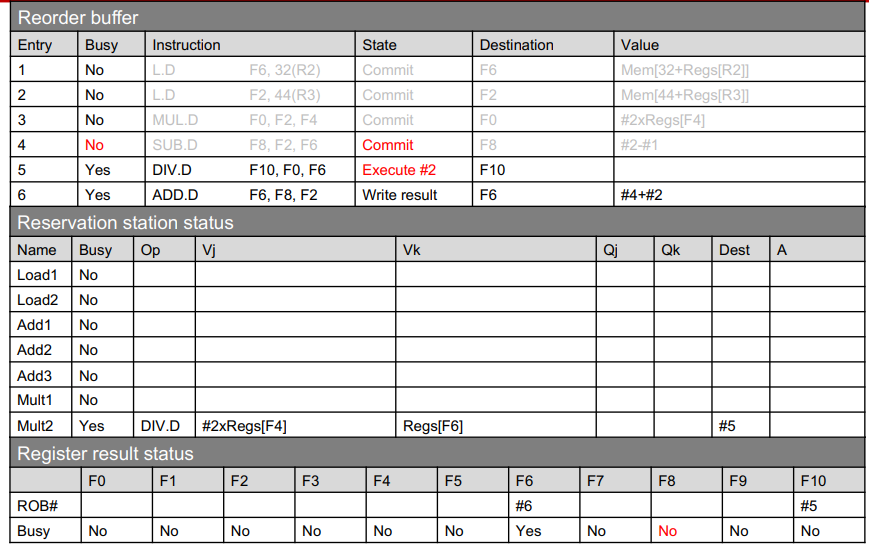

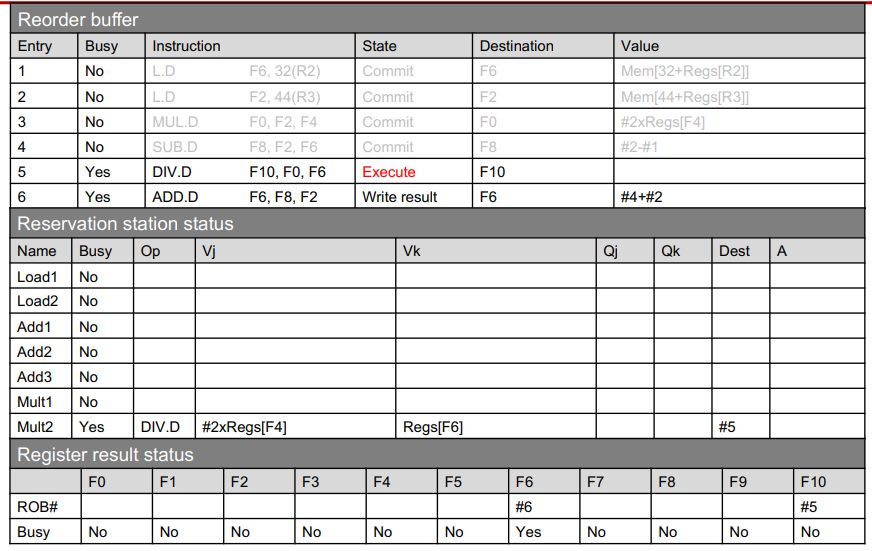

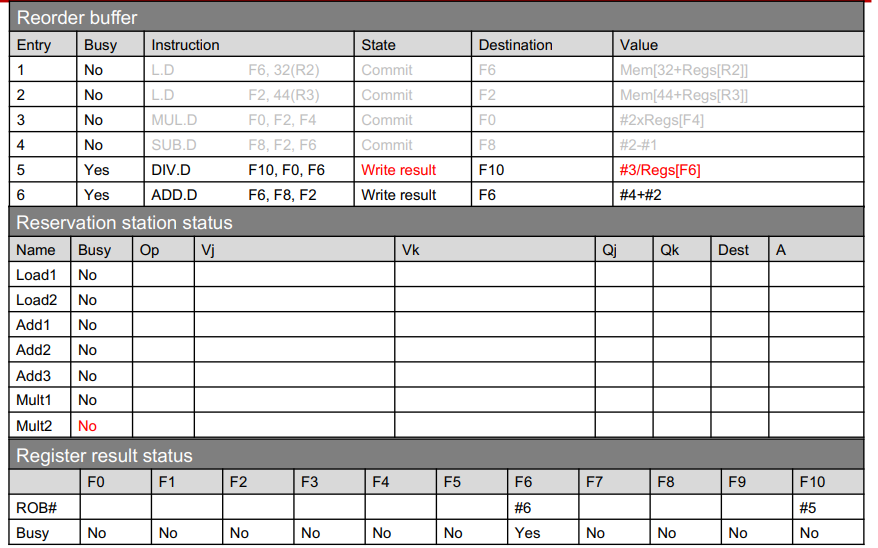

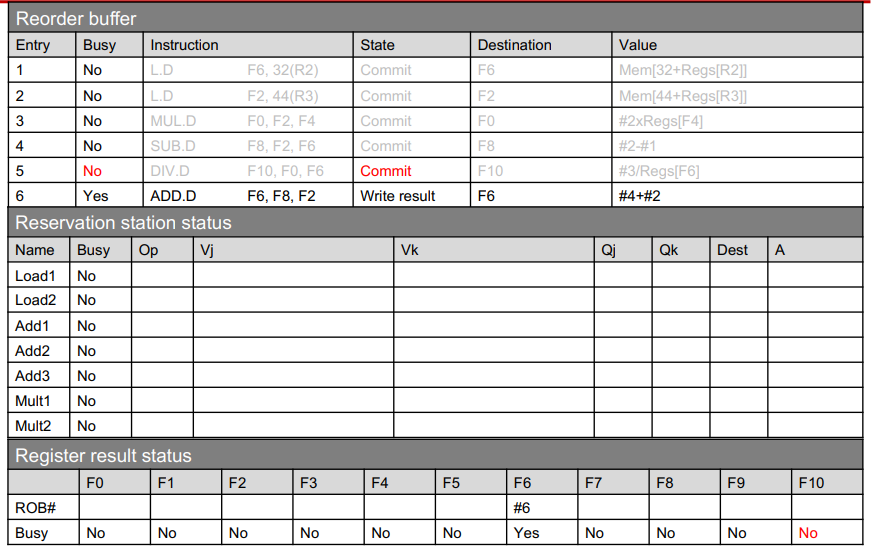

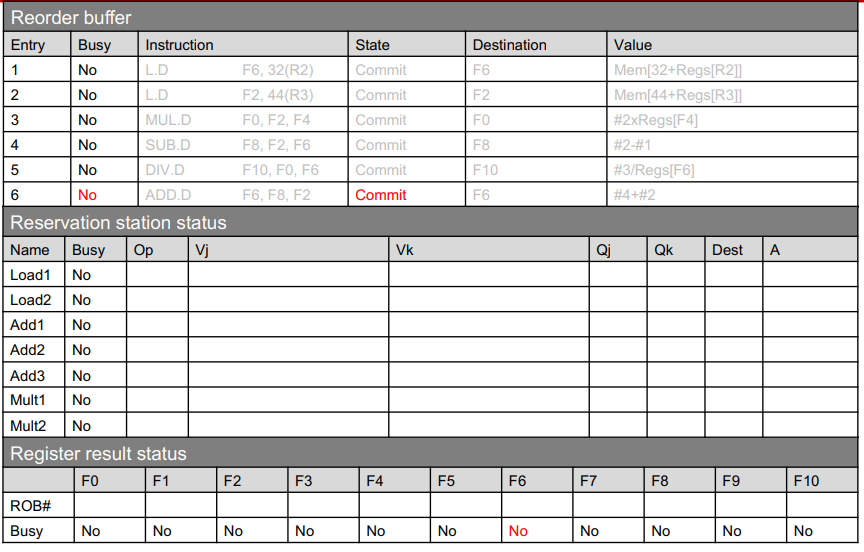

Tomasulo+ROB运行示例

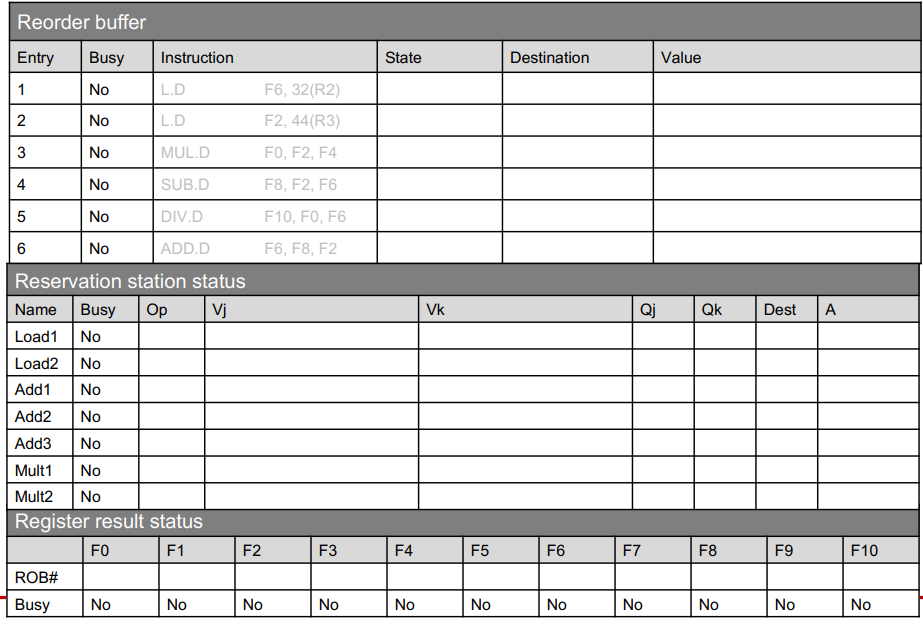

初始状态

假设延时:Load:1, Add:2, Mult:6, Divide:12

可以发现 ,每条指令都在ROB中有一个条目(entry)

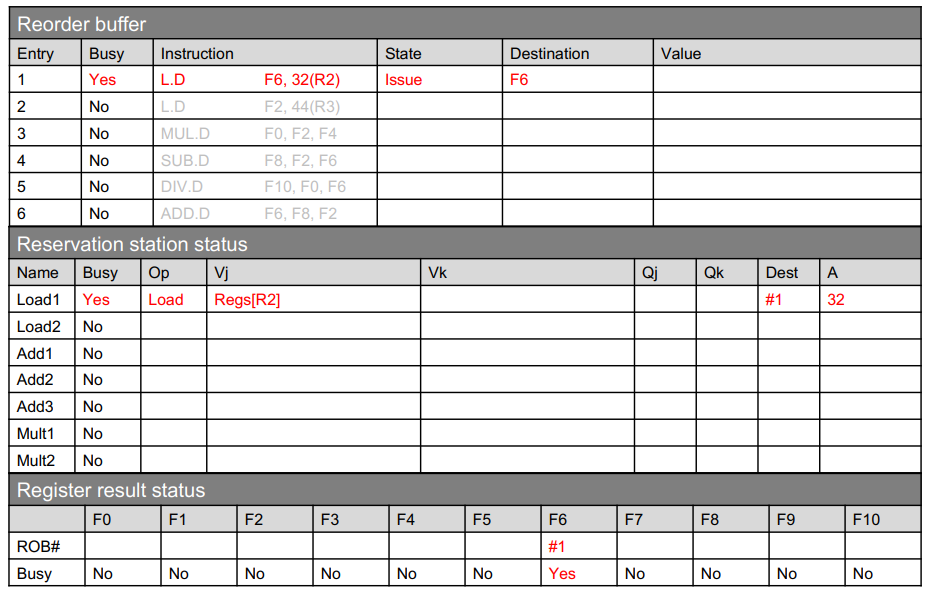

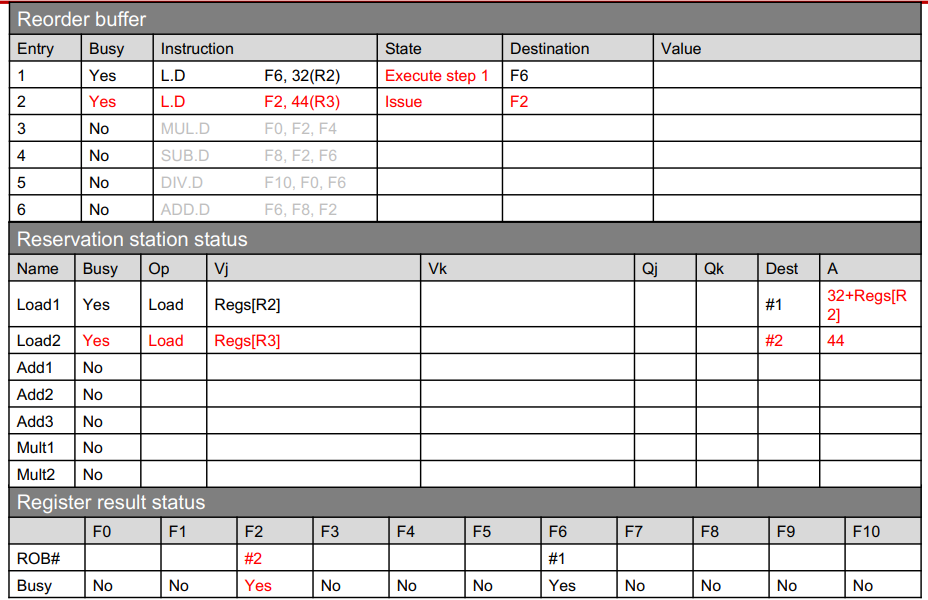

CC1:第一条Load发射

CC2:第一条Load完成地址计算;第二条Load发射

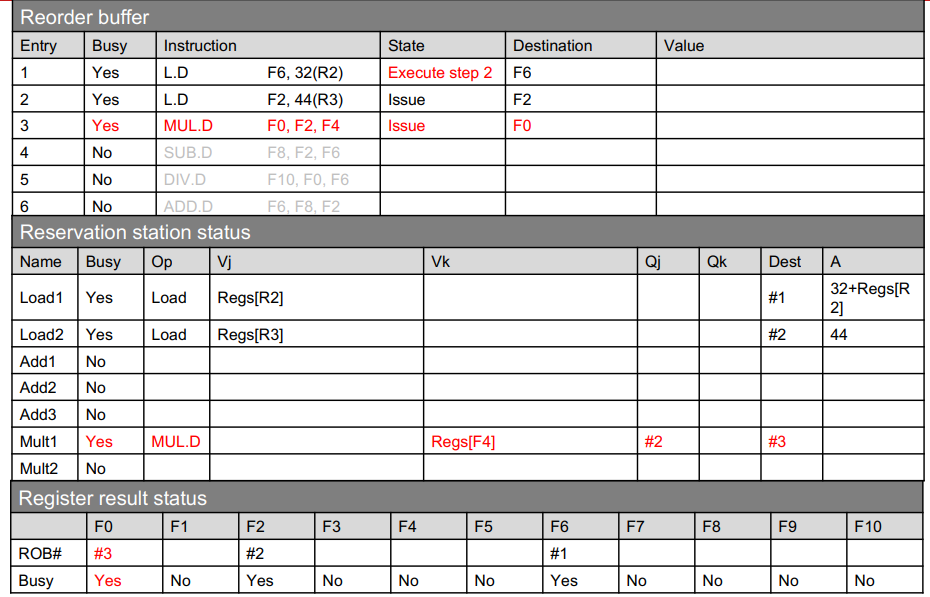

CC3:第一条Load执行完毕;第二条Load等待;MUL.D发射

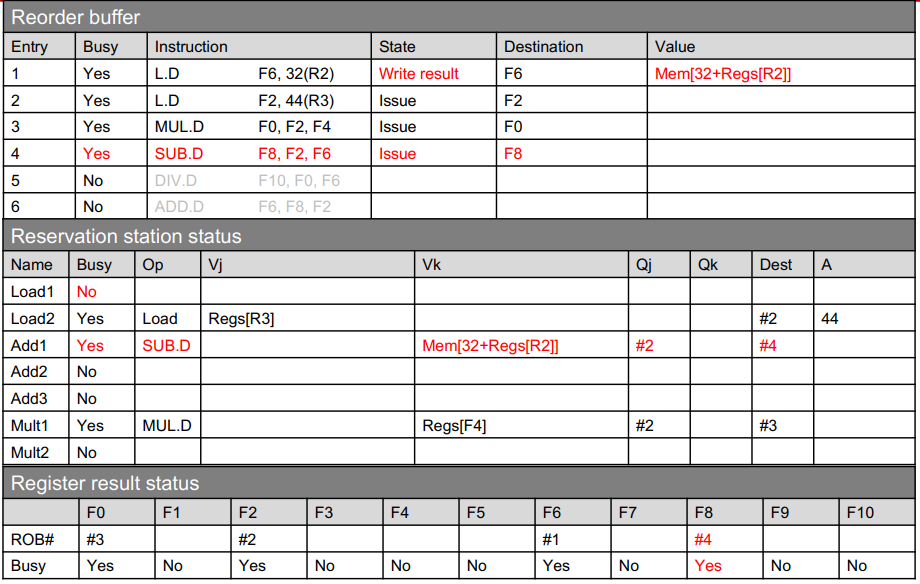

CC4:第一条Load写回完毕;第二条Load等待;MUL.D等待操作数;SUB.D发射

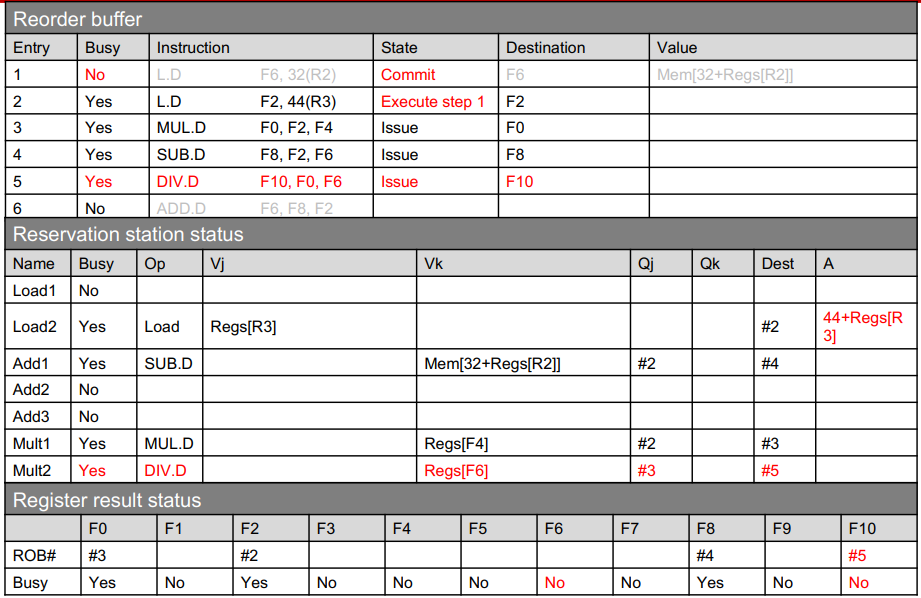

CC5:第一条Load提交;第二条Load完成地址计算;MUL.D/SUB.D等待操作数;DIV.D发射

CC6:第二条Load执行完毕;MUL.D/SUB.D/DIV.D等待操作数;ADD.D发射

CC7:第二条Load写回完毕;MUL.D/SUB.D就绪;DIV.D/ADD.D等待操作数

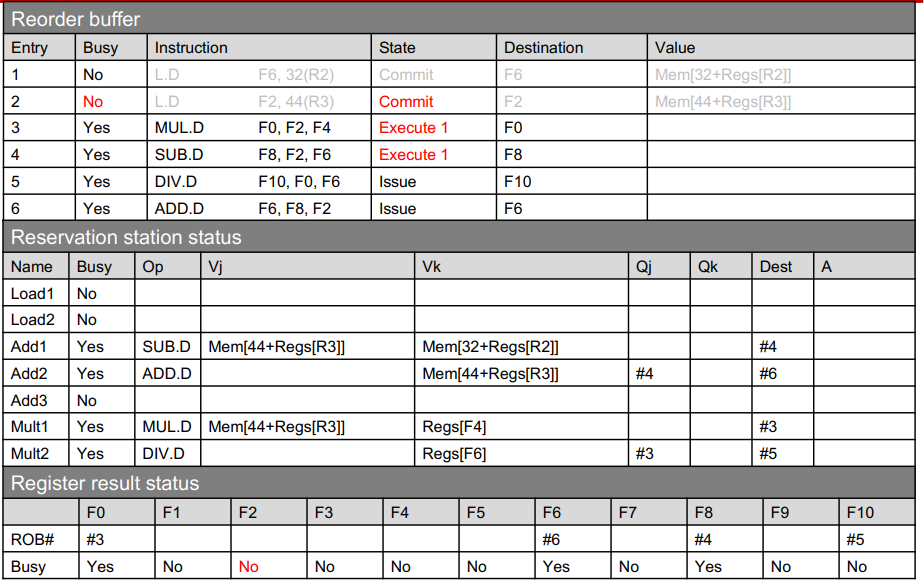

CC8:第二条Load提交;MUL.D/SUB.D执行完第一拍;DIV.D/ADD.D等待操作数

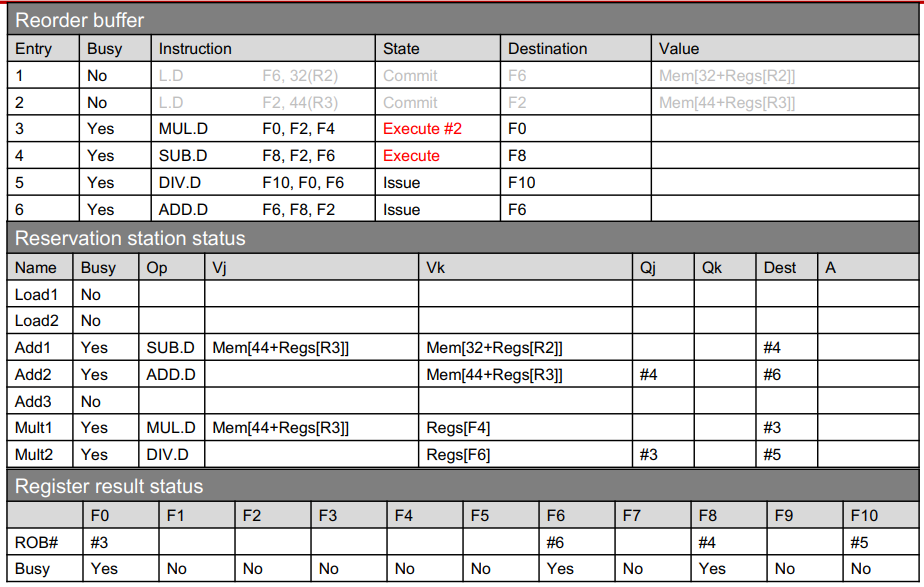

CC9:SUB.D执行完毕;MUL.D执行完第二拍;DIV.D/ADD.D等待操作数

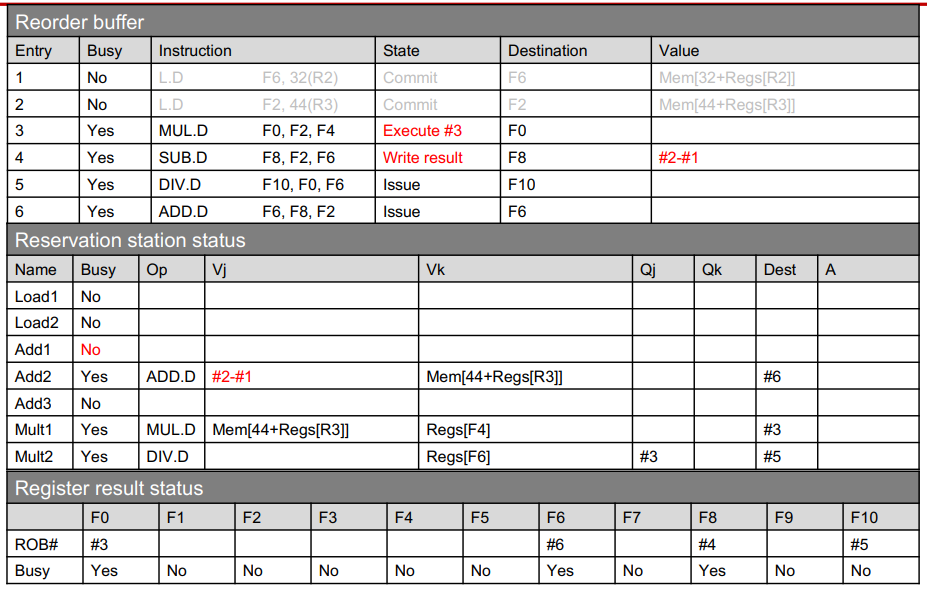

CC10:SUB.D写回完毕;MUL.D执行完第三拍;ADD.D就绪;DIV.D等待操作数

CC11:SUB.D等待提交;MUL.D执行完第四拍;ADD.D执行完第一拍;DIV.D等待操作数

CC12:ADD.D执行完毕;SUB.D等待提交;MUL.D执行完第五拍;DIV.D等待操作数

CC13:ADD.D写回完毕;MUL.D执行完毕;SUB.D等待提交;DIV.D等待操作数

CC14:MUL.D写回完毕;DIV.D就绪;SUB.D/ADD.D等待提交

CC15:MUL.D提交;DIV.D执行完毕第一拍;SUB.D/ADD.D等待提交

CC16:SUB.D提交;DIV.D执行完毕第二拍;ADD.D等待提交

CC26:DIV.D执行完毕;ADD.D等待提交

CC27:DIV.D写回完毕;ADD.D等待提交

CC28:DIV.D提交;ADD.D等待提交

CC29:ADD.D提交

ROB的折衷

- 优点 :

- 概念简单,支持精确异常

- 可以消除错误的依赖性

- 缺点:

- 需要访问重新排序缓冲区以获得尚未写入寄存器文件的结果 ,CAM 或间接会增加延迟和复杂性

- 其他解决方案旨在消除缺点

- History buffer

- Future file

- Checkpointing

文章来源:https://blog.csdn.net/Programmer_jzm/article/details/135508847

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- LUT预设.cube格式PR/达芬奇/FCP/剪映等视频电影调色预设LUTs

- 【vue】正则表达式限制input的输入:

- Linux学习教程(第十四章 Linux系统服务管理)二

- 生物批签发数据库<收载15W+条数据>

- MySQL的一些综合运用

- Neo4j CQL语法

- 异步非阻塞事件驱动架构的具体流程解析

- 两种经典的现货白银假突破类型

- logstack 日志技术栈-02-ELK 的缺点?loki 更轻量的解决方案?

- 64位AT&T汇编语言as汇编ld链接,执行报错Segmentation fault