「Verilog学习笔记」流水线乘法器

发布时间:2023年12月17日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

`timescale 1ns/1ns

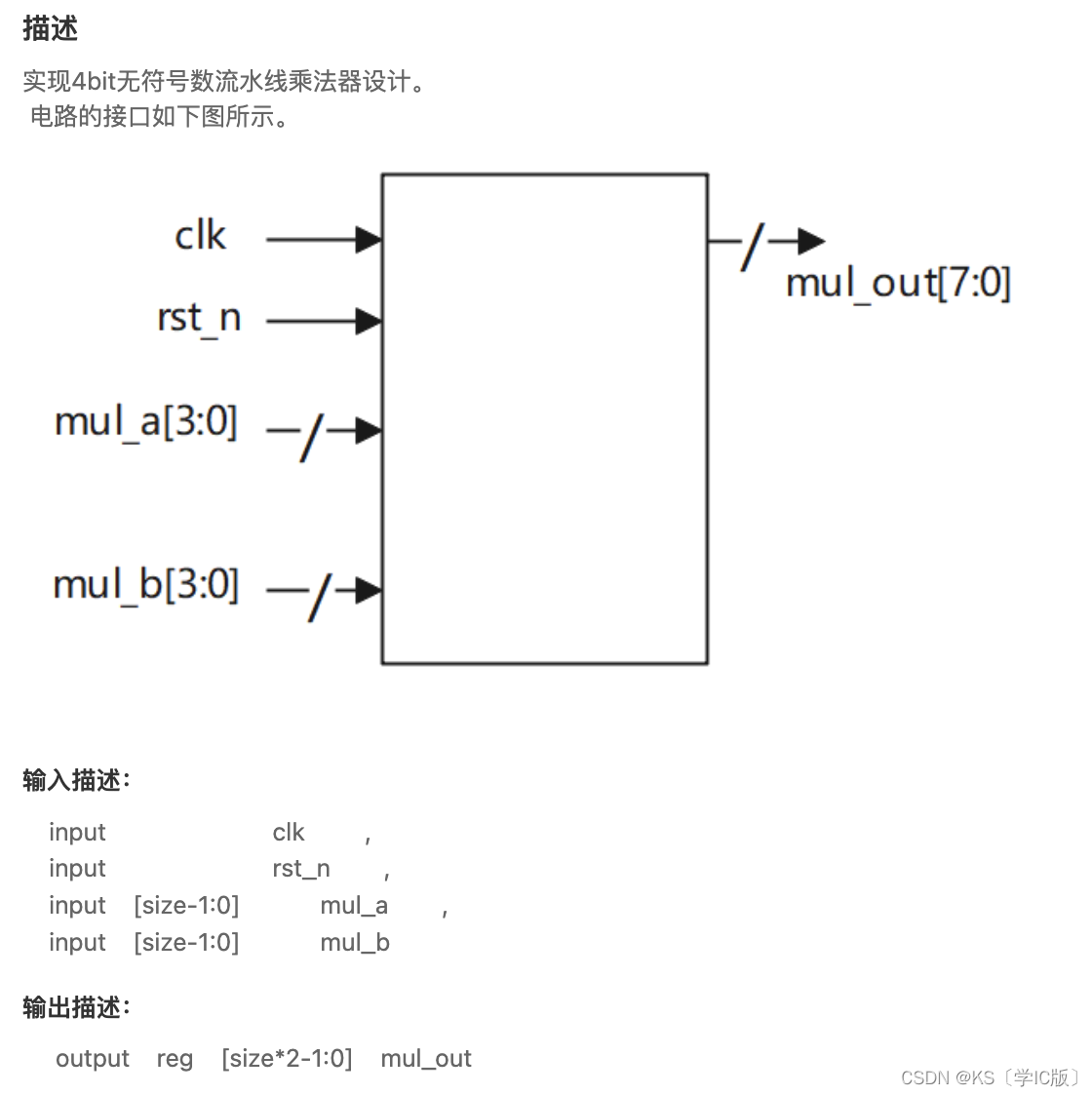

module multi_pipe#(

parameter size = 4

)(

input clk ,

input rst_n ,

input [size-1:0] mul_a ,

input [size-1:0] mul_b ,

output reg [size*2-1:0] mul_out

);

reg [7:0] sum01, sum23 ;

wire [7:0] t0, t1, t2, t3 ;

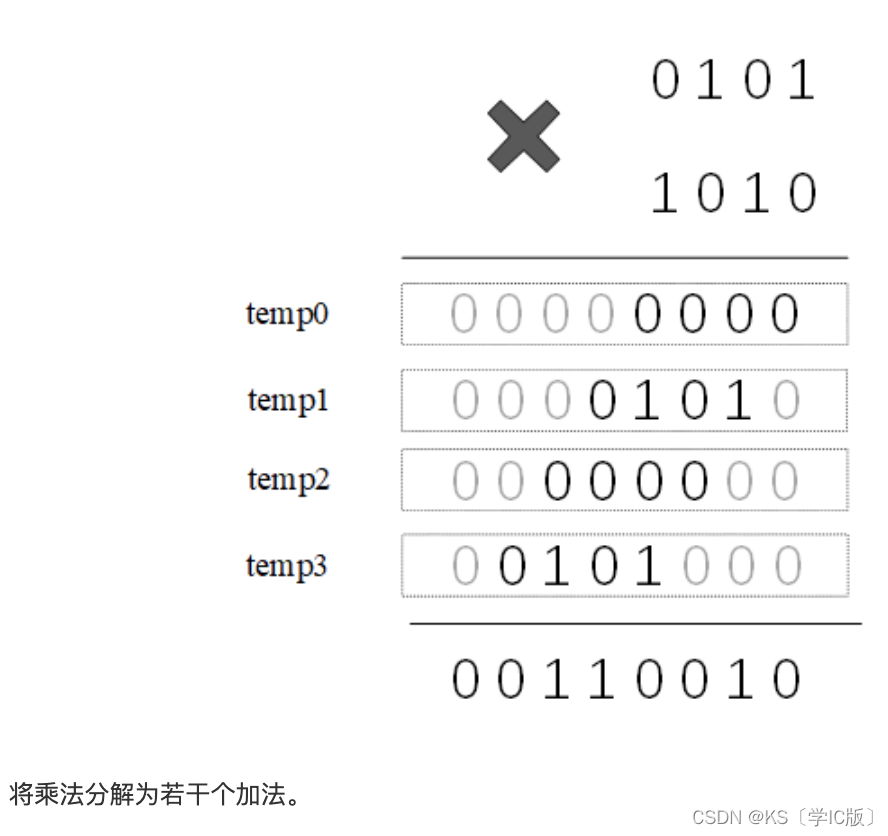

assign t0 = mul_b[0] ? {4'b0, mul_a} : 0 ;

assign t1 = mul_b[1] ? {3'b0, mul_a, 1'b0} : 0 ;

assign t2 = mul_b[2] ? {2'b0, mul_a, 2'b0} : 0 ;

assign t3 = mul_b[3] ? {1'b0, mul_a, 3'b0} : 0 ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) begin

sum01 <= 0 ;

sum23 <= 0 ;

mul_out <= 0 ;

end

else begin

sum01 <= t0 + t1 ;

sum23 <= t2 + t3 ;

mul_out <= sum01 + sum23 ;

end

end

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135046495

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!