FPGA设计与实战之时钟及时序简介1

发布时间:2023年12月18日

一、时钟定义

我们目前设计的电路以同步时序电路为主,时钟做为电路工作的基准而显得非常重要。

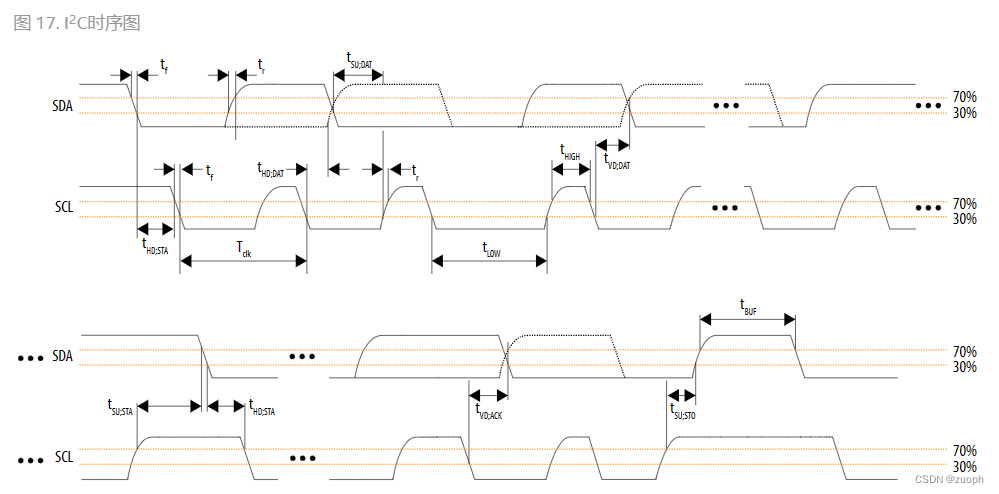

简单的接口电路比如I2C、SPI等,复杂一点接口比如Ethernet的MII、GMII等接口,它们都有一个或多个时钟信号。

那么什么是时钟信号?它有哪些特性和参数呢?

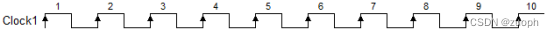

如上图所示,时钟信号简单而言是一种具有特定频率和确定占空比的周期性重复的数字信号。

时钟通常具有以下参数:

- 频率(周期):描述时钟重复周期;

- 占空比:时钟信号高电平占整个时钟周期的比值;

- 上升沿和下降沿:时钟信号边沿10%-90%间的时间;

- 时钟偏移(skew):描述时钟在不同芯片或芯片内部由于走线通道差异导致到达时间的差值;

- 时钟抖动(ji

文章来源:https://blog.csdn.net/zuoph/article/details/135003099

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- LabVIEW开发自动读取指针式仪表测试系统

- RK3568驱动指南|第十二篇 GPIO子系统-第131章 GPIO子系统API函数的引入

- PCL 点云半径查找

- UDS诊断(ISO14229-1) 22服务

- RS232转profinet网关扫码枪自由口与1500程序对比

- gitlab请求合并分支

- Goland如何进行Debug断点调试

- FindMy技术|CES展会上最新的Location Card钱包卡产品

- 2024年医院设备维修培训安排

- Mac卸载nodejs