DDR3信号概念--入门1

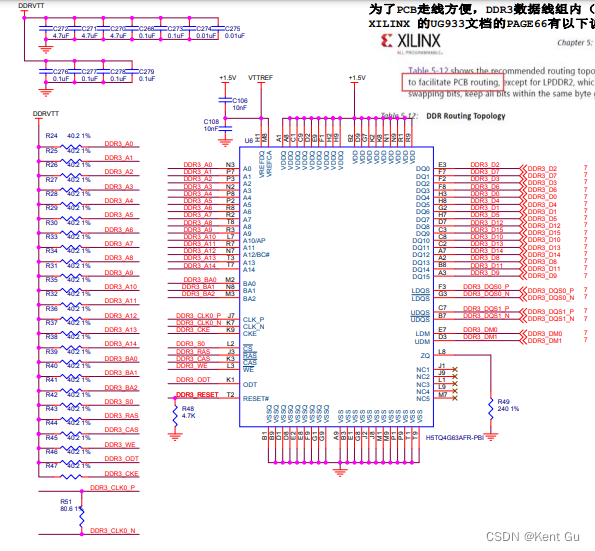

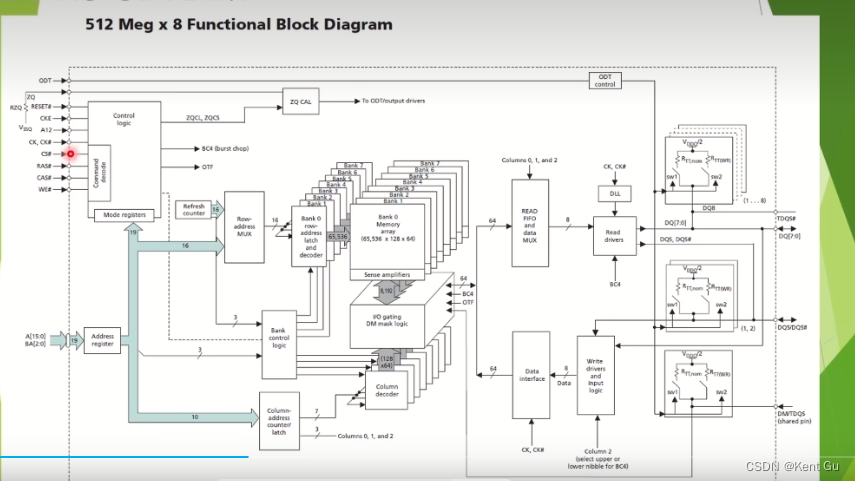

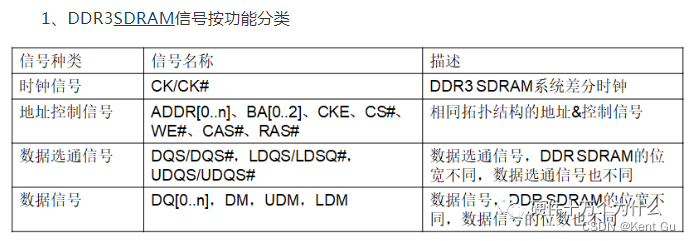

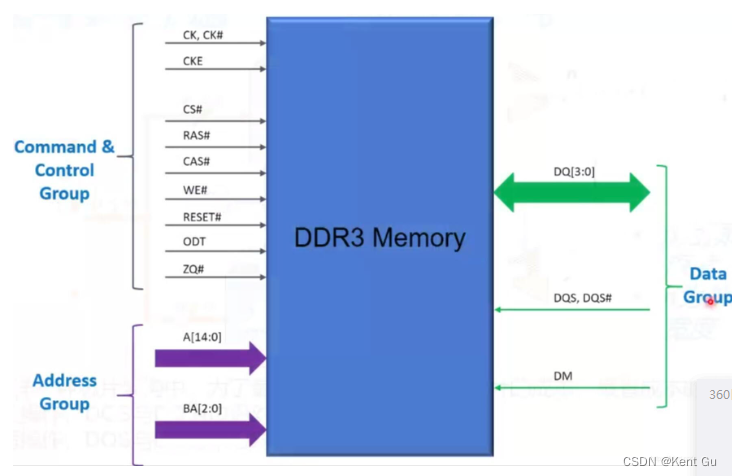

1. 信号分类 & 框架图

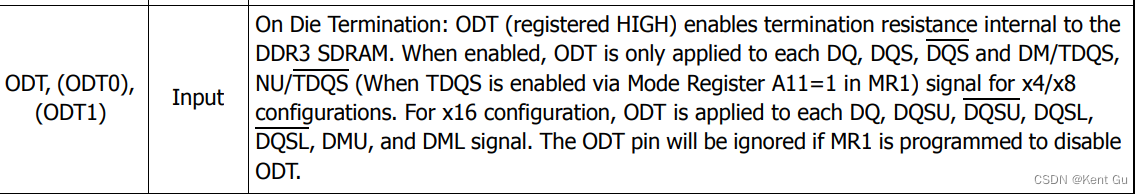

2. ODT ( On-DieTermination ,片内终结)

ODT 也是 DDR2 相对于 DDR1 的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸收掉,而不会在电路上形成反射, 造成对后面信号的影响。 顾名思义, ODT 就是将端接电阻移植到了芯片内部,主板上不再有端接电路。

假如数据长度长,更多的信号被阻抗匹配。

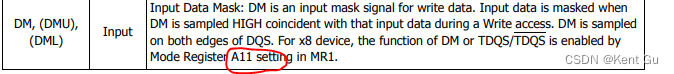

3. Data Mask(DM)/ TDQS,TDQS# 数据选通

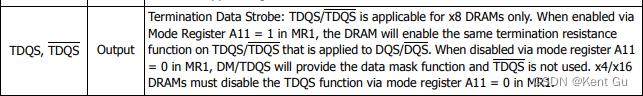

TDQS, termination Data Strobe

数据掩膜功能也称为部分写。只支持x8和x16配置。DM功能与TDQS功能共用相同的管脚。DM功能只用于写操作,应该说TDQS功能的优先级最高,如果使能了TDQS那么DM功能都被禁止。

如果禁止了TDQS功能,才允许DM和DBI发挥作用。但有点我不太明白,DBI好像没有和TDQS及DM共用管脚啊

X8 DDR3芯片用了TDQS功能,用于控制器(有两对DQS信号),控制器其中一对用于通信,另外一对是电阻匹配。

X4。用于控制器(有两对DQS信号),控制器分别接两个DDR芯片。

X16DDR3芯片用了DM功能,DM(UDM & LDM)选择高/低 Byte

如果是从内存中读取信号,那么主板北桥(内存控制器)根据内存发出的DQS来判断在什么时候接收读出来的数据。如果是写的话,就正好相反,内存根据北桥发出的DQS来触发数据的接收。

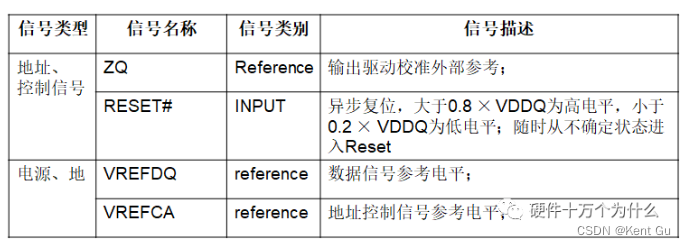

4. ZQ 校准

如下所示, ZQ 是DDR3一个新增的引脚,在这个引脚上接有一个 240 欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎( ODCE ,On-DieCalibrationEngine )来自动校验数据输出驱动器导通电阻与 ODT 的终结电阻值。 当系统发出这一指令之后, 将用相应的时钟周期 (在加电与初始化之后用 512 个时钟周期,在退出自刷新操作后用 256 时钟周期、在其他情况下用 64个时钟周期)对导通电阻和 ODT 电阻进行重新校准。

ODT是终端匹配,那就是要在你的信号线终端上拉一个电阻,但是这个内部电阻随着温度会有些细微的变化,为了保证信号被准确的进行终端匹配,就需要ZQ了,ZQ的作用就是使用你外面连接的,高精度240R电阻来对这个内部的电阻进行校准。

5.专有名词索引表

https://blog.csdn.net/Rspate/article/details/107859785

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!