第三课:寄存器与内存、中央处理器(CPU)、指令和程序及高级 CPU 设计

第三课:寄存器与内存、中央处理器(CPU)、指令和程序及高级 CPU 设计

各位小伙伴想要博客相关资料的话,关注公众号:chuanyeTry即可领取相关资料!

第六章:寄存器与内存

课程导入

- 当玩游戏、写文档时如果断电,进度会丢失,这是为什么?

– 这是电脑使用的是 RAM(随机存取存储器),俗称内存,内存只能在通电情况下存储数据。

– 本节课程将讲述内存的工作原理。

1、概念梳理

锁存器:利用 AND、OR、NOT 逻辑门,实现存储 1 位数字的器件。

寄存器:1 组并排的锁存器。

矩阵:以矩阵的方式来存放锁存器的组合件,n* n 门锁矩阵可存放 n^2 个锁存器,但同一时间只能写入/读取 1 个数字。(早期为 16*16 矩阵)。

位址:锁存器在矩阵中的行数与列数。eg.12 行 8 列。

多路复用器:一组电线,输入 2 进制的行址&列址,可启用矩阵中某个锁存器。

内存(RAM):随机存取存储器,由一系列矩阵以及电路组成的器件,可根据地址来写入、读取数据。类似于人类的短期记忆,记录当前在做什么事情。

2、锁存器

作用:存储 1 位数字。

图示:

3、门锁

锁存器需要同时输入 2 个数字,不太方便。

为了使用更方便,只用 1 根电线控制数据输入,发展了门锁这个器件。另外,用另一根电线来控制整个结构的开关。(和复位作用不同)

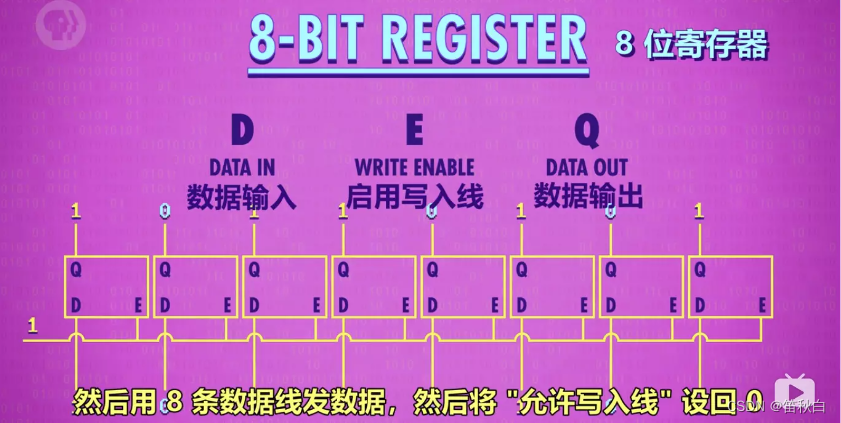

4、寄存器

作用:并排使用门锁,存储多位数字

图示:

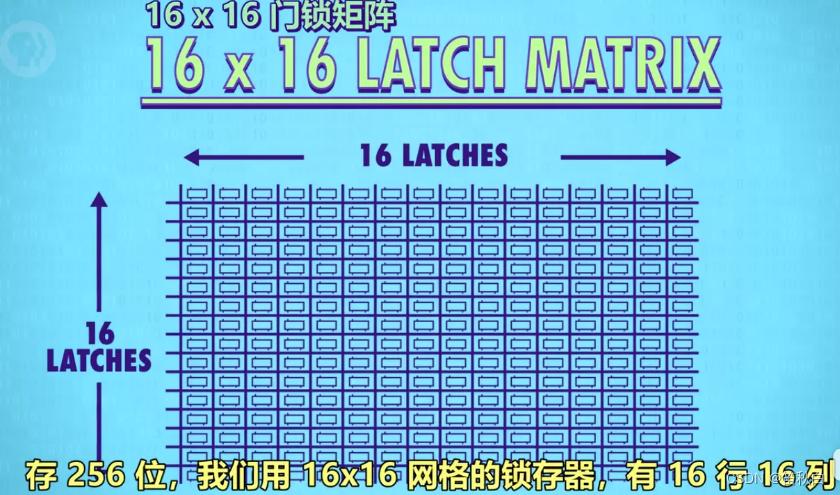

5、门锁矩阵

作用:n* n 的矩阵有 n^ 2 个位址,则可以存储 n^2 个数。但 1 个矩阵只可记录 1 位数字,n 个矩阵组合在一起,才可记录 n 位数。如 1 个 8 位数,会按位数分成 8 个数,分别存储在 8 个矩阵的同一个位址中。

8 个矩阵,则可以记录 256 个 8 位数字。

通俗理解:16* 16 的门锁矩阵,可理解为 1 个公寓,1 个公寓 256 个房间。

8 个门锁矩阵并排放,则有了 8 个公寓。

规定每一个公寓同一个编号的房间,都有一样的标记(地址),共同组成 8 位数字。

那么 8 个公寓就能存 (8*256 / 8)个数字。

原因:16*16 的门锁矩阵虽然有 256 个位置,但每次只能存/取其中 1 个位置的数字。因此,要表示 8 位数字,就需要同时调用 8 个门锁矩阵。

图示:

使用方法:在多路复用器中输入位址,x 行 x 列(2 进制),即可点亮 x 行 x 列的锁存器。

举例:

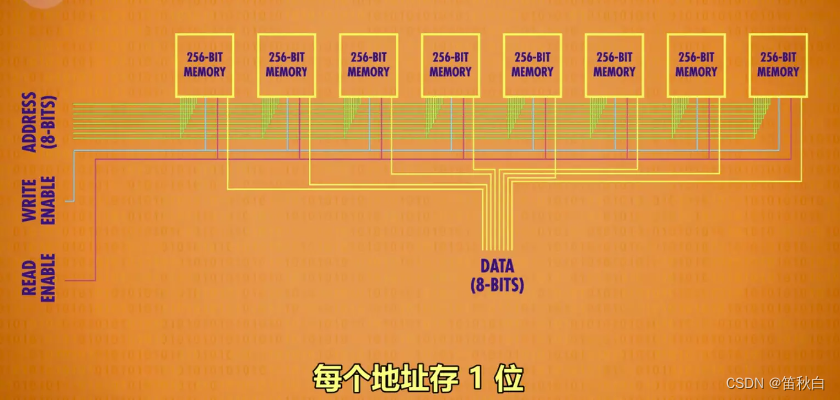

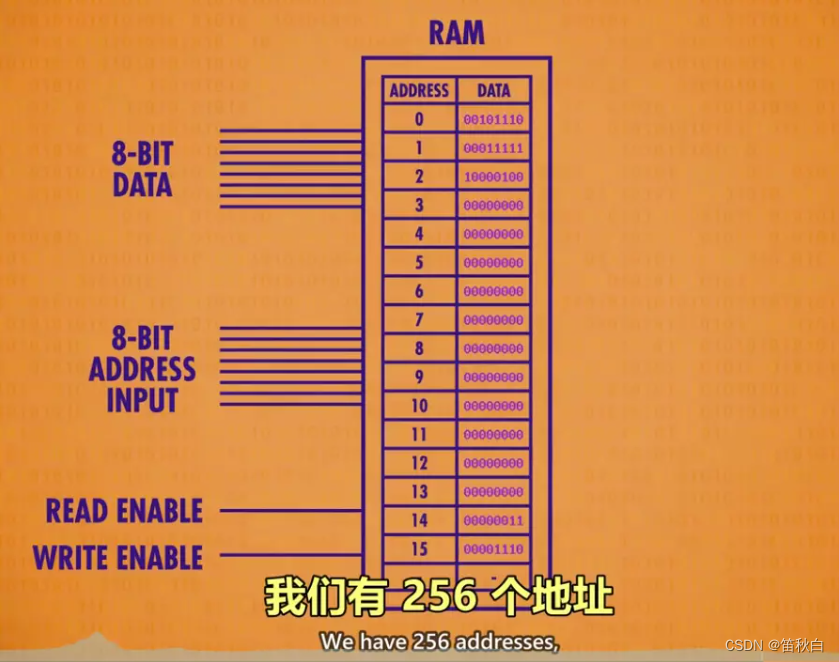

5、内存

粗略定义:将一堆独立的存储模块和电路看做 1 个单元,组成内存方块,n 个内存方块组成内存模块。在一个电路板上所有的内存方块统称为内存(RAM)。

图示:

第七章:中央处理器(CPU)

1、概念梳理

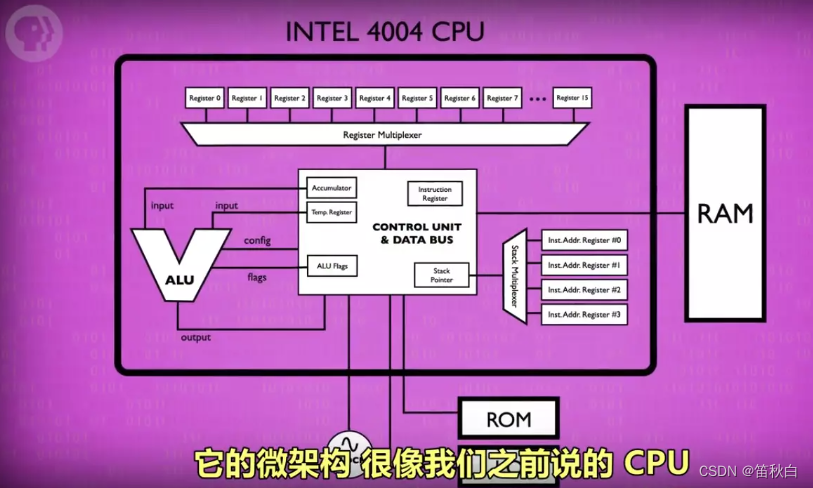

- CPU(Central Processing Unit):中央处理单元,负责执行程序。通常由寄存器/控制单元/ALU/时钟组成。与 RAM 配合,执行计算机程序。CPU 和 RAM 之间用“地址线”、“数据线”和“允许读/写线”进行通信。

– 指令:指示计算机要做什么,多条指令共同组成程序。如数学指令,内存指令。 - 时钟:负责管理 CPU 运行的节奏,以精确地间隔,触发电信号,控制单元用这个信号,推动 CPU 的内部操作。

– 时钟速度:CPU 执行“取指令→解码→执行”中每一步的速度叫做“时钟速度”,单位赫兹Hz,表示频率。

– 超频:修改时钟速度,加快 CPU 的速度,超频过多会让 CPU 过热或产生乱码。

– 降频:降低时钟速度,达到省电的效果,对笔记本/手机很重要。 - 微体系框架:以高层次视角看计算机,如当我们用一条线链接 2 个组件时,这条线只是所有必须线路的抽象。

2、CPU 工作原理

1)必要组件

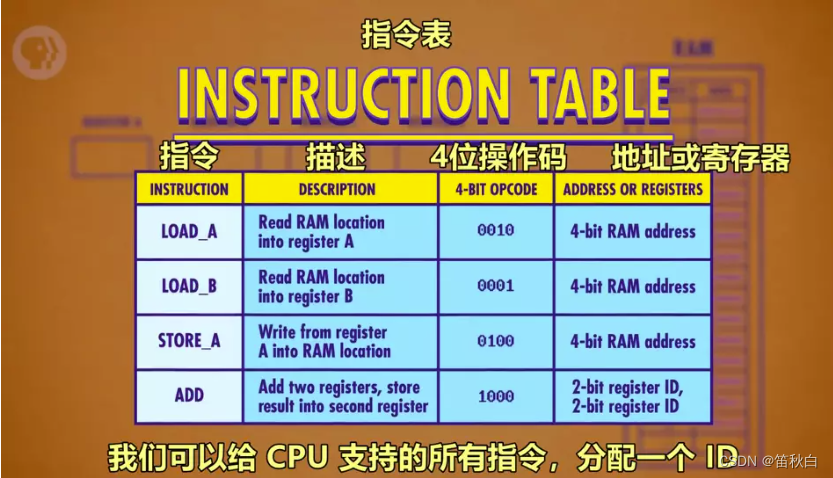

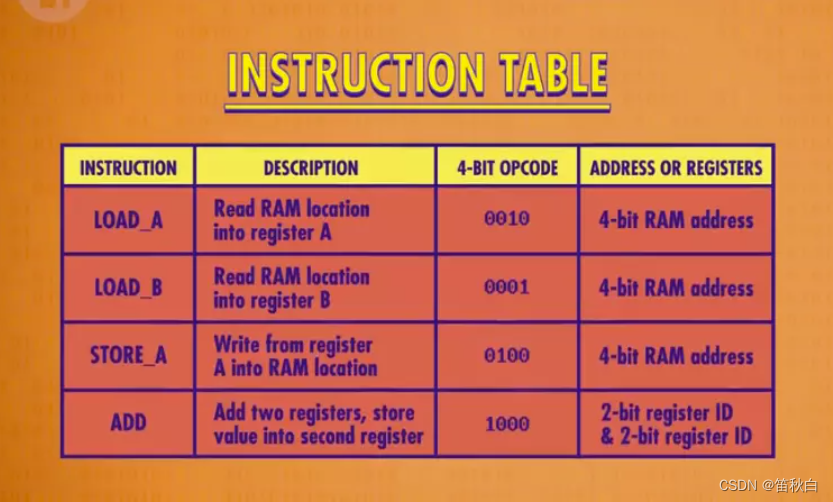

- 指令表:给 CPU 支持的所有指令分配 ID

- 控制单元:像指挥部,有序的控制指令的读取、运行与写入。

– 指令地址寄存器:类似于银行取号。该器件只按顺序通报地址,让 RAM 按顺序将指令交给指令寄存器。

– 指令寄存器:存储具体的指令代码。

2)过程

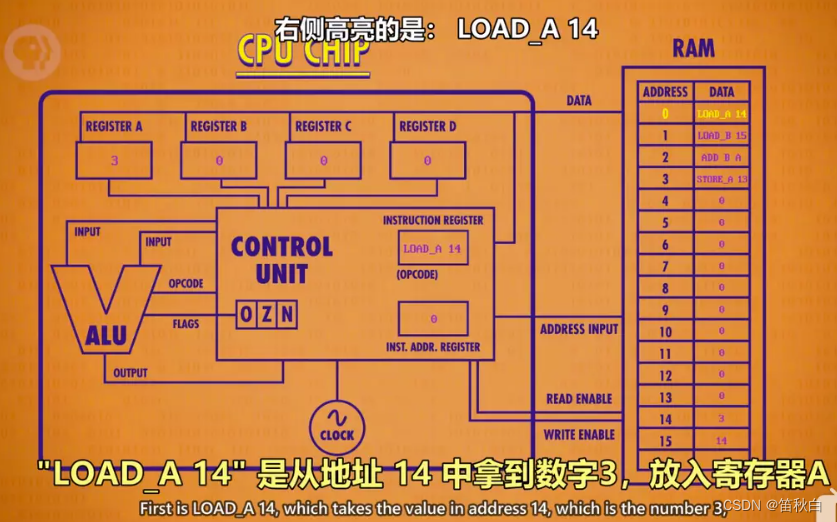

- 取指令:指令地址寄存器发地址给 RAM→RAM发该地址内的数据给指令寄存器→指令寄存器接受数据

- 解码:指令寄存器根据数据发送指令给控制单元 →控制单元解码(逻辑门确认操作码)

- 执行阶段:控制单元执行指令(→涉及计算时→调用所需寄存器→传输入&操作码给ALU执行)→调用RAM特定地址的数据→RAM将结果传入寄存器→指令地址寄存器+1

3)图示

第一个 CPU

第八章:指令和程序

1、概念梳理

- 指令:指示计算机要做什么的代码(机器码),多条指令共同组成程序。如数学指令,内存指令。

– 注:指令和数据都是存在同一个内存里的。 - 指令集:记录指令名称、用法、操作码以及所需 RAM 地址位数的表格。

2、指令的执行

- 原则:

– RAM 每一个地址中,都存放 0 或 1 个数据。

– 特定的数字组合,就表示为一个指令,否则表示一个值。 - LOAD 指令:

– 计算机会按地址的顺序,读取 RAM 中所记录的指令/数据。

– 计算机接受到指令后,如 LOAD_A,则通过数据线将数据传至寄存器 A。

- ADD 指令:

– ADD B A 指令告诉 ALU,把寄存器 B 和寄存器中的数字加起来,存到寄存器 A 中。 - JUMP 指令:

– 遇到 JUMP 指令,程序会跳转至对应的 RAM 地址读取数据。

– JUMP 指令可以有条件跳转(如 JUMP-negative),也可以无条件跳转。

3、计算机指令长度

由于早期计算机每个字只有 8 位,指令只占 4 位,意味着只能有 16 个指令,这远远不够。

现代计算机有两种方式解决指令不够用的问题:

最直接的是用更多位来表示指令,如 32 位或 64 位。

采用“可变指令长度”,令不同的指令的长度不同,尽量节约位数。

– 假设 1 个字为 16 位,如果某指令不需要操作内存,则可以省去寻址的位数。

– 该情况下,部分指令后面需要跟数据,如 JUMP,称为立即值。

第九章:高级 CPU 设计

概念梳理

- 缓存:在 CPU 中的小块 RAM,用于存储批量指令。

– 缓存命中:想要的数据已经在缓存里

– 缓存未命中:想要的数据不在缓存里脏位:缓存里每块空间,有个特殊标记,叫

– 脏位,用于检测缓存内的数据是否与 RAM 一致。 - 多核处理器:一个 CPU 芯片中,有多个独立处理单元。

1、现代 CPU 如何提升性能

早期通过加快晶体管速度,来提升 CPU 速度。但很快该方法到达了极限。

后来给 CPU 设计了专门除法电路+其他电路来做复杂操作:如游戏,视频解码。

2、缓存

为了不让 CPU 空等数据,在 CPU 内部设置了一小块内存,称为缓存,让 RAM 可以一次传输一批数据到 CPU 中。(不加缓存,CPU 没位置放大量数据)

缓存也可以当临时空间,存一些中间值,适合长/复杂的运算。

脏位:储存在缓存中与 RAM 不一致的数据。

空等原因:从 RAM 到 CPU 的数据传输有延迟(要通过总线,RAM 还要时间找地址、取数据、配置、输出数据)。

3、缓存同步

缓存同步一般发生在 CPU 缓存已满,但 CPU 仍需往缓存内输入数据。此时,被标记为脏位的数据会优先传输回 RAM,腾出位置以防被覆盖,导致计算结果有误。

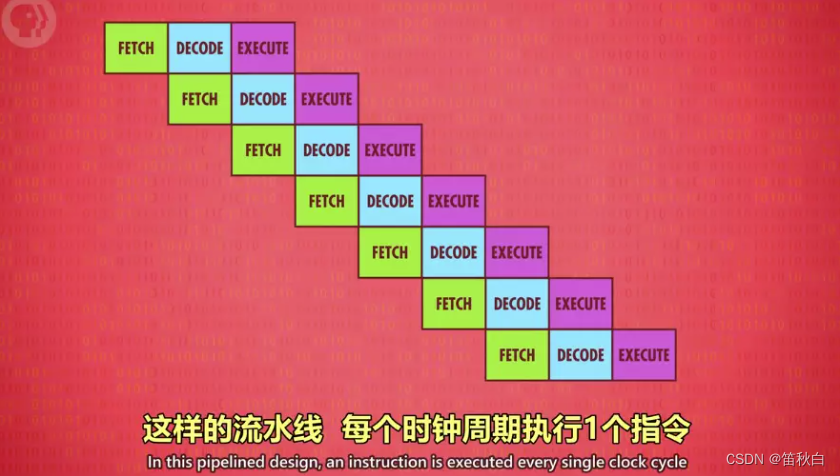

4、指令流水线

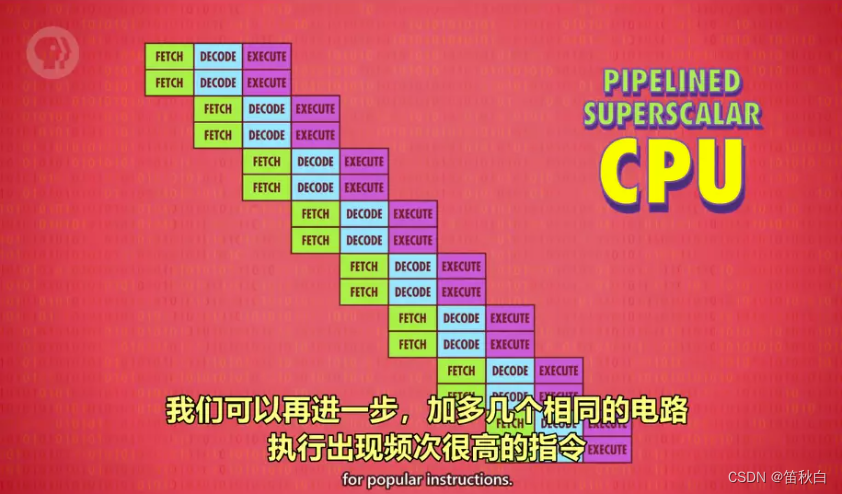

作用:让取址→解码→执行三个步骤同时进行。并行执行指令,提升CPU性能。

原本需要 3 个时钟周期执行 1 个指令,现在只需要 1 个时钟周期。

设计难点:数据具有依赖性 跳转程序

数据依赖性解决方法:乱序运行、预测分支(高端 CPU)

5、一次性处理多条指令

6、同时运行多个指令流(多核 CPU)

多核处理器:一个 CPU 芯片中,有多个独立处理单元。但因为它们整合紧密,可以共享一些资源。

7、超级计算机(多个 CPU)

在一台计算机中,用无数个 CPU,做怪兽级的复杂运算,如模拟宇宙形成。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- ssmpython在线学习与考试系统(开题+源码)

- AutoSAR(基础入门篇)3.2-Autosar中RTE的Ports【S/R】与【C/S】

- Power Apps 学习笔记 - IOrganizationService Interface

- nbuntu 18.04 终端打开后无内容

- d2l动手学深度学习】 Lesson 13 Dropout层 老板随机丢掉一些做项目的程序员?,项目的效果会更好!(bushi)

- 写回(write back)与 写分配(write allocate)的差异

- 二分类任务、多分类任务、多标签分类任务、回归任务的代码实现上的区别和联系

- uniapp中uview组件库中丰富的LineProgress 线形进度条 的使用方法

- Linux _ apache服务器部署 不同域名—访问不同网站(多网站)

- 动态画出300以内的质数曲线图