转 [Verilog] Quartus II 13.0下载安装和HelloWorld

主页: 元存储博客

转载自

https://blog.csdn.net/qq_38113006/article/details/121569176

文章目录

一、前言

Quartus II是Altera的FPGA设计工具,

二、安装包下载

百度云链接地址:https://pan.baidu.com/s/1VtDVKaiUDgbZI1vICS9jlw 提取码:ac9r

其他相关资料下载:http://www.corecourse.cn/forum.php?mod=viewthread&tid=27539

三、软件安装

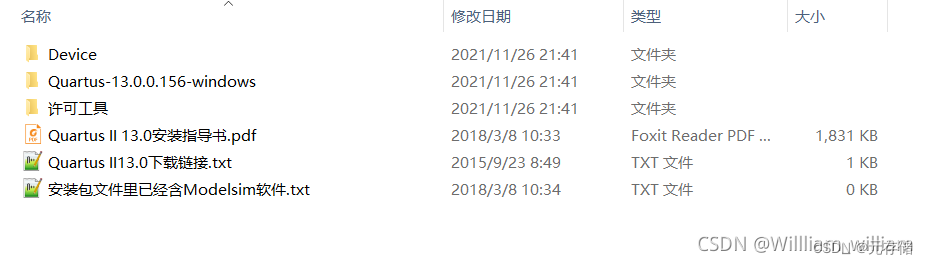

安装包下载好后解压

点击进入【Quartus-13.0.0.156-windows】文件夹中,其中包含了开发 FPGA 所需的所有工具, 包括 Quartus

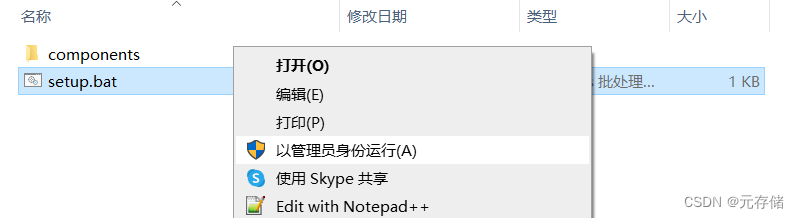

II13.0 主程序、 仿真工具 modelsim-altera, Dspbuilder 以及帮助文档。然后点击【setup.bat】右键选择【以管理员身份运行】

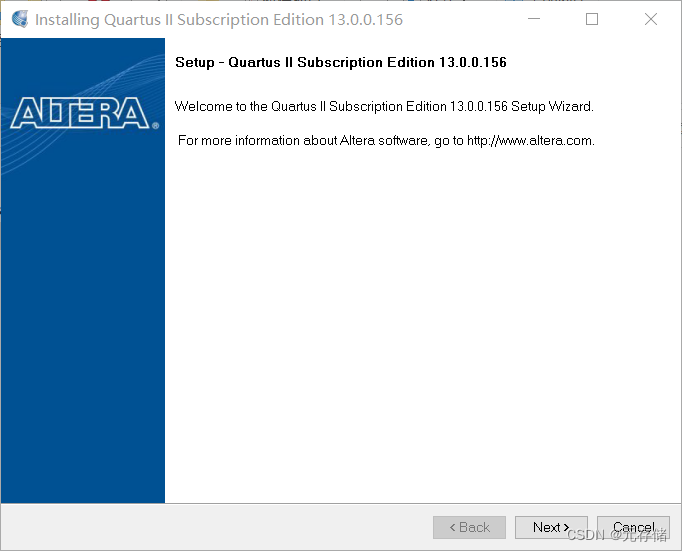

等待一会后会出现如下安装界面,点击【Next】即可

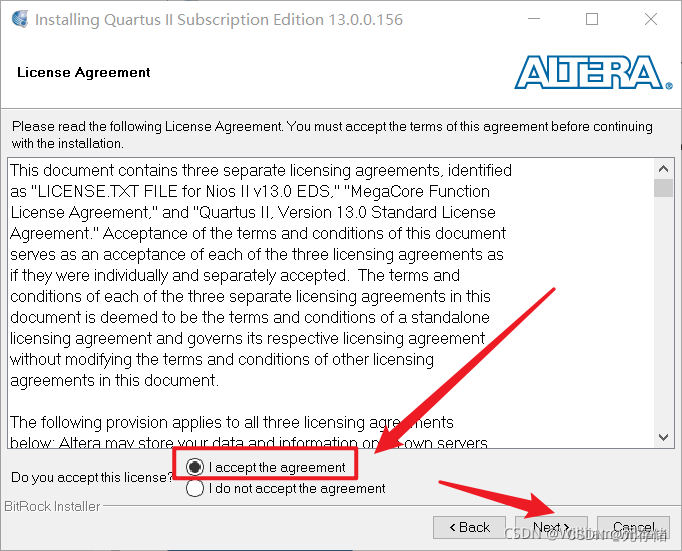

然后勾选【I accept the agreement】后依然点击【Next】

接下来选择安装路径,默认安装在C盘,按照自己的习惯我安装在D盘

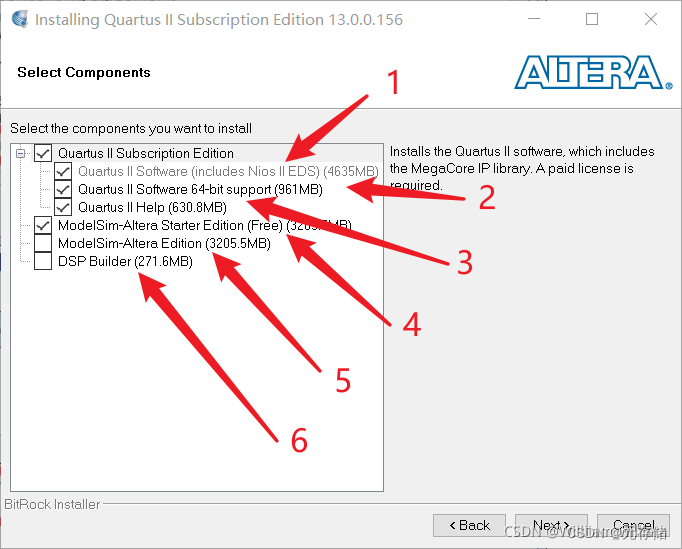

接下来选择安装的内容,第 1 项为 quartus 软件主包,为必装选项; 第 2 项为 quartus 软件 64 位系统支持包, 64 位系统需要安装此包,第 3 项为 quartus的帮助选项,建议安装。 第 4 项为 modelsim–altera 的初学者版本,基础的学习和仿真安装初学者版本即可完全满足条件,就不需要选择安装第 5 项了, 且第 5 项使用需要 license,没必要安装。 第 6 项为 dspbuilder,需要和 matlab 2012b 或更高版本配合使用,没有需求不用安装。勾选完成后,就可以点击 next 直接运行下一步了。

接下来是对安装选项的一个汇总报告,直接点击 【next】 即可开始安装,

接下来等待安装,比较漫长,可能需要 几十分钟的时间。

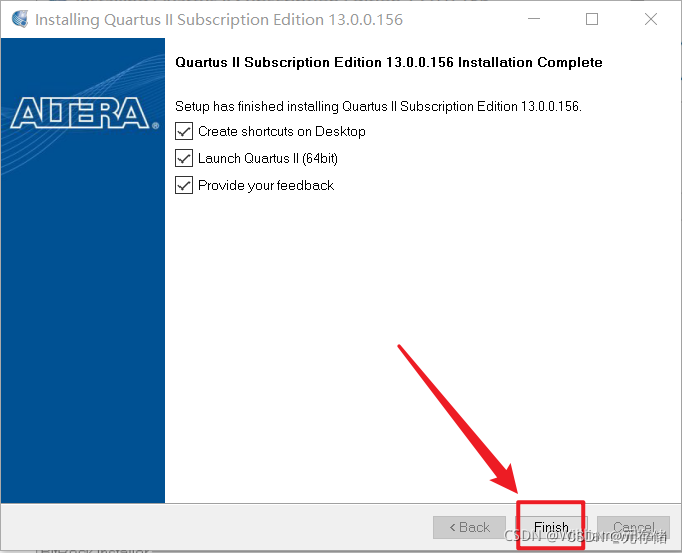

安装完成后点击【finish】即可

四、运行软件

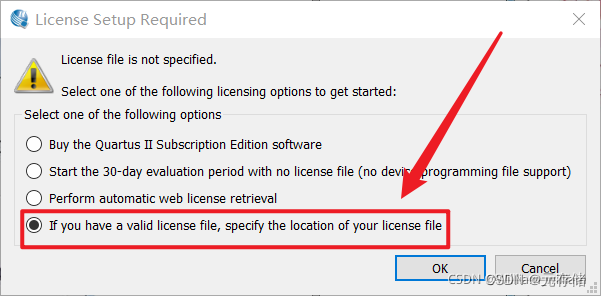

安装完后会自动打开软件,如果没有自动打开,从开始菜单或桌面上找到 Quartus II13.0 软件打开即可, 首次运行,会弹出以下界面, 提示我们安装 license。这里我们选择最后一项, 然后点击【OK】进入下一个页面。

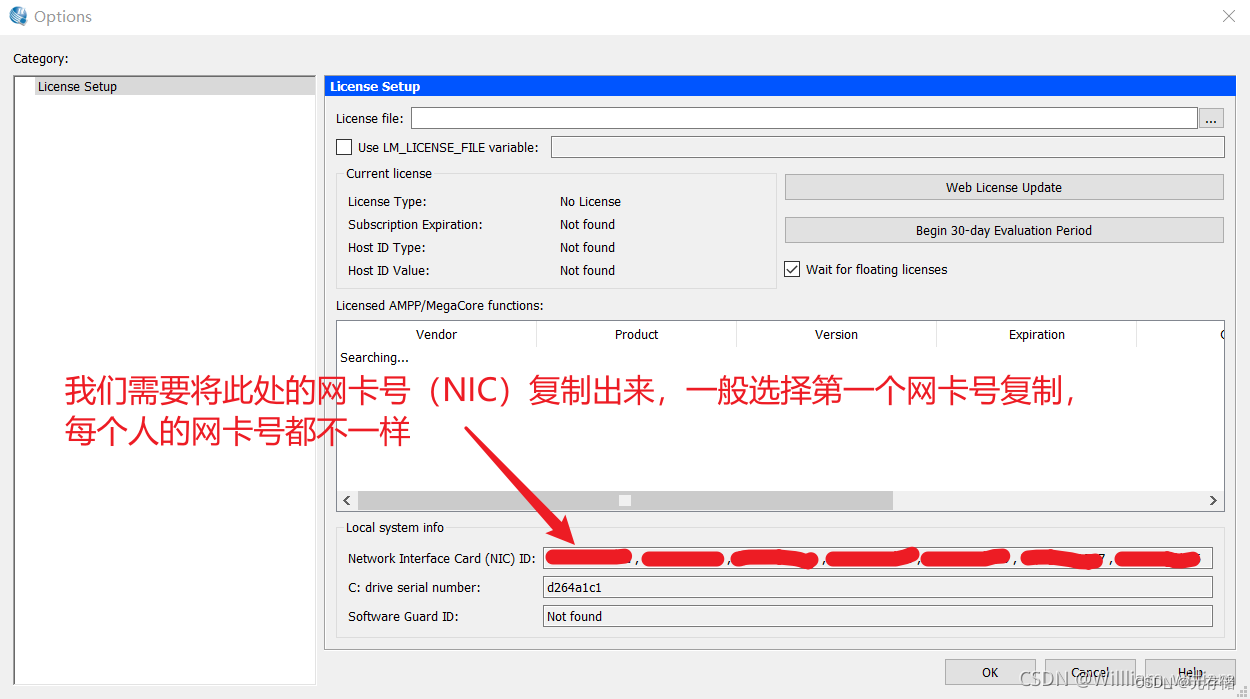

接下来跳出如下窗口,我们复制网卡号,然后点击【Cancel】关闭即可,然后将 quartus 主程序一并关闭。如果没有跳出,则在 Quartus II 中依次点击【Tools】 ->【License Setup】 来打开以下窗口。

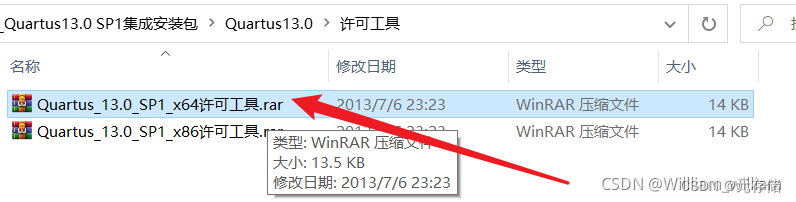

然后回到安装包所在的目录,进入【许可工具】目录,我的是64位系统,将【Quartus_13.0_SP1_x64许可工具】解压出来

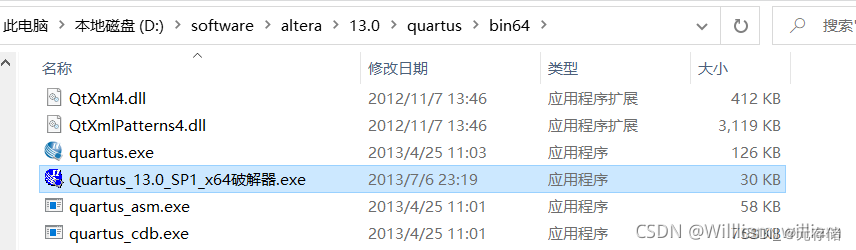

然后将其复制粘贴到你软件安装目录的 bin64 文件夹下, 如我的对应就是D:\software\altera\13.0\quartus\bin64。

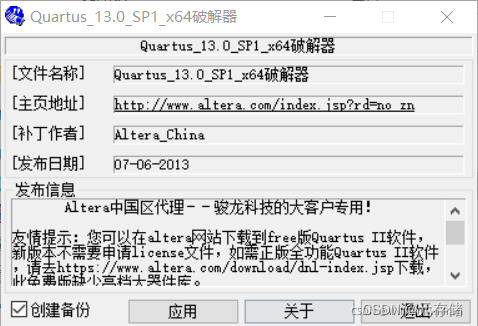

接下来选中它右键,选择以管理员身份运行, 则会出现以下界面:

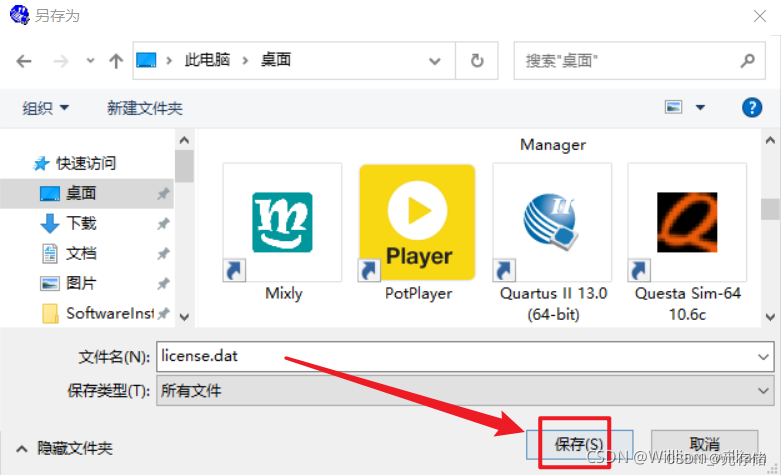

然后我们点击应用,就会弹出如下所示的界面,即会生成一个 licens.dat 的文件,要求我们保存,我们先将其保存在桌面上。保存完成以后, 就可以关闭该工具了。

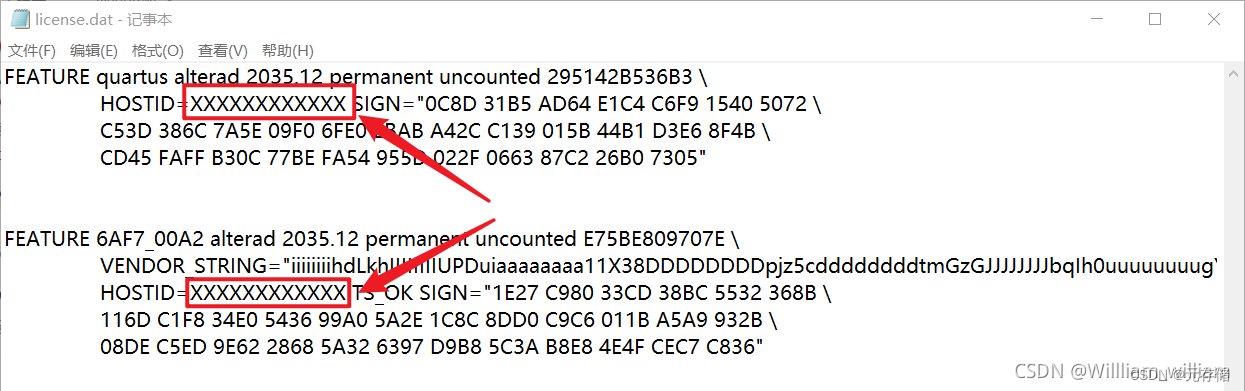

接下来,我们需要对刚刚生成的 license.dat 文件进行修改,找到先前复制的网卡号(NIC ID),将此 license 中的所有“XXXXXXXXXXXX”都用你的网卡号替换,然后保存此文件。

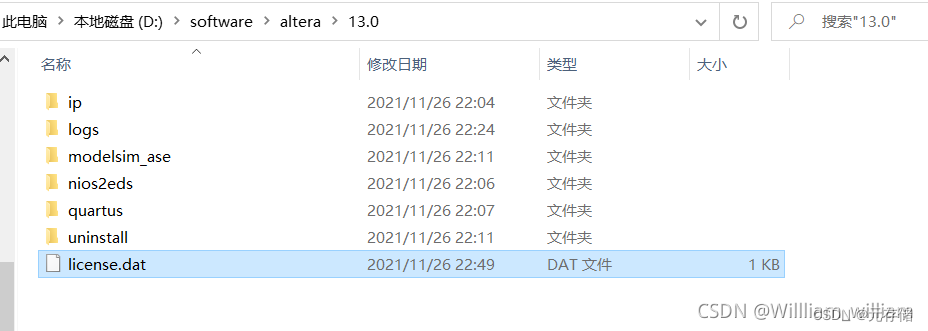

然后将其复制到一个不易被误删的文件夹下,一般选择保存在软件安装目录下,这里即【D:\software\altera\13.0】文件夹下。

(注意,这个地方一定要注意!!!!! 该路径千万不能再向下了,否则软件将不能正常识别 license)

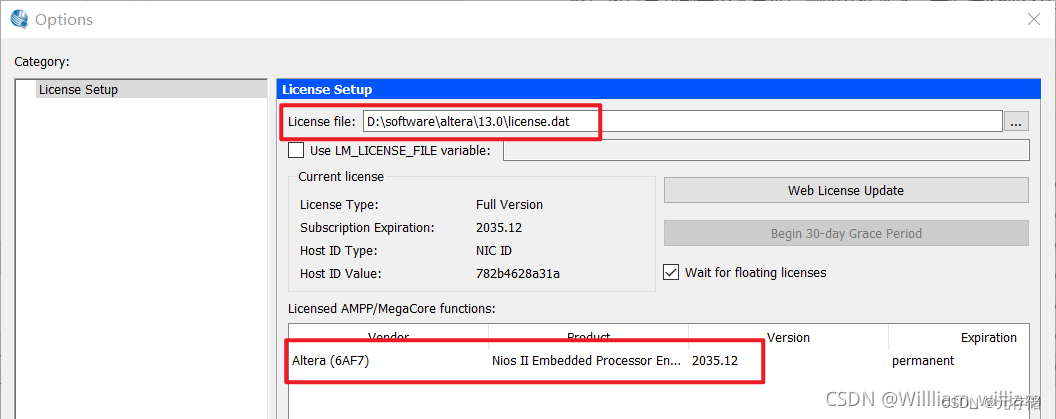

然后再次运行 Quartus II 软件, 在弹出的页面中接着再次选择最后一项,点击OK,在打开的页面中,将 license file 指向你刚刚保存好的 license.dat,当出现图中所示的内容,即表明破解成功了。

五、安装器件库

安装器件库需要关闭Quartus II 软件,然后回到安装包的 Device 文件夹下,运行 DeviceInstall-13.0.0.156.exe 文件,

点击 next 即可,

在接下来弹出的页面中,为选择器件安装目录,这里必须和软件安装目录一致,所以这里修改为 D:\software\altera\13.0,

将【Cyclone, Cyclone II/III/IV】勾选即可,然后点击【Next】

同样点击【Next】

等待其安装完成,安装完成后点击【Finish】即可。

六、新建Hello工程

打开安装好的 Quartus II 软件,点击【File】->【New project Wizard】来新建一个工程

直接单击 Next 即可,

选择新建工程所在路径、设置工程命名以及顶层设计实体名称。在输入顶层设计实体时默认与工程名称一致,此处可根据具体情况来自行修改, 如下图所示。

没有已有的设计文件需要添加, 直接点击 Next,

选择器件,随便选择一个即可,这里我选择Cyclone IV E 系列的EP4CE10F17C8,然后点击【Next】

这里将仿真工具设置为 ModelsimAltera ,语言选择 Verilog HDL,其他选项可暂时不做处理,然后点击【Next】

点击【Finish】即可

六、新建设计

单击 【File】->【New】,弹出如图选择框,选择 Design Files 中的 【Verilog HDL File】,然后点击【OK】

输入代码如下所示,然后以hello.v 命名保存到工程目录下

然后单击工具栏中的 Start Analysis & Synthesis 来进行分析和综合,

分析综合成功后点击【RTL Viewer】

可以看到为一个二选一多路选择器

七、功能仿真

新建如下所示hello_tb.v 文件保存到工程目录下

单击标题栏的 Assignments→Settings→Simulation,选中 Compile test bench,单击 Test Benches 后点击 OK。

点击 New, 弹出如图 所示的 Test Bench 设置文件对话框,找到已经编写好的激励文件,单击 Add。在 Test bench name 中填写对应的激励名称。点击 OK 后回到主界面。

单击 Tools→Run Simulation Tool→RTL Simulation 来进行功能仿真,如图所示

然后就会发现报错如下所示,这是因为默认设置的仿真工具路径不对

点击Tools→Options→EDA Tool Options 设置对应的仿真软件的路径,注意,和原来的仿真路径相比,多了一层【modelsim_ase】目录

然后我们再次启动仿真,可以看到,启动了【ModelSim-Altera】软件,并可以在输出中看到打印了“Hello world", 同时我们还可以看到波形的变化。

————————————————

版权声明:本文为CSDN博主「Willliam_william」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_38113006/article/details/121569176

总结

参考文献

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- pycharm快捷键

- 如何实现APP安全加固?加固技术、方法和方案

- Python常用的自动化小脚本!

- react+redux+antd-mobile 之 记账本案例

- 第九章 数据可视化—pyecharts

- 独立站上传产品的方式有哪些?如何快速上品?采集、同步、复制

- 【NI-RIO入门】记录和监控数据

- mysql 中给表单添加外键的方法

- Yarn ResourceManager 页面上的绿色条块(Used Resources)反映的是真实的资源占用情况吗?

- 住宅代理妙用:网络抓取的必备工具