FPGA引脚物理电平(内部资源,Select IO)-认知2

-

引脚电平

The SelectIO pins can be configured to various I/O standards, both single-ended and differential.

? Single-ended I/O standards (e.g., LVCMOS, LVTTL, HSTL, PCI, and SSTL)

? Differential I/O standards (e.g., LVDS, Mini_LVDS, RSDS, PPDS, BLVDS, and differential HSTL and SSTL) -

引脚种类

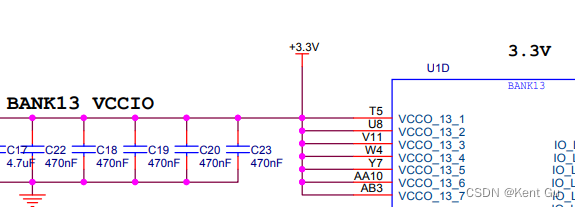

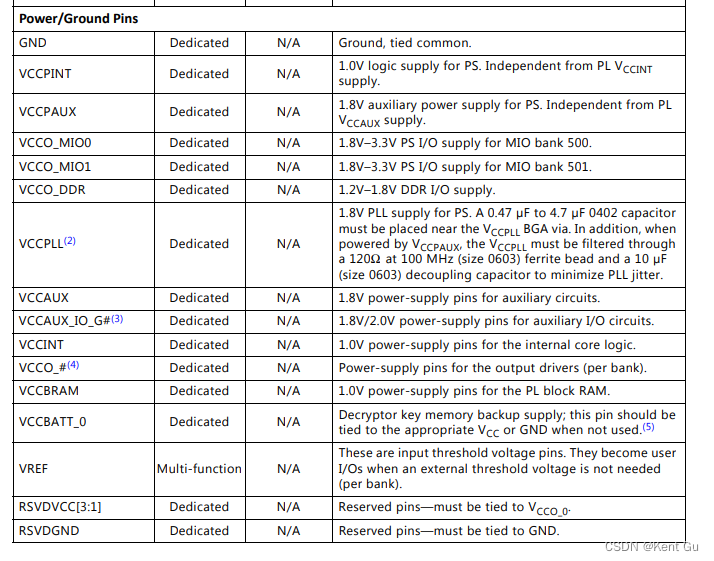

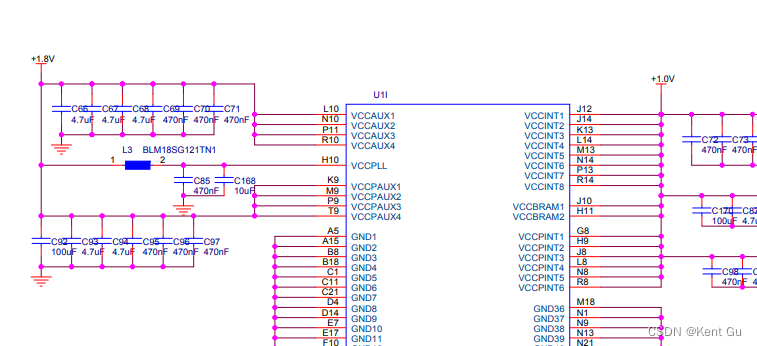

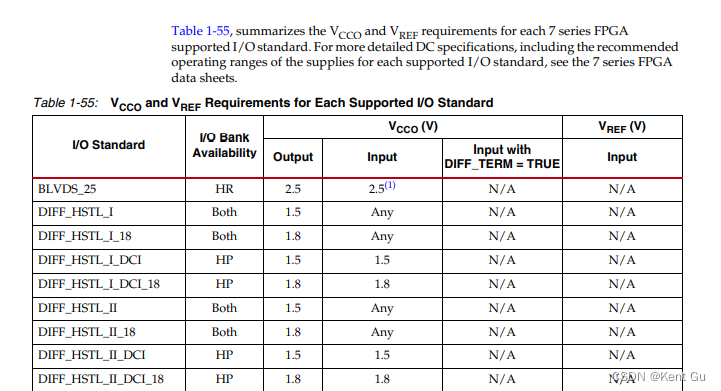

VCCO,for PL

每个Bank对应一个电压,HP Bank VCCO电压应该小于<=1.8V.

The VCCO supply is the primary power supply of the 7 series I/O circuitry

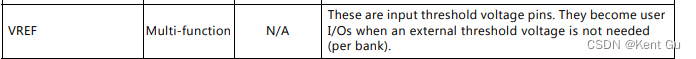

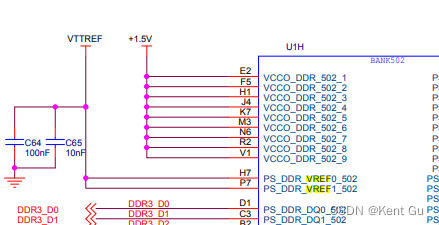

Vref,

Single-ended I/O standards with a differential input buffer require an input reference voltage (VREF).

VccAux,

VCCAux_IO,

The auxiliary I/O (VCCAUX_IO) supply rail is only present in HP I/O banks and provides power to the I/O circuitry.

-

引脚配置资源

3.1,DCI,

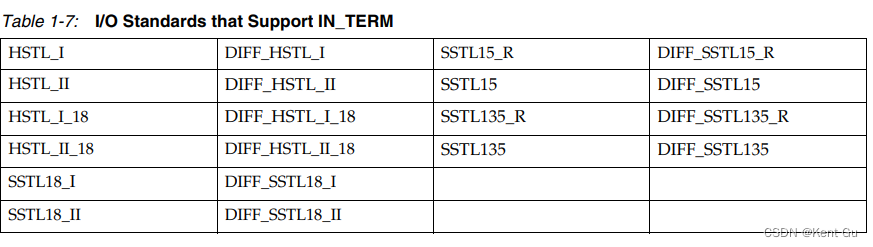

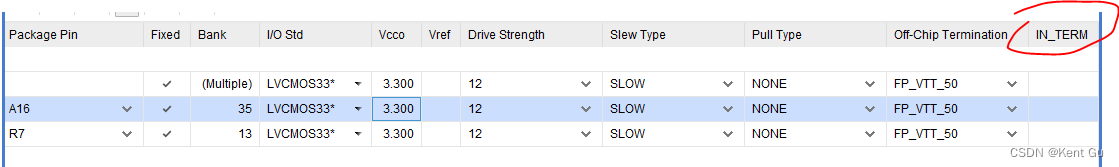

3.2, IN_TERM,

Uncalibrated Split Termination in High-Range I/O Banks (IN_TERM)

-

引脚电平

电平标准网站:https://www.jedec.org/

LVTTL, low voltage ttl, 3.3V.

LVCMOS, Low voltage cmos, LVCMOS12,LVCMOS18,LVCMOS25,LVCMOS33

LVDCI/2 (Low-Voltage Digitally Controlled Impedance)

HSLVDCI (High-Speed LVDCI)

HSTL (High-Speed Transceiver Logic), HSTL_ I_12, HSTL_ I_18,HSTL_ I_DCI,DIFF_HSTL_I a

SSTL (Stub-Series Terminated Logic)

LVDS and LVDS_25 (Low Voltage Differential Signaling)

RSDS (Reduced Swing Differential Signaling)

SelecIO, 主要讲的根据性能/程序级去选择引脚。因为需要考虑内部资源。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 【MySQL】数据库概述与SQL语句

- IIC Master 设计实现

- IPsec vpn和SSL VPN的详解对比!

- 【数字信号分析】小波变换气象数据分析(小波系数、小波方差、小波模、小波模平方)【含Matlab源码 2409期】

- 手搓没有softmax 的gpt

- 【CAN】Basic CAN和Full CAN

- 1-2B参数规模大模型使用心得及模型汇总

- 什么是动态IP?静态IP和动态IP有什么区别?

- 使用 Kubernetes 部署机器学习模型的优势

- MySql踩坑记录 DATE_FORMAT函数