《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(17)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(16)

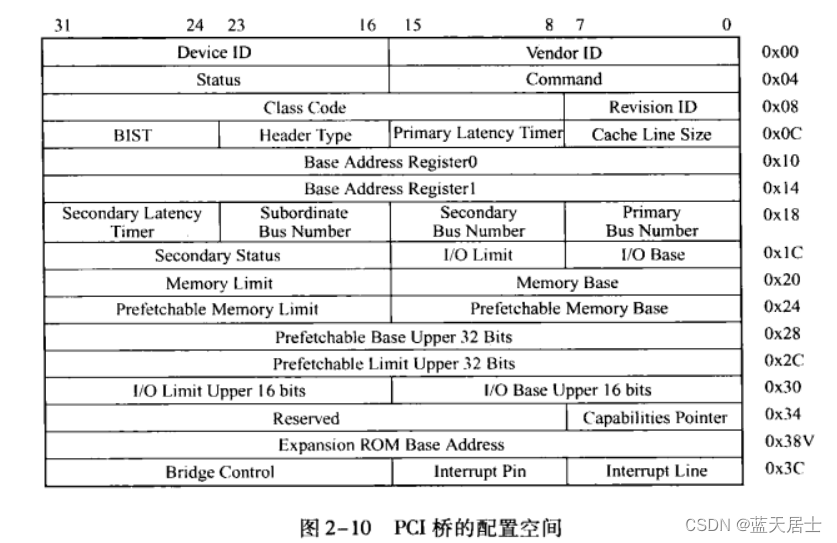

2.3.3?PCI桥的配置空间

PCI桥使用的配置空间的寄存器如图2-10所示。

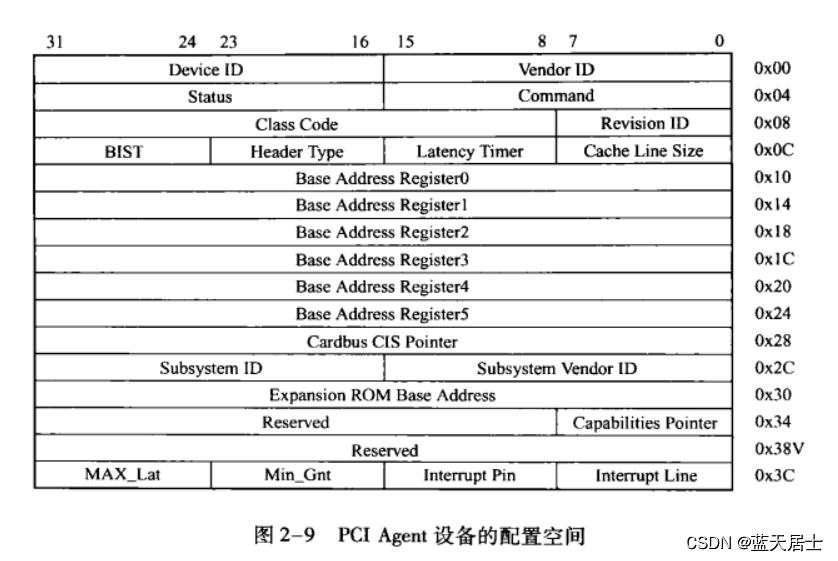

PCI桥作为一个PCI设备,使用的许多配置寄存器与PCI Agent的寄存器是类似的,如Device ID、Vendor ID、Status、Command、Interrupt Pin、Interrupt Line寄存器等。为了便于理解两者的异同,再次贴出PCI Agent设备的配置空间,如下图所示:

本节不再重复介绍这些寄存器,而重点介绍在PCI桥中与PCI Agent的配置空间不相同的寄存器。

与PCI Agent设备不同,在PCI桥中只含有两组BAR寄存器,即Base Address Register 0~1寄存器。这两组寄存器与PCI? Agent设备配置空间的对应寄存器的含义一致。但是在PCI桥中,这两组寄存器是可选的。如果在PCI桥中不存在私有寄存器,那么可以不使用这两组寄存器设置BAR空间。

在大多数PCI桥中都不存在私有寄存器,操作系统也不需要为PCI桥提供专门的驱动程序,这也是这类桥被称为透明桥的原因。当在PCI桥中不存在私有空间时,PCI桥将这两个BAR寄存器的值初始化为0。在PCI桥的配置空间中使用两个BAR寄存器的原因是,这两个32位的寄存器可以组成一个64位地址空间。

在PCI桥的配置空间中,有许多寄存器是PCI桥所特有的。PCI桥除了作为PCI设备之外,还需要管理其下连接的PCI总线子树使用的各类资源,即Secondary Bus所连接PCI总线子树使用的资源。这些资源包括存储器、I/O地址空间和总线号。

在PCI桥中,与Secondary Bus相关的寄存器包括两类:一类寄存器管理Secondary Bus之下PCI子树的总线号,如Secondary Bus Number和Subordinate Bus Number寄存器;另一类管理寄存器管理下游PCI总线的I/O和存储器地址空间,如I/O Limit和Memory Limit、I/O?Base和Memory Base寄存器。在PCI桥中还使用Primary Bus寄存器保存上游的PCI总线号。

其中,存储器(Memory)地址空间还分为可预读空间和不可预读空间。Perfetchable Memory Limit和Perfetchable Memory Base寄存器管理可预读空间,而Memory Limit、Memory Base寄存器管理不可预读空间。在PCI体系结构中,除了ROM地址空间之外,PCI设备使用的地址空间大多都是不可预读的。

对于PCI桥配置空间中所特有的寄存器的详细介绍,放在下一回中。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 20.仿简道云公式函数实战-数学函数-RADIANS

- LLM之RAG实战(十六)| 使用Llama-2、PgVector和LlamaIndex构建LLM Rag Pipeline

- 初识HTTP协议

- 《Kotlin核心编程》笔记:可空类型&平台类型&装箱类型&数组类型&泛型&协变与逆变

- HashMap的五种遍历方式

- 《动手学深度学习》学习笔记 第6章 卷积神经网络

- 什么是CSS3?深入理解css3

- BFS算法套路框架与双指针技巧套路框架

- 嵌入式八股文——Linux常用命令介绍及用法

- RLAIF方法与传说中的函数‘Q‘,揭露OpenAI那不为人知的Qstar计划