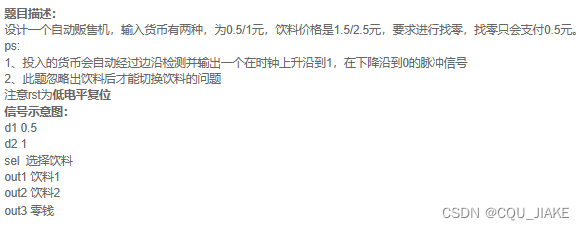

12.21自动售货机,单物品,多物品

发布时间:2023年12月30日

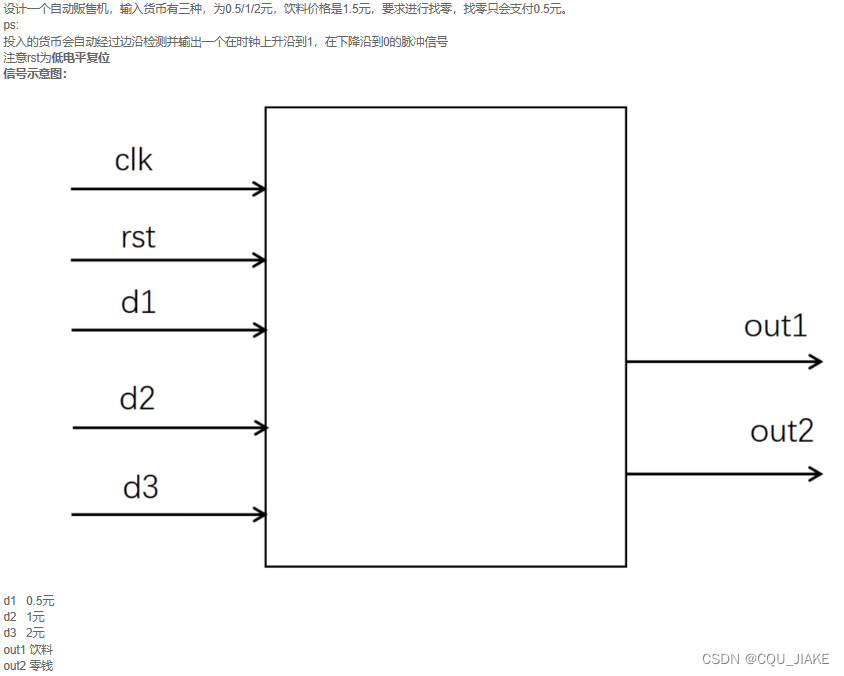

自动售货机?

if朴素方法

?一种思路是用寄存器cnt记录已有的最小单位货币量,这里就是0.5

当d1时,cnt+1;d2时,cnt+2;d3时,cnt+4;

`timescale 1ns/1ns

module seller1(

input wire clk ,

input wire rst ,

input wire d1 ,

input wire d2 ,

input wire d3 ,

output reg out1,

output reg [1:0]out2

);

reg[2:0]cnt;

always@(posedge clk,negedge rst)begin

if(!rst)begin

cnt<=0;

out1<=0;

out2<=0;

end

else begin

if(d1)cnt<=cnt+1;

else if(d2)cnt<=cnt+2;

else if(d3)cnt<=cnt+4;

else if(cnt>=3)begin

out1<=1;

out2<=cnt-3;

cnt<=0;//记得复位为0,表示一个过程的结束

end

else begin

out1<=0;

out2<=0;

end//这里需要注意一定需要这一步,不然在不复位时,将保持一直输出1的状态

end

end

endmodule这里注意,d1,d2,d3都是以脉冲的形式,即只会接受一个时间步里,检测也都是

`timescale 1ns/1ns

module seller1(

input wire clk ,

input wire rst ,

input wire d1 ,

input wire d2 ,

input wire d3 ,

output reg out1,

output reg [1:0]out2

);

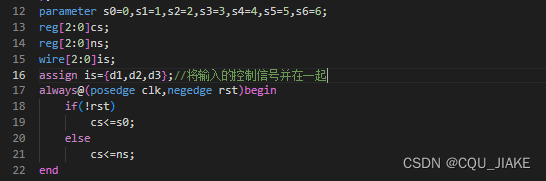

parameter S0 = 'd0, S1 = 'd1, S2 = 'd2, S3 = 'd3 , S4 = 'd4, S5 = 'd5 , S6 = 'd6;

reg [2:0] current_state;

reg [2:0] next_state;

wire [2:0] input_state;//将输入组合起来

assign input_state = {d1,d2,d3};

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

current_state <= S0;

end

else begin

current_state <= next_state;

end

end

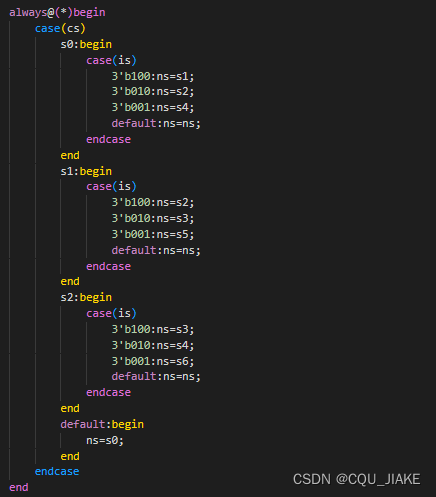

always@(*)begin

case(current_state)

S0:begin

case(input_state)

3'b100:next_state = S1 ;

3'b010:next_state = S2 ;

3'b001:next_state = S4 ;

default:next_state = next_state;

endcase

end

S1:begin

case(input_state)

3'b100:next_state = S2 ;

3'b010:next_state = S3 ;

3'b001:next_state = S5 ;

default:next_state = next_state;

endcase

end

S2:begin

case(input_state)

3'b100:next_state = S3 ;

3'b010:next_state = S4 ;

3'b001:next_state = S6 ;

default:next_state = next_state;

endcase

end

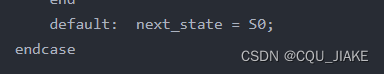

default:begin

next_state = S0;

end

endcase

end

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

out1 <= 1'b0;

out2 <= 2'b0;

end

else begin

case(next_state)

S3: begin out1 <= 1'b1;out2 <= 2'b0; end

S4: begin out1 <= 1'b1;out2 <= 2'b1; end

S5: begin out1 <= 1'b1;out2 <= 2'b10; end

S6: begin out1 <= 1'b1;out2 <= 2'b11; end

default: begin out1 <= 1'b0;out2 <= 2'b0; end

endcase

end

end

endmodule状态机方法

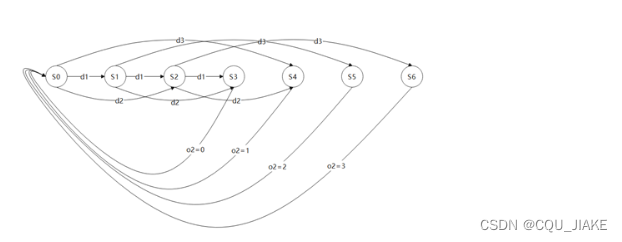

采用MOORE状态机,即输出只与状态有关,而与当前输入信号无关

状态机的方式可以支持一次投入多枚硬币

MOORE三段

第一段:信号声明,状态定义,状态转换

第二段:由现态,依据输入信号确定次态

这里可以看出,如果一次投入多个硬币,可以进行转移与判断,只需在case里增添判断即可

第三段:依据次态确定输出信号

自动售货机(支持多物品售卖)

sel为0时买一块五,即第四个状态,s3;为1时买两块五,为第六个状态,s5

状态机

`timescale 1ns/1ns

module seller2(

input wire clk ,

input wire rst ,

input wire d1 ,

input wire d2 ,

input wire sel ,

output reg out1,

output reg out2,

output reg out3

);

//*************code***********//

parameter S0=0, S0_5=1, S1=2, S1_5=3, S2=4, S2_5=5, S3=6;

reg[2:0] state, nstate;

always@(posedge clk or negedge rst) begin

if(~rst)

state <= 0;

else

state <= nstate;

end

always@(*) begin

case(state)

S0 : nstate = d1? S0_5:

d2? S1:

nstate;

S0_5 : nstate = d1? S1:

d2? S1_5:

nstate;

S1 : nstate = d1? S1_5:

d2? S2:

nstate;

S1_5 : nstate = ~sel? S0:

d1? S2:

d2? S2_5:

nstate;

S2 : nstate = ~sel? S0:

d1? S2_5:

d2? S3:

nstate;

default: nstate = S0;

endcase

end

always@(*) begin

if(~rst) begin

{out1, out2, out3} = 3'b000;

end

else begin

case(state)

S0, S0_5, S1: {out1, out2, out3} = 0;

S1_5 : {out1, out2, out3} = ~sel? 3'b100: 3'b000;

S2 : {out1, out2, out3} = ~sel? 3'b101: 3'b000;

S2_5 : {out1, out2, out3} = ~sel? 3'b101: 3'b010;

S3 : {out1, out2, out3} = ~sel? 3'b101: 3'b011;

default : {out1, out2, out3} = 3'b000;

endcase

end

end

//*************code***********//

endmodule

上面为mealy型状态机,即输出取决于现态与输入信号?

`timescale 1ns/1ns

module seller2(

input wire clk ,

input wire rst ,

input wire d1 ,

input wire d2 ,

input wire sel ,

output reg out1,

output reg out2,

output reg out3

);

parameter S0 = 'd0, S1 = 'd1, S2 = 'd2, S3 = 'd3 , S4 = 'd4, S5 = 'd5, S6 = 'd6;

reg [2:0] current_state;

reg [2:0] next_state;

wire [1:0] input_state;

assign input_state = {d1,d2};

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

current_state <= S0;

end

else begin

current_state <= next_state;

end

end

always@(*)begin

if (!sel) begin

case(current_state)

S0:begin

case(input_state)

2'b10 :next_state = S1 ;

2'b01 :next_state = S2 ;

default:next_state = next_state;

endcase

end

S1:begin

case(input_state)

2'b10 :next_state = S2 ;

2'b01 :next_state = S3 ;

default:next_state = next_state;

endcase

end

S2:begin

case(input_state)

2'b10 :next_state = S3 ;

2'b01 :next_state = S4 ;

default:next_state = next_state;

endcase

end

default: next_state = S0;

endcase

end

else begin

case(current_state)

S0:begin

case(input_state)

2'b10 :next_state = S1 ;

2'b01 :next_state = S2 ;

default:next_state = next_state;

endcase

end

S1:begin

case(input_state)

2'b10 :next_state = S2 ;

2'b01 :next_state = S3 ;

default:next_state = next_state;

endcase

end

S2:begin

case(input_state)

2'b10 :next_state = S3 ;

2'b01 :next_state = S4 ;

default:next_state = next_state;

endcase

end

S3:begin

case(input_state)

2'b10 :next_state = S4 ;

2'b01 :next_state = S5 ;

default:next_state = next_state;

endcase

end

S4:begin

case(input_state)

2'b10 :next_state = S5 ;

2'b01 :next_state = S6 ;

default:next_state = next_state;

endcase

end

default: next_state = S0;

endcase

end

end

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

out1 <= 1'b0;

out2 <= 1'b0;

out3 <= 1'b0;

end

else begin

if(!sel)begin

case (next_state)

S3: begin out1 <= 1'b1;out2 <= 1'b0;out3 <= 1'b0;end

S4: begin out1 <= 1'b1;out2 <= 1'b0;out3 <= 1'b1;end

default:begin out1 <= 1'b0;out2 <= 1'b0;out3 <= 1'b0;end

endcase

end

else begin

case (next_state)

S5: begin out1 <= 1'b0;out2 <= 1'b1;out3 <= 1'b0;end

S6: begin out1 <= 1'b0;out2 <= 1'b1;out3 <= 1'b1;end

default:begin out1 <= 1'b0;out2 <= 1'b0;out3 <= 1'b0;end

endcase

end

end

end

endmodule上面为标准的MOORE状态机代码,即输出只与次态有关

在状态转换中,一定要记得写

即相当于 ?后面的复位,不然没办法复位

?后面的复位,不然没办法复位

文章来源:https://blog.csdn.net/m0_73553411/article/details/135130144

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- linux文件目录权限

- 消费者购买决策行为分析及引导VR仿真实训软件实用性强

- 【贪心】牛客练习赛90 C

- linux环境redis集群部署-手把手教程(小白必看)

- Docker极限压缩tar镜像,20G变10G

- 竞赛保研 机器视觉人体跌倒检测系统 - opencv python

- 基于萤火虫算法优化BP神经网络回归分析,基于GSO-BP的回归预测

- ChatGPT论文指南|ChatGPT助力论文论点提炼详细流程!【建议收藏】

- 1.你好, Python!

- 解决Vue3 中Eharts数据更新渲染不上问题