PCIe 6.0生态业内进展分析总结

上一篇,我们针对PCIe 6.0的功能更新与实现挑战做了简单的分析与总结。更多详细内容可以参考:

那么,PCIe 6.0已经发布了一段时间了,业内硬件支持PCIe 6.0目前有哪些进展呢?小编根据公开信息,做了一些不完全总结,仅供大家参考!(也欢迎大家在文章底部补充留言交流~)

1.PCIe 6.0连接器

Amphenol作为全球知名的互连产品制造商,在2023 FMS上对外也宣布了对多组支持PCIe 6.0的产品

-

Amphenol MCIO(Mini Cool Edge IO)线缆连接器:该产品针对最近开发的PCIe 6.0内部电缆规格Ver 0.9进行了定制设计。此外,Amphenol展示的下一代产品Multi-Trak?被OCP DC-MHS HPM作为近端I/O解决方案采用,支持PCIe 5.0和6.0规范速度,并且与x8规格的MCIO线缆兼容互连。

-

Amphenol ExtremePort? Swift线缆连接器:专为服务器和网络应用提供高速、低剖面解决方案,近期已实现对PCIe 6.0性能的支持。

-

Amphenol PCIe 6.0 CEM连接器:符合最新PCIe 6.0 CEM规格Ver 0.7草案的SI要求,表明该产品已经准备好应对PCIe 6.0时代的挑战。

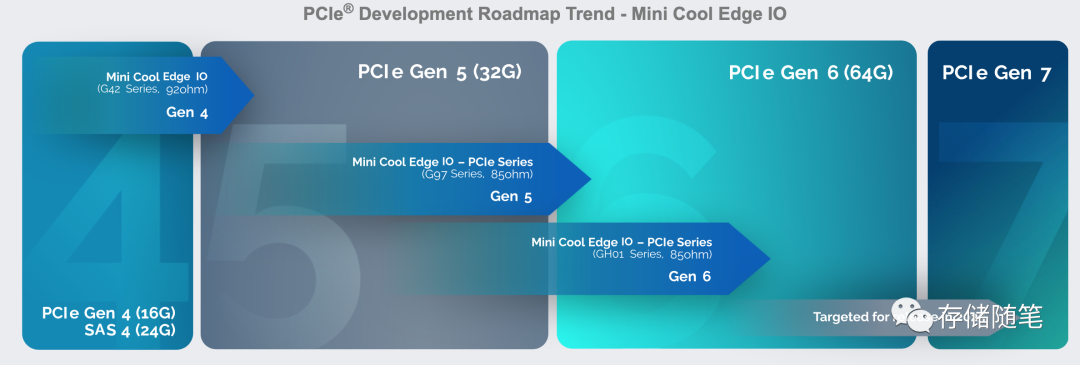

Mini Cool Edge IO是Amphenol公司推出的一种高性能、高密度内部连接器解决方案,专为满足下一代高速信号传输需求而设计。这种连接器具有0.60mm的针脚间距(pitch),采用紧凑型设计,旨在优化系统空间并支持高效能数据传输。它适用于需要在有限空间内进行高速信号布线和管理的设计,如服务器、网络设备以及其他要求苛刻的数据中心应用。

Mini Cool Edge IO系列不仅灵活且坚固耐用,还具有成本效益,可以扩展到24Gbps SAS4等高速协议的标准,确保信号完整性,并有助于降低系统能耗。该产品通过其创新设计和技术特性,解决了高速信号在传输过程中可能出现的信号衰减、串扰等问题,从而提升整体系统的性能表现和可靠性。此外,它可能还兼容PCIe标准,例如适应PCIe 6.0等新一代技术规格的需求。

2.PCIe 6.0 IP设计

(1)Alphawave

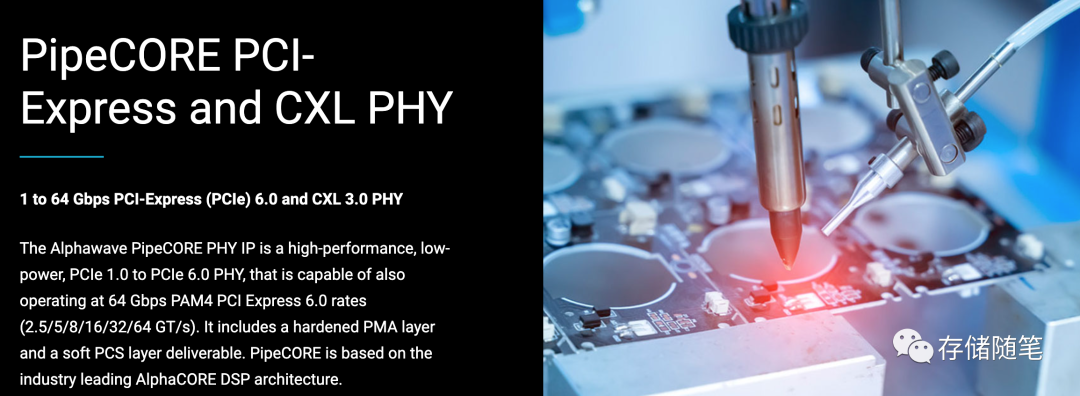

近日,一家名为Alphawave的芯片设计公司,与示波器公司是德科技Keysight联合展示了其PCIe 6.0控制器和物理接口与Keysight测试设备之间的互操作性,在数据传输速率上达到了64 GT/s。这一举措证明了Alphawave已准备好制造搭载PCIe 6.0接口的芯片,从而加入到越来越多准备迎接2024年首款商业可用PCIe 6.0设备到来的生态建设行列。

Alphawave的PipeCORE PHY IP是一款高性能、低功耗的物理层(PHY)集成电路设计知识产权,适用于从PCIe 1.0到PCIe 6.0的全系列PCI Express标准。该IP特别强调了其能够在64 Gbps PAM4 PCI Express 6.0速率下运行的能力,这意味着它可以支持2.5 GT/s、5 GT/s、8 GT/s、16 GT/s、32 GT/s直至64 GT/s的数据传输速度。

(2)Synopsys

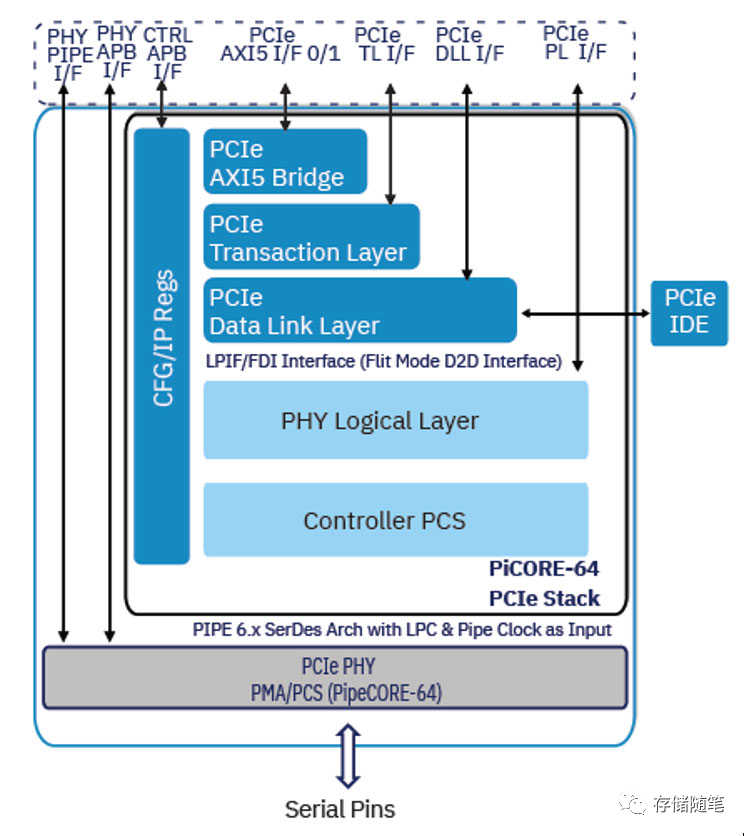

Synopsys是另外一家PCIe IP供应商。早在2023年9月份,Intel Innovation活动中,Synopsys和Intel双方共同成功演示了其PCIe Gen6解决方案与Intel测试芯片之间的互操作性。

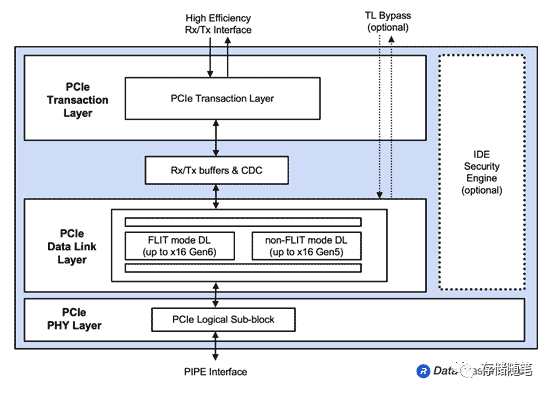

此次展示的Synopsys PCIe 6.0全套IP解决方案包含了控制器、PHY、验证IP以及完整性与数据加密(IDE)安全IP,旨在加速高性能计算和AI应用芯片的开发进程。

(3)Rambus

Rambus Inc.是一家知名的半导体技术公司,提供包括内存接口、高速SerDes(serializer/deserializer)和控制器在内的多种高性能互连解决方案。在PCIe 6.0规范发布后,Rambus针对这一标准开发了一系列关键知识产权(IP)产品,

Rambus PCIe 6.0 IP套件主要包括:

-

PCIe 6.0控制器IP:这是实现PCIe 6.0功能的核心部分,负责处理数据包的发送和接收,管理事务层和数据链路层的功能,并确保与PCIe规范兼容的数据传输。该控制器支持最新的带宽速度,即每通道64 GT/s,并可能整合了先进的错误检测和纠正机制以保证数据完整性。

-

PHY物理层IP:作为连接控制器和其他系统组件的关键硬件模块,PHY物理层IP采用了先进的信号处理技术来实现高效的数据传输,同时通过PAM4调制方式应对高频率下的信号衰减问题,从而实现在更高速率下保持信号质量和稳定性。

-

CXL 3.0支持:Rambus的PCIe 6.0子系统还支持Compute Express Link (CXL) 3.0规范,这是一个开放的行业标准,旨在提高CPU到设备间如GPU、FPGA和其他加速器的互连性能和效率。

(4)Cadence

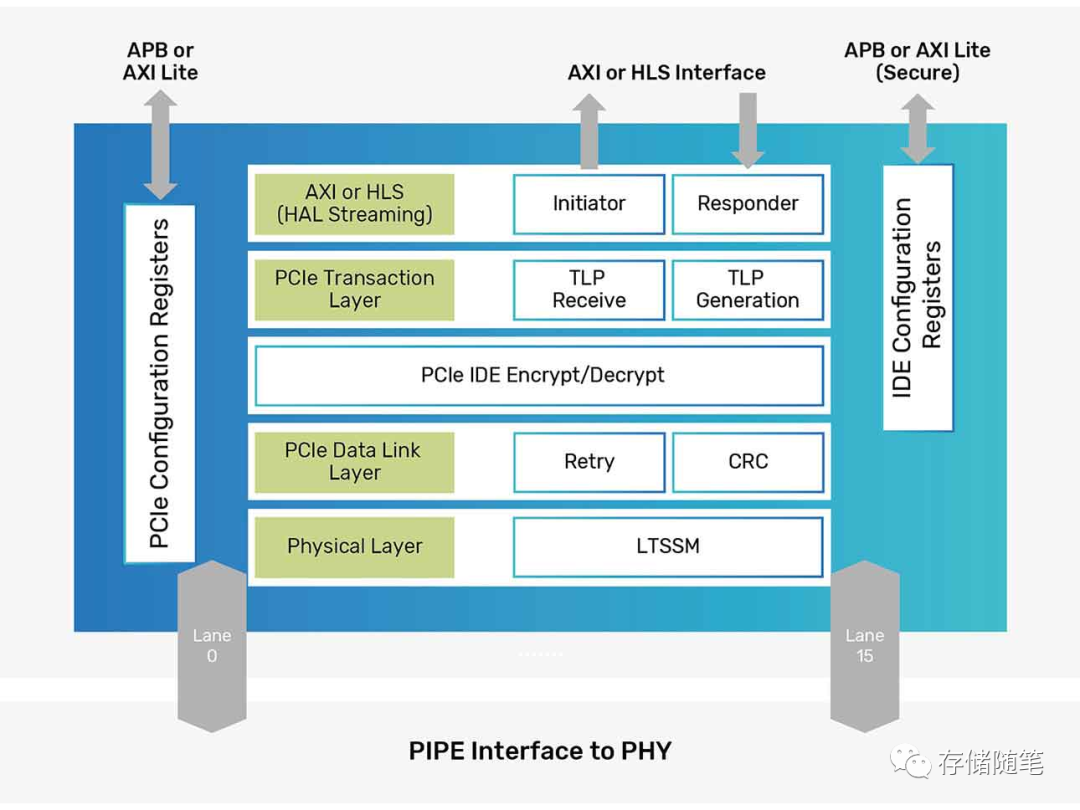

Cadence的PCIe控制器IP兼容PCIe 6.0、5.0、4.0、3.1、2.1和1.1等多个版本协议,并支持最新的ECNs,包括IDE/DOE等

该控制器IP提供根端口、终端端点或双模模式选择,以满足多样化的应用场景需求。同时具备多分支支持功能,使得应用能够轻松构建从1x16到16x1等各种配置,极大地增强了设计灵活性。

控制器内建对SR-IOV的支持,可实现高达256个虚拟功能以及4K字节的有效载荷大小,并且还提供了基于PASID的可扩展I/O虚拟化能力。

性能方面,该控制器IP在基准测试中达到了理论性能的95%,采用了超标量设计,确保在所有数据速率下都能实现高吞吐量和低延迟。此外,为最大化性能表现,用户可以根据实际需求选择最适合的客户端接口。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- docker——网络(bridge简介和案例实践、overlay简介)

- 【安卓模拟器】雷电模拟器9 v9.0.64 绿色版(免安装版,一键绿化)

- Windows系统历史版本简介

- toluaframework中C#怎么调用Lua的方法以及无GC方法

- 学习记录1.10

- 为什么西拉和设拉子的味道如此不同?

- export default 和exprot

- Stable Diffusion 源码解析(1)

- 优化企业运营,深入探索SAP库存管理解决方案

- Mybatis的占位符中使用的名称