「Verilog学习笔记」根据RTL图编写Verilog程序

发布时间:2023年12月21日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

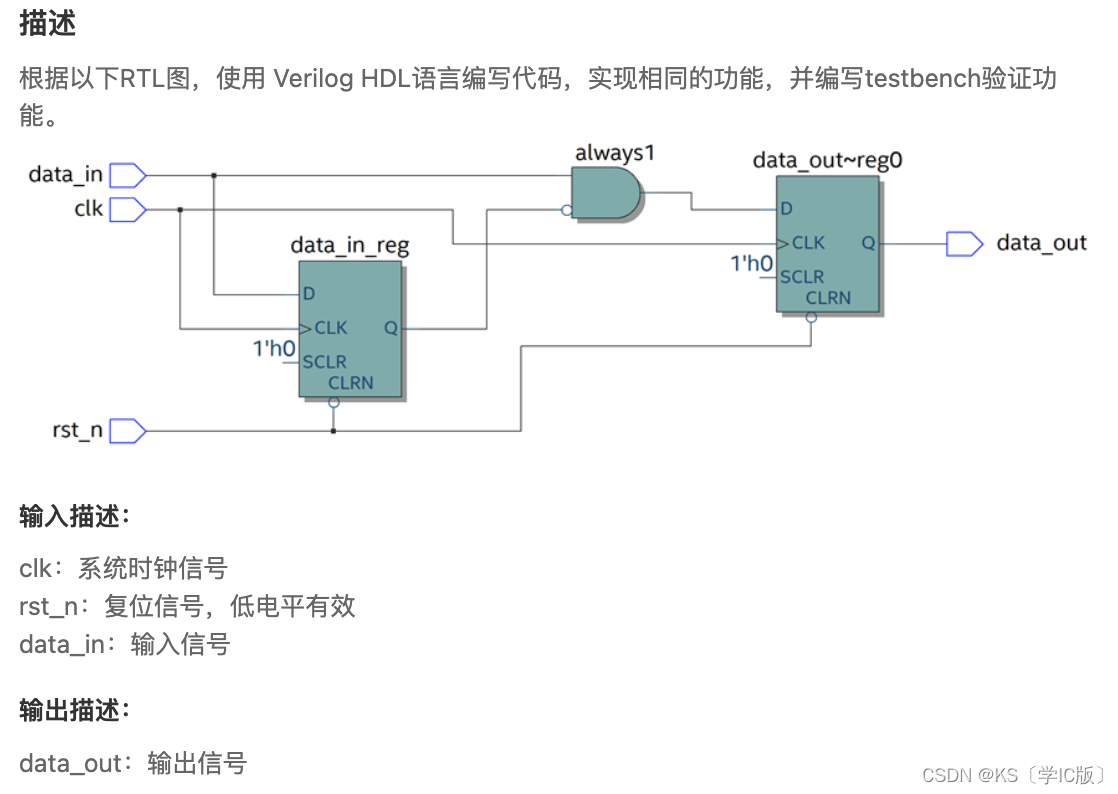

观察题目给出的RTL图,主要的器件是两个D触发器,一个与门。D触发器含有异步复位信号,且为低电平有效。data_in输入到D触发器,D触发器的输出Q是前一时刻的data_in,即data_in打一拍得到data_in_reg。与门表示data_out = data_in && !data_in_reg。再通过一个D触发器输出,这样子处理使data_in上升沿出现的时候,data_out保持一个时钟的高电平。由此可见,RTL实现了求data_in上升沿的功能。

`timescale 1ns/1ns

module RTL(

input clk,

input rst_n,

input data_in,

output reg data_out

);

reg data_in_reg ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) data_in_reg <= 0 ;

else data_in_reg <= data_in ;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) data_out <= 0 ;

else data_out <= data_in && ~data_in_reg ;

end

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135103435

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 揭秘漫途遥测终端的功能及应用

- 栈的常见题型

- YOLOv7改进Shape-IoU损失函数:元旦假期最新 IoU论文|考虑边界框形状和比例的更准确的指标,YOLO性能提升

- office bookmarks

- Ubuntu系统的基础操作和使用

- 精通推荐算法3:精排特征交叉架构(体系化总结,面试必备)

- 文献速递:PET-影像组学专题—《基于影像组学的基线PETCT成像在淋巴瘤中的作用:诊断、预后和反应评估》

- linux DHCP赛题配置

- 2024华数杯国际赛AB题五小问完整思路+数据+四小问代码+后续高质量成品论文+运行结果高清图+参考文献

- resetlogs失败故障恢复-ORA-01555---惜分飞