STM32 NVIC结构体中成员偏移量的具体计算

发布时间:2024年01月02日

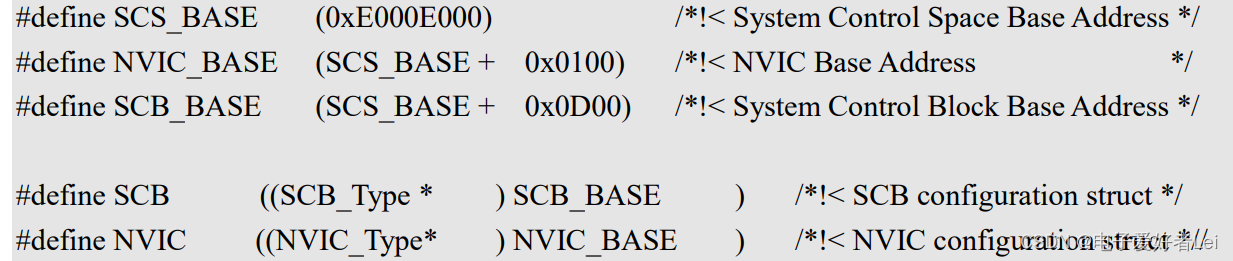

首先来看NVIC和SCB这两个结构体指向的地址:

?这两个结构体的成员:

typedef struct

{

__IO uint32_t ISER[8]; /*!< Offset: 0x000 Interrupt Set Enable Register */

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; /*!< Offset: 0x080 Interrupt Clear Enable Register */

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; /*!< Offset: 0x100 Interrupt Set Pending Register */

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; /*!< Offset: 0x180 Interrupt Clear Pending Register */

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; /*!< Offset: 0x200 Interrupt Active bit Register */

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; /*!< Offset: 0x300 Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644];

__O uint32_t STIR; /*!< Offset: 0xE00 Software Trigger Interrupt Register */

} NVIC_Type; typedef struct

{

__I uint32_t CPUID; /*!< Offset: 0x00 CPU ID Base Register */

__IO uint32_t ICSR; /*!< Offset: 0x04 Interrupt Control State Register */

__IO uint32_t VTOR; /*!< Offset: 0x08 Vector Table Offset Register */

__IO uint32_t AIRCR; /*!< Offset: 0x0C Application Interrupt / Reset Control Register */

__IO uint32_t SCR; /*!< Offset: 0x10 System Control Register */

__IO uint32_t CCR; /*!< Offset: 0x14 Configuration Control Register */

__IO uint8_t SHP[12]; /*!< Offset: 0x18 System Handlers Priority Registers (4-7, 8-11, 12-15) */

__IO uint32_t SHCSR; /*!< Offset: 0x24 System Handler Control and State Register */

__IO uint32_t CFSR; /*!< Offset: 0x28 Configurable Fault Status Register */

__IO uint32_t HFSR; /*!< Offset: 0x2C Hard Fault Status Register */

__IO uint32_t DFSR; /*!< Offset: 0x30 Debug Fault Status Register */

__IO uint32_t MMFAR; /*!< Offset: 0x34 Mem Manage Address Register */

__IO uint32_t BFAR; /*!< Offset: 0x38 Bus Fault Address Register */

__IO uint32_t AFSR; /*!< Offset: 0x3C Auxiliary Fault Status Register */

__I uint32_t PFR[2]; /*!< Offset: 0x40 Processor Feature Register */

__I uint32_t DFR; /*!< Offset: 0x48 Debug Feature Register */

__I uint32_t ADR; /*!< Offset: 0x4C Auxiliary Feature Register */

__I uint32_t MMFR[4]; /*!< Offset: 0x50 Memory Model Feature Register */

__I uint32_t ISAR[5]; /*!< Offset: 0x60 ISA Feature Register */

} SCB_Type;以 NVIC_Type 中的成员和地址偏移为例:(需要知道的一个前提是 NVIC_Type 中的成员是32位寄存器,但其实每个32位寄存器都是由4个临近的8位寄存器组成的)

第一个成员为 __IO uint32_t ISER[8]; ,其偏移地址为 0x000

第二个成员为 uint32_t RESERVED0[24];

第三个成员为 __IO uint32_t ICER[8]; ,其偏移地址为 0x080

那么从第一个成员的地址到第三个成员的地址跨度为 0x080,那么下面我们来推算下为什么是0x080:

前面所说,每32位寄存器由4个8位寄存器组成,而每8位的寄存器对应着一个地址,即对于?NVIC_Type 的前两个成员来说,就对应了128个地址(128=(8+24)*4)!这就是为什么第三个成员的偏移地址为128的原因了(128的十六进制为0x80)。

其余的一次类推即可【花花】【花花】

文章来源:https://blog.csdn.net/qq_63796876/article/details/135277265

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 深度学习爬取京东评论好评差评情感分析系统朴素贝叶斯算法应用python程序源代码数据集

- golang实现skiplist 跳表

- js比大小的问题

- Jupyter的简单实用

- 「实验记录」CS144 Lab1 StreamReassembler

- FastJSON 禁用循环引用检测DisableCircularReferenceDetect(“$ref“)

- vue3-13

- 2024.1.14

- 深度探讨数据库索引的数据结构及优化策略

- 若依微服务框架,富文本加入图片保存时出现JSON parse error: Unexpected character (‘/‘ (code 47)):...