跑马灯实验

4.1 实验目的

????????1.熟悉龙芯实验开发板、熟悉 VIVADO 的编译环境及操作流程。

????????2.掌握 FPGA 编程入门知识、利用门级方法实现简单逻辑电路。

????????3.继续学习 Verilog HDL 语法、掌握跑马灯的设计、熟悉调试过程。

4.2 实验原理及芯片

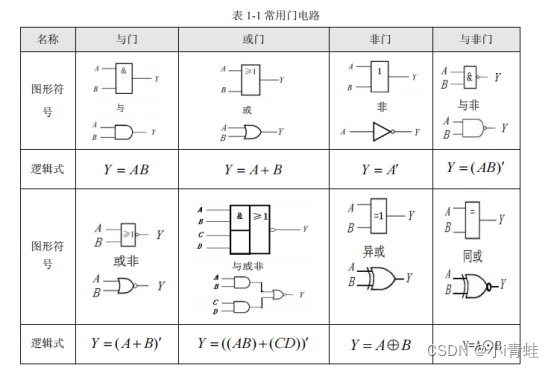

????????本次实验用 Verilog HDL 语言来描述 6 个不同的 2 输入逻辑门电路,其中包括:与、或、与非、或非、异或和同或门,并给出仿真测试代码和约束文件代码,可通过仿真波形图和龙芯实验板卡验证其功能,同时完成跑马灯(点亮实验台上 16 个 led 灯)实验。门电路是数字电路中最基本的元件,它能实现最基本的逻辑功能。

4.3 实验内容

????????1.FPGA 编程使用入门,在 VIVADO 环境下完成对简单电路工作情况的仿真模拟,掌握基本流程。

????????2.利用 Verilog 编程实现基本逻辑门电路,完成配置程序的下载,并在实验台上对程序进行最终验证。

????????3.点亮实验台上 16 个 led 灯。

????????4.利用 Verilog 编程实现组合逻辑功能,实现跑马灯的设计 (例如:1 秒钟流水显示)。

4.4 实验步骤

????????4.4.1 输入逻辑门电路验证

????????逻辑关系文件:

module gates2 (

input a,

input b,

output [5:0] y

);

assign y[0] = a & b; //与

assign y[1] = a |b; //或

assign y[2] = ~(a & b); //与非

assign y[3] =~(a | b); //或非

assign y[4] = a ^ b; //异或

assign y[5] = a ~^ b; //同或

endmodule????????仿真文件:

module gates2_test (

);

reg a,b;

wire [5:0] y;

gates2 test_gates2(a,b,y);

initial begin

a = 0; b =0; #100; //时间常量,#100 表示延迟 100 个时间单位

a=0; b =1; #100;

a = 1; b =0; #100;

a = 1; b =1; #100;

end

endmodule?????????实验具体步骤与对应关系不再一一阐述(群文件里都有),在这只对比输入逻辑门电路验证结果。

????????仿真结果:

????????真值表:

4.4.2 跑马灯实验设计

????????逻辑关系文件:

module led_test (

input sys_clk,

input rst_n,

output reg [15:0] led

);

reg [31:0] timer;

reg [15:0] led_counter;

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n) begin

timer <= 32'd0;

led_counter <= 4'b0000;

end

else if (timer == 32'd199_999_999 )begin

timer <= 32'd0; // 计时器达到 4 秒(50M*4-1=199999999),清零计时器

led_counter <= led_counter +1'b1;

end

else

timer <= timer + 1'b1; // 计时器加一

end

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n)

led <= 16'b0000_0000_0000_0000; // 复位信号有效时,将 LED 清零

else begin

case (led_counter)

4'b0000: led <= 16'b0000_0000_0000_0001;

4'b0001: led <= 16'b0000_0000_0000_0011;

4'b0010: led <= 16'b0000_0000_0000_0111;

4'b0011: led <= 16'b0000_0000_0000_1111;

4'b0100: led <= 16'b0000_0000_0001_1111;

4'b0101: led <= 16'b0000_0000_0011_1111;

4'b0110: led <= 16'b0000_0000_0111_1111;

4'b0111: led <= 16'b0000_0000_1111_1111;

4'b1000: led <= 16'b0000_0001_1111_1111;

4'b1001: led <= 16'b0000_0011_1111_1111;

4'b1010: led <= 16'b0000_0111_1111_1111;

4'b1011: led <= 16'b0000_1111_1111_1111;

4'b1100: led <= 16'b0001_1111_1111_1111;

4'b1101: led <= 16'b0011_1111_1111_1111;

4'b1110: led <= 16'b0111_1111_1111_1111;

4'b1111: led <= 16'b1111_1111_1111_1111;

default: led <= 16'b0000_0000_0000_0000;

endcase

end

end

endmodule????????实验思路:

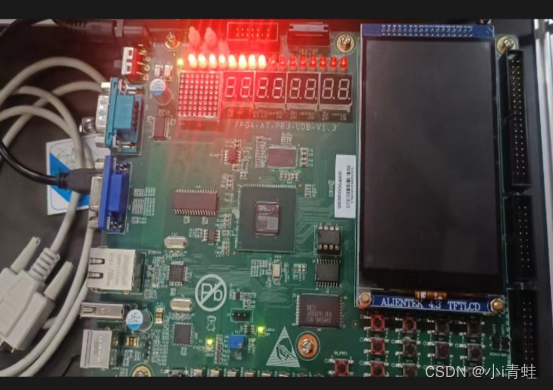

????????本次实验要实现跑马灯的效果,设置一个计时器(timer)和一个LED计数器(led_counter)。计时器每个时钟周期加一,直到达到4秒(199,999,999个时钟周期),然后计时器清零,并且LED计数器加一。

????????在第一个always块中,根据时钟信号和复位信号来控制计时器和LED计数器的行为。当复位信号有效时,计时器和LED都被清零。当计时器达到4秒时,计时器清零并且LED计数器加一。其他情况下,计时器继续加一。

????????在第二个always块中,根据LED计数器的值来设置LED的输出。根据LED计数器的不同值,LED的输出会依次从1到全亮(16位二进制数)。整个模块的功能是实现一个LED计时器,每4秒LED的亮度逐渐增加,最后达到全亮状态。

????????实验结果:

?

5 实验总结与反思

????????两次实验中,第一次验证输入逻辑门电路较为简单,由于有老师提供的代码,自己理解起来也比较容易,按照实验步骤的指导一步步做下来,自己也是顺利的完成了第一次实验。

????????在第二次实验中,由于没有老师提供的代码,在自己的摸索下,自己写出了一个跟同学不一样的跑马灯代码,通过设置一个计时器(timer)和一个LED计数器(led_counter)来实现跑马灯的效果,通过此次实验,自己也发现对Verilog HDL的理解还是不够熟悉,只停留在课本方面,没有运用到实际中,这让我看到了自己的差距,在下步的实验中,我将在课下继续努力,熟练掌握Verilog HDL语言。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 每日汇评:随着全面市场回归,黄金买家变得谨慎

- 回归预测 | Matlab基于SO-LSTM蛇群算法优化长短期记忆神经网络的数据多输入单输出回归预测

- 【CSS】保持元素宽高比

- 基于springboot+vue的牙科就诊管理系统

- 得帆云为玉柴打造CRM售后服务管理系统,实现服务全过程管理|基于得帆云低代码的CRM案例系列

- 2023年12月 Python(一级)真题解析#中国电子学会#全国青少年软件编程等级考试

- 芯片新闻-Global Semiconductor Sales Increase 5.3% Year-to-Year in November

- php中常用的几个安全函数

- C++力扣题目232--用栈实现队列

- 数据库常见的面试题