FPGA设计时序约束十三、Set_Data_Check

目录

一、序言

????通常进行时序分析时,会考虑触发器上时钟信号与数据信号到达的先后关系,从而进行setup,hold分析。同样地,我们也可以对两个数据信号进行类似的setup和hold关系检查。对于这类检查,有专门的约束命令,即set_data_check,可以对两个终点设置最大和最小要求时间检查,最终结果体现在设计的时序路径上,该约束只是用于检查时序的目的,不会影响布局布线。???

二、Set Data Check

2.1 基本概念

???set data check通常用于控制信号与数据信号间的时序关系检查,类似于常见的setup和hold关系检查。在set data check约束中,from是设置相关联的引脚,类比setup/hold中的时钟信号clk,to设置约束的引脚,类比setup/hold中的数据引脚。时序分析即是比较两个信号到达两个终点的时间。

2.2?设置界面

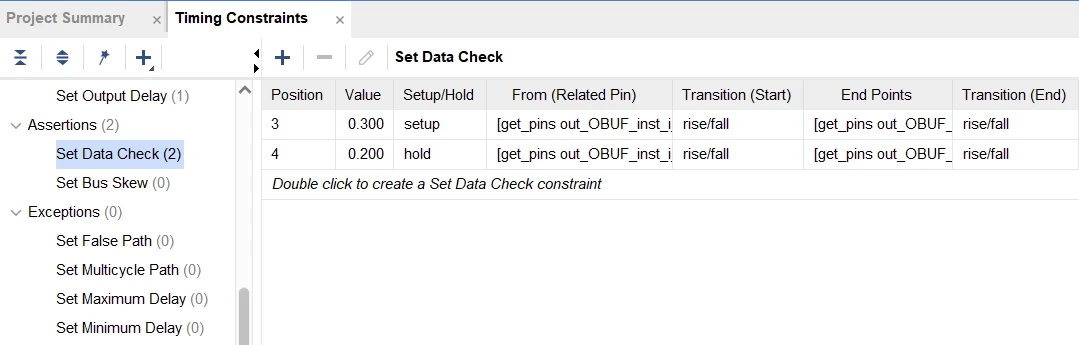

进入Timing Constraints界面,在左侧Others栏中选中Set Data Check,右侧即显示Set?Data?Check

?

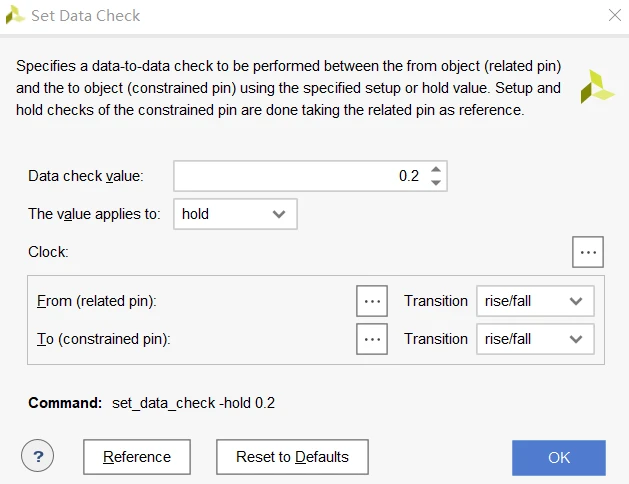

设置界面中需设置单data端口检查值Data Check Value,检查类性The Value applies to,关联的clock,关联引脚From,约束引脚对象to,对于引脚也可指定上升沿或下降沿,默认是上升沿和下降沿都可以。

?

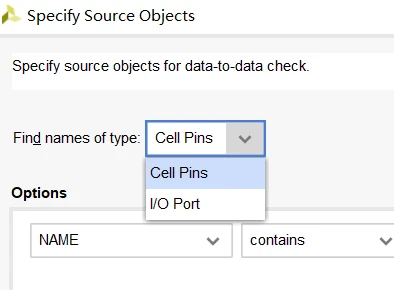

约束from/to的对象,只能为I/O port或cell pins

?

2.3?命令语法

命令格式

set_data_check [?from <args>] [?to <args>] [?rise_from <args>] [?fall_from <args>] [?rise_to <args>] [?fall_to <args>] [?setup] [?hold] [?clock <args>] [?quiet] [?verbose] <value>参数含义

?

1、以对从引脚A_IN到引脚C_IN进行一个setup的检查,A_IN是相关联的引脚,C_IN是被约束的引脚,即C_IN上的信号需早于A_IN上的信号2ns到达

set_data_check -from A_IN -to C_IN -setup 2.0三、工程示例

3.1 工程代码

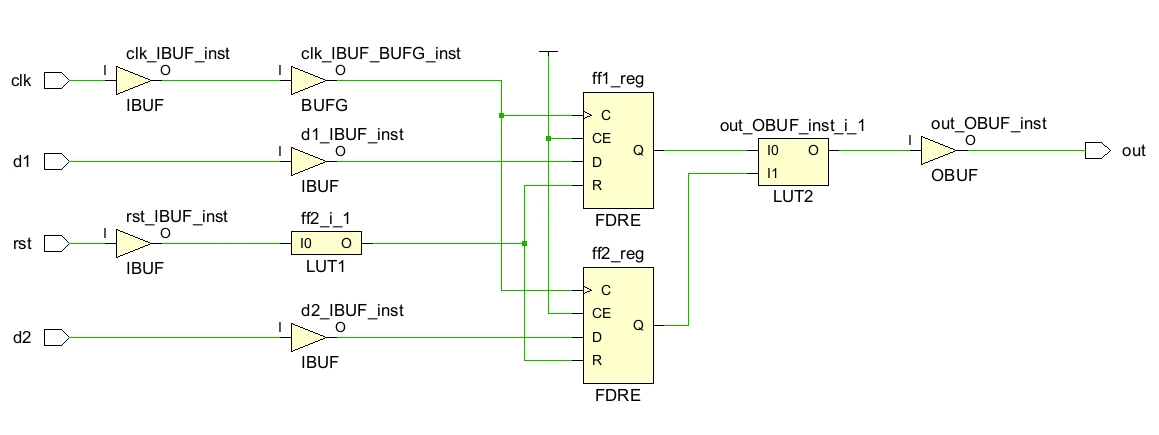

设计中以两个触发器输出到一个LUT2的两个输入引脚为例,对LUT2的两个输入引脚设置set_data_check约束检查

module set_data_check(d1,d2,clk,rst,out);

input d1,d2,clk,rst;

output out;

reg ff1,ff2;

always@(posedge clk)

begin

if(!rst)

ff1<=0;

else

ff1<=d1;

end

always@(posedge clk)

begin

if(!rst)

ff2<=0;

else

ff2<=d2;

end

assign out=ff1&ff2;

endmodule综合网表连接图如下图所示

3.2 约束设置

约束文件,set_data_check约束中setup,hold约束都设置了,即LUT2上I1端口的信号要早于I0信号至少0.3ns到达,并且在I0到达后至少要维持0.2ns。还需对out端口设置set_output_delay约束,否则无时序路径进行分析。

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

set_output_delay -clock [get_clocks *] 0.500 [get_ports -filter { NAME =~ "*" && DIRECTION == "OUT" }]

set_data_check -setup -from [get_pins out_OBUF_inst_i_1/I0] -to [get_pins out_OBUF_inst_i_1/I1] 0.300 -clock [get_clocks *]

set_data_check -hold -from [get_pins out_OBUF_inst_i_1/I0] -to [get_pins out_OBUF_inst_i_1/I1] 0.200 -clock [get_clocks *]3.3?时序报告

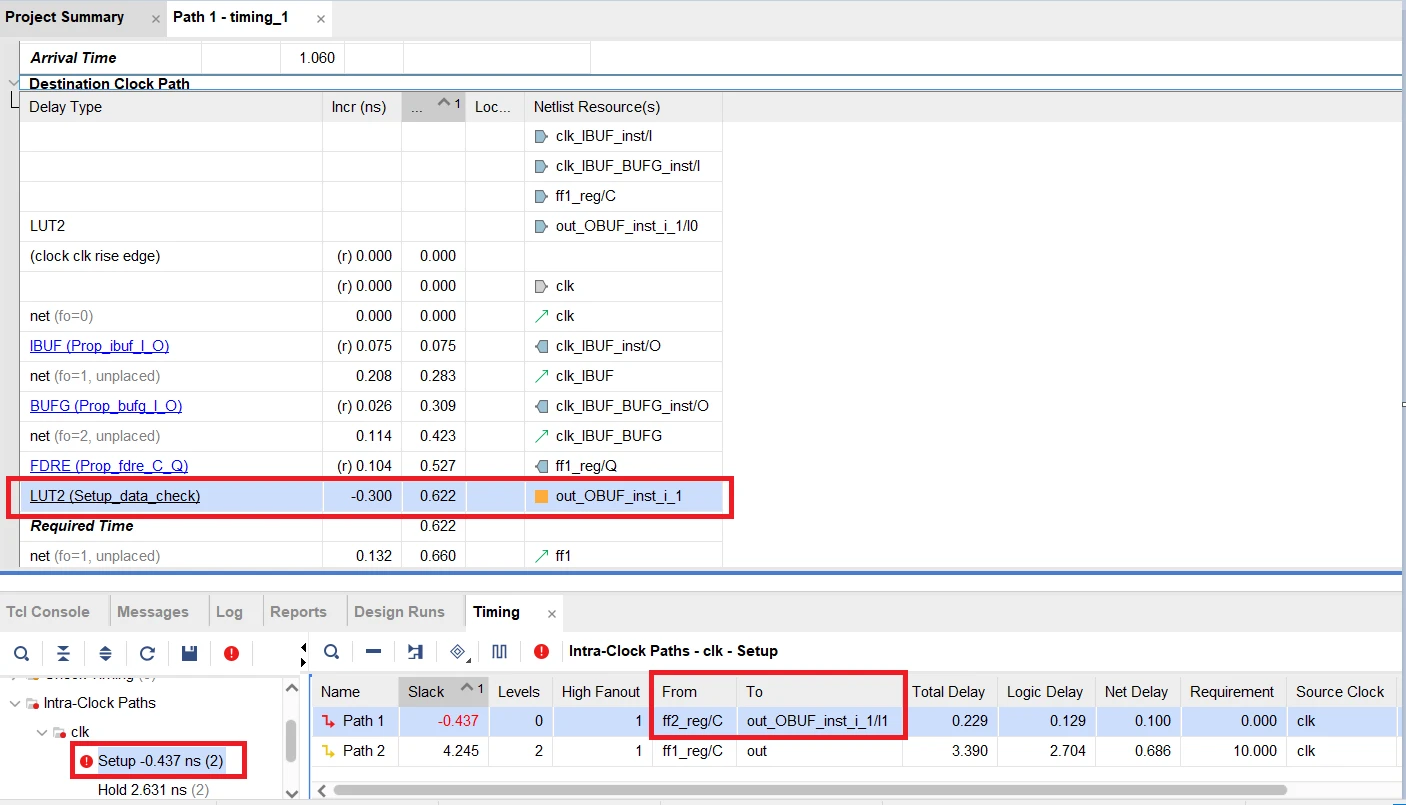

????时序报告结果中,setup中有一条ff2_reg/C到out_OBUF_inst_i_1/I1的路径,查看详细信息,可看到在目标时钟到达的路径上有一条LUT2标注有set_data_check的路径,时延值即为约束的0.3ns,-0.3即表示在原有基础上还需提前0.3ns到达。但此种条件会到导致setup违例0.437ns,说明该条目录上自身就存在0.137ns的违例。

?

????再看对应的hold检查,hold路径中多了一条ff2_reg/C到out_OBUF_inst_i_1/I1的路径,再看详细的路径时延,在目的时钟到达时延中,有一个LUT标注了hold_data_check,该路径时延值增加了0.2ns,即为约束set_data_check中hold的0.2ns,表示信号到达后时延值需再维持0.2ns

?

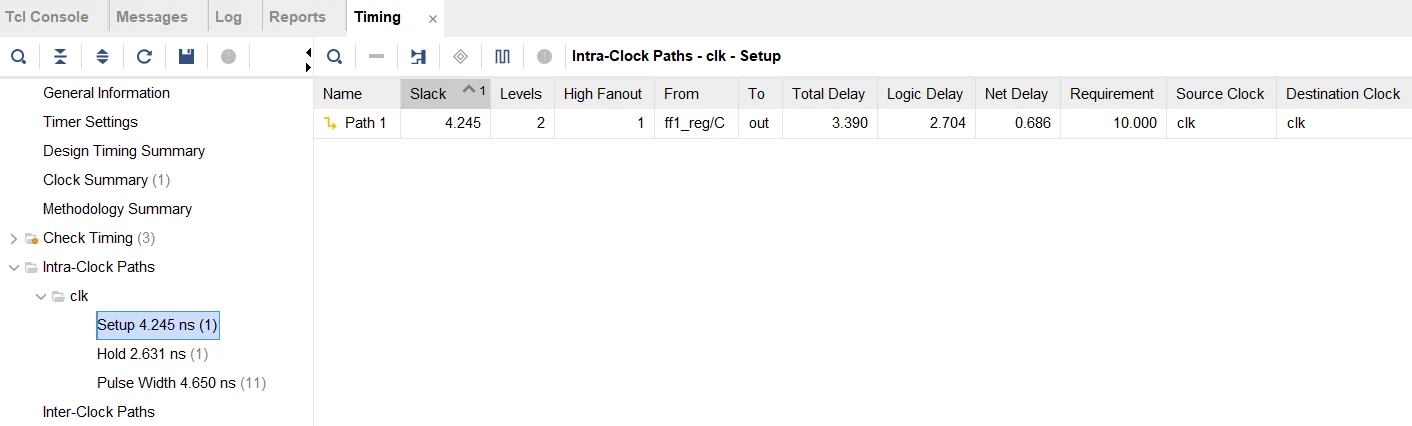

将set_data_check约束移除,时序报告中setup,hold都只有一条,符合预期

?

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt?

提取码:mylt? ?

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- SpringCloudAlibaba之Gateway

- SpringSecurity6 | 退出登录后的JSON处理

- 【ASP.NET Core 基础知识】--介绍

- 做私域社交电商,其店铺流量从何而来?

- 强化学习的数学原理学习笔记 - 策略梯度(Policy Gradient)

- 1.14和1.15

- 烟雾识别摄像机

- Python中真的没有switch语句吗

- Resnet结构的有效性解释

- 【AIGC】IP-Adapter:文本兼容图像提示适配器,用于文本到图像扩散模型